Запоминающее устройство с самоконтролем

Иллюстрации

Показать всеРеферат

О П И С А Н И Е ()934554

И306РЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Ресяублик (6t ) Дополнительное к авт. свнд-ву(22) Заявлено 29. 12. 80 (21) 3224959/18-24 (5t)A%. Кл. с присоединением заявки,%G I l С 29/00

G 11 С 11/22

)еаударстввииый комитет

СССР (23) Приоритет (53) УД К681. 327 (088.8) ио делам изобретеиий и открытий

Опубликовано 07.0б.82. Бюллетень pg 21

Дата опубликования описания 07.06,82 (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

С САМОКОНТРОЛЕМ

Изобретение относится к запоминающим устройствам и может быть использовано в вычислительной технике и автоматике, где требуется неразрушающее воспроизведение хранимой информации при ее сравнительно медленной смене.

Известно заминаюцее устройство (ЗУ), содержащее блок управления по адресу, матрицу, блок управления по разряду и блок усилителей считыва!

О ния. Устройство позволяет осуществлять электрическую перезапись информации, хранение ее при выключенном питании и считывание в прямом коде 1), тэ

Однако известное ЗУ .отличается большими аппаратурны ли затратами.

Наиболее близким к предлагаемому являетсл запоминающее устройство, содержащее блок управления по адресу, накопитель и блрк усилителей считывания, которое позволяет осуществлять неразрушающее считывание информации в прямом коде и длительное ее хранение с редкой сменой информации (2).

Недостатка ли указанного устройства являются отсутствие контроля считываемой информации и возможности считывания хранимой в накопителе информации в инверсном коде, что сни жает его надежность.

Цель изобретения - повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее накопитель на сегнетоэлектрических элементах памяти, адресные шины которого соединены с выходами блока управления, экранирующие шины - с шиной нулевого потенциала, а разрядные шины подключены ко входам усилителей считывания, выходы которых соединены со входами регистра числа, введены триггеры по числу разрядов накопителя, элемент

ИЛИ я коммутаторы, причем входы первого коммутатора и элемента ИЛИ обье34554

3 9 динены и являются стробирующими входами устройства, выход первого коммутора соединен с управляющим входом регистра числа, выход элемента

ИЛИ подключен к управляющим входам триггеров, счетные входы которых соединены с выходами усилителей считывания, выходы — с информационными входами второго коммутатора, выходы которого являются одними из выходов устройства, установочные входы триггеров и второго коммутатора соединены и являются одним из управляющих входов устройства.

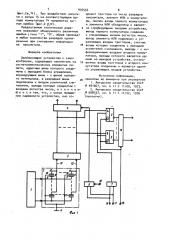

На фиг.! представлена структурная схема запоминающего устройства с са моконтролем, на фиг.2 - временные диаграммы работы устройства.

Запоминающее устройство с самоконтролем содержит блок 1 управления, накопитель 2 на сегнетоэлектрических элементах памяти, усилители 3 считывания, регистр 4,числа, триггеры 5, первый коммутатор 6, элемент ИЛИ

Накопитель 2 содержит сегнетоэлектрические элементы 8 памяти на основе широкополосных пьезотрансформаторов, например интегральные пьезокерамические микросхемы 307PBI.

Входные электроды 9 элементов 8 памяти объединены в адресные шины и .соединены с выходами блока 1 управления.

Экранирующие электроды 10 всех элементов 8 памяти соединены между собой, объединены в экранирующие шины и подключены к шине 11 нулевого потенциала. Выходные электроды

12 элементов 8 памяти объединены в разрядные шины .13 и подключены к усилителям 3 считывания. Устройство содержит также второй коммутатор

14, входы 15-18.

Запоминающее устройство с самоконтролем имеет три режима работы: ! записи, хранения и считывания информации.

Запись информации в устройство заключается в установке соответствующих направлений остаточной поляризации участков сегнетоэлектрической пьезокерамической пластины (weментов 8 памяти), расположенных между выбранными входными электродами 9 и экранирующими электродами 10, путем воздействия на .них электрического полл. В процессе записи информации накопитель 2 вынимают из запоминающего устройства и подключают к автономному блоку запи" си (не показан). Блок записи вырабатывает напряжение поляризации, которое подается на входные 9 и экранируюцие 10 электроды накопителя в соответствии с записываемой информацией. Под действием электрического

10 поля, созданного между входными 9 и экранирующими 10 электродами, происходит поляризация пластины в направлении, соответствующем направлению электрического поля. После записи накопитель 2 возвращают в запоминающее устройство.

В режиме хранения информации накопитель не потребляет эпектрической энергии, и сохранность записан20 ной в нем информации практически не зависит от времени и наличия питания.

В режиме считывания запоминающее устройство допускает выборку храни25 м ой информации с произвольным доступом к адресным шинам накопителя 2.

Считанная из накопителя 2 информация может быть представлена в регистре

4 в прямом или инверсном коде. зо На блок 1 управления подается код адреса, из которого необходимо считать требуемое слово. Блок 1 вырабатывает импульс напряжения считывания (фиг.2а), который поступает на требуемый вход накопителя 2 и прикладывается к входным 9 и экранирующим 10 электродам элементов 8 памяти (выбранного слова). Пьезокерамическая пластина, находящаяся

1О между этими электродами, деформируется вследствие явления обратного пьезоэлектрического эффекта.

Из-за наличия механической связи деформируется и пьезоэлектрическая пластина, находящаяся между экранирующим 10 и выходным 12 электродами. Вследствие явления прямого пьезокерамического эффекта на выходном электроде 12 каждого элемента 8

50 памяти относительно экранирующего электрода !0 появляется информационный импульсный сигн л в виде свободных электрических зарядов.

В силу линейности пьезоэлектрического эффекта направление деформации возбуждаемой пластины, а следовательно, и знак свободных электрических зарядов на выходном элект-, 5 9345 троде 12 каждого элемента 8 памяти (выбранного слова ) однозначно зависит от направления остаточной поляризации пьезокерамической пластины, находящейся между входным 9 и экра" нирующим 10 электродами, которое в свою очередь определено двоичной информацией, записанной в накопитель

2. Форма выходного сигнала, соответствующая логической "1" и логическому "0", имеет вид, представленный на фиг.2б (1 и II соответственно), причем амплитуды первой и второй полуволн приблизительно одинаковы.

Информационные сигналы с выходов !5 элементов 8 памяти (выбранного слова) поступают на усилители 3 считывания.

С выходов усилителей 3 информация (фиг.2e,!, И ) поступает на входы регистра 4 и триггеров 5. Если счи- 2о тываемую из накопителя 2 информацию необходимо представить в прямом коде то на управляющий вход регистра числа через коммутатор 6 подается стробирующий импульс (фиг.2r) с входа 25

16 устройства. В том случае, если информацию необходимо представить в инверсном коде, с входа 18 устройства на управляющий вход коммутатора 6 подается сигнал, по которому 5В коммутатор 6 пропускает на управляющий вход регистра 4 стробирующий импульс с входа 17 (фиг.2д), и в регистр 4 записывается слово в инверсном коде.

Информация с выходов усилителей

3 считывания поступает на регистр

4 и одновременно для контроля подается на входы триггеров 5. На управляющие входы триггеров 5 через элемент ИЛИ 7 поступают стробирую-. щие импульсы (фиг.2г,д) с входов

16 и 17 запоминающего устройства.

Триггеры 5 находятся в исходном состоянии, т.е. на инвертирующих выходах присутствует логическая "1".

На выходах коммутатора 14 отсутствует информация о состоянии триггеров 5, так как на входе 15 устройства присутствует низкий уровень напряжения.

На входах триггеров 5 может присутствовать как полезная информация (фиг,2в, 1,0), так и. отказы типа логическая "1" (фиг.2в, П() или логический "0" (фиг.2e,Iy ), 55

При поступлении на один из входов триггера 5 полезной информации, соответствующей "!", на другой вход

54 .6 поступает стробирующий импульс (фиг.2г,1) с входа 1б, и триггер

5 перебрасывается, т.е. на инверсном выходе появляется логический "0".

Второй стробирующий импульс (фиг.2д,I) поступающий на триггер 5 с входа

17, не меняет состояния триггера

5, так как на счетном входе в этот момент присутствует "0". Потом на установочные входы триггеров 5 и коммутатора 14 подается импульс (фиг.2е,1), который пропускает информацию с выходов триггеров 5 на их выходы. Иа выходах триггеров 5 сигнал отказа отсутствует (отказ соответствует логической "1"). .По заднему фронту импульса установки в "0" (фиг.2е,I), поступившего с входа 15, триггеры 5 возвращаются в исходное состояние, т.е. на инверсных выходах появляется "1".

При поступлении на вход триггера 5 полезной информации, соответствующей "0", первый стробирующий импульс с входа 16 не перебрасывает триггер 5, так как в этот момент времени отсутствует сигнал "1" на счетном входе триггера 5. Второй стробирующий импульс с входа 17 совпадает по времени с сигналом нуля и перебрасывает триггер 5, т.е. на инверсном выходе триггера 5 появляется "0", Импульс сброса с входа

15 осуществляет операции аналогично описанным выше при поступлении на вход триггеров 5 информации, сост" ветствующей "1".

При отказе одного из разрядов устройства типа логическая "1" (фиr.2б,в,10) триггер 5 перебрасывается дважды: в момент действия первого стробирующего импульса и второго, т.е. на выходе триггера 5 .устанавливается "1" (фиг.2ж, 10). Импульс, (фиг.2е, III) с входа 15 разрешает прохождение. информации с выходов триггеров 5 через коммутатор 14 на выходы устройства. На выходе, соответствующем отказавшему разряду, появляется сигнал отказа "1" (фиг.2э,1Ц), При отказе одного из разрядов устройства типа логический "0" соответствующий триггер 5 не изменяет своего исходного состояния (фиг.2ж,IV) при воздействии стробирующих импульсов с входов 16 и 17, так как на одном из информационных входов тригге" ра 5 присутствУет нулевой сигнал

934554

Формула изобретения (фи г. 2в, 1М ) . При воздействии импул ьса с входа 15 на соответствующем выходе коммутатора 14 появляется сигнал ошибки (фиг.2 P;1V).

Предлагаемое техническое реше ние позволяет обнаруживать различные ошибки (типа "1", "0", обрыв провода) в любом количестве разрядов одновременно при считывании информации из накопителя.

Запоминающее устройство с самоконтролем, содержащее накопитель на сегнетоэлектрических элементах памяти, адресные шины которого соединены с выходами блока управления, экранирующие шины - с шиной нулевого потенциала, а разрядные шины го подключены к входам усилителей считывания, выходы которых соединены с входами регистра числа, о т л и ч а ю4 е е с я тем, что, с целью повышения надежности устройства, оно со1

1 держит триггеры по числу разрядов накопителя, элемент ИЛИ и коммутаторы, причем входы первого коммутатора и элемента ИЛИ обьединены и являются стробирующими входами устройства, выход первого коммутатора соединен с управляющим входом регистра числа, выход элемента ИЛИ подключен к уп- равляющим входам триггеров, счетные входы которых соединены с выходами усилителей считывания, выходы - с информационными входами второго коммуматора, выходы. которого являются од" ними из выходов устройства, установочные входы триггеров и второго коммутатора соединены и являются одним из управляющих входов устройства.

Источники информации,,принятые во внимание при экспертизе

1. Авторское свидетельство СССР и 481067, кл. G 11 С 11/00, 1973.

2. Авторское свидетельство СССР ,N 6081Я7. кл. G 11 С 11/22, 1976 (прототип), 934554

Составитель 8.Рудаков

Техред T. Маточка Корректор И.Иуска

Редактор И.Михеева

Филиап ППП "Патент", г.Ужгород, ул.Проектная,4

Заказ 3949/49 Тираж 622 Подписное

8НИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.:, д.4/5