Устройство для контроля частоты

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик о11935805 (61) Дополнительное к авт. свид-sy (22) Заявлено 03. 10. 80 (2! ) 2990376/18-21 с присоединением заявки ¹

Р1 М К з

G 01 R 23/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет г

Опубликовано 15.06.82, Бюллетень ¹ 22 (53) УДК 621.317 (088. 8) Дата опубликования описания 15. 06. 82 (72) Авторы изобретения

В.Л. Грузов, A.Ñ. Завьялов и В.П. Калявин (71) Заявитель

Вологодский политехнический институт (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЧАСТО Щ

Изобретение относится к электротехническим измерениям и может использоваться для контроля частоты.

Известно устройство для допустимого контроля, содержащее два импульсных генератора с комбинированными длитепьностями импульсов, триггеры, логические элементы flj .

Однако известное устройство недостаточно информативно.

Известно устройство для контроля частоты, содержацее три триггера, дешифратор, счетчики и группу логических элементов (2).

Известное устройство достаточно слржно.

Цель изобретения — упроцение устройства.

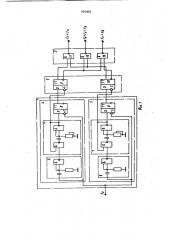

Поставленная цель достигается тем, что в устройстве, содержащем блок сравнения, выходы которого соединены со входами двух триггеров блока памяти, выходы которых соединены с входами элемента совпадения, блок сравнения выполнен в виде двух пороговых датчиков частоты, состоящих из последовательно соединенных дифференцирующей цепочки, одновибратора и D-триггера, причем общий вход устройства соединен с входами синхронизации Dтриггеров датчиков блока сравнения и через дифференцируюцие цепочки с входами одновибраторов датчиков блока сравнения, при этом входы синхронизации D триггеров блока памяти соединены с выходами одновибраторов датчиков блока сравнения.

На фиг.1 приведена принципиальная схема предлагаемого устройства; на фиг.2 — временная диаграмма, поясняющая работу устройства.

Устройство содержит блок 1 сравнения, блок 2 памяти и элемент 3 совпадения. Блок 1 сравнения состоит

15 из двух пороговых датчиков 4 и 5 частоты, каждый из которых имеет дифференцирующую цепочку 6, на вход которой поступает контролируемый сигнал частоты Рх, одновибратор 7, запускаемый сигналом дифференцирующей цепочки, и D--триггер 8. Блок 2 памяти содержит два Э-триггера 9 н

10, в элемент 3 совпадения входят три ячейки 11, 12 и 13 И (И-HE).

25 Устройство работает следующим образом.

Одновибратор 7 датчика 4 имеет длительность импульса, равную 1/Ги .

Одновибратор 7 датчика 5 настроен

30 на длительность импульса, равную

935805

1/Fg, где F — частота, -соответствующая нижней границе допуска, à F< соответствует наибольшей допустимой частоте. Если Р,(F„, то одновибратор 7 запускается (фиг.25) каждым перепадом 0- 1 входного сигнала частоты F (фиг.2а), как, например, в моменты времени t и t<. При этом триггер 8 остается в состоянии. 1 (фиг. 2в),так как к моменту прихода перепада 0- 1 на вход С на входе 10

D уже успевает установиться сигнал логической 1 . Как только Р„ станет больше F очередной перепад 0- 1 в момент t переведет триггер 8 в состояние 0 (фиг.2в), 15 так как одновибратор 7, запустившись в момент.t держит на входе

0-триггера логический 0 при поступлении сигнала синхронизации. В дальнейшем состояние триггера 8 может20 меняться, но поскольку его сигнал подается на вход D-триггера 9 блока

2 памяти, а сигнал синхронизации на триггер 9 поступает с выхода одно-вибратора 7, то, перейдя в момент

С4 в состояние 0, триггер 9 (фиг.2г) в этом состоянии и остается, поскольку в моменты подачи перепада 0- 1 на вход С (моменты t, 1: и т..д.) триггер 8 находится в состоянии 0 . Если

Fg станет меньше F„, то триггер 8, а за ним и 9 перейдет опять в состояние 1 .

Ланалогично работает датчик 5 частоты (фиг.2 д,е,ж) и триггер 10 блока памяти. При ступенчатом изменении частоты F< (фиг.2а) триггер

10 перейдет в состояние 0 при

F<> Р8 (момент t7) .

Ячейки 11, 12, -.:13 И-НЕ элемента 40

3 совпадения формируют по состояниям триггеров . блока 2 памяти на своих выходах сигналы, соответствующие трем возможным результатам к и роля, появляющиес а виде логи- 45 ческого нуля: Р сР (фиг.2 и);

F„(F„cРВ (Фиг ° 2 к); FR F5 (фиг ° 2 л) °

Точность отработки частот F„ и

Fg зависит от точности установки и стабильности импульсов одновибраторов и может быть легко, повышена применением более качественных одновибраторов, построенных, например, на операционных усилителях.

Таким образом, предлагаемое устройство выполняет контроль частоты

F сигнализируя о нахождении ее в пределах допуска и выхода ее за пределы допуска: сигналы Р„ Р„ Fx>FB °

Устройство обладает высоким быстродействием ч имеет простую схемную реализацию.

Формула изобретения

Устройство для контроля частоты, содержащее блок сравнения, выходы которого соединены с входами двух триггеров блока памяти, выходы ко- . торых соединены с входами элемента совпадения, о т л и ч а ю щ е е с я тем, что, с целью упрощения устройства, блок сравнения выполнен в виде двух пороговых датчиков частоты, состоящих из последовательно соединенных дифференцирующей цепочки, одновибратора и D-триггера, причем общий вход устройства соединен с входами синхронизации D-триг-. геров датчиков блока сравнения и через дифференцирующие цепочки с входами одновибраторов датчиков блока сравнения, при этом входы синхронизации D триггеров блока памяти соединены с выходами одновибраторов датчиков блока сравнения;

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 613263 ° G Ol R 23/00с 1979 °

2. Авторское свидетельство СССР

9 468178, 6 01 R 23/02, 1974.

935805 составитель B.Новоселов

Техред А. Бабинец Корректор В. Бутяга

Редактор М.Петрова

Заказ 4200/45 Тираж 717 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Z(-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4