Устройство измерения параметров сигналов

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

<>935810

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 13. 10. 80 (21) 2992365/18-21 И1М.К . с присоединением заявки ¹

G 01 R 23/02

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет (33) УДК 621. 317. .3(088.81

Опубликовано 15.06.82. Бюллетень ¹ 22

Дата опубликования описания 15. 06. 82

Г.Д.Козлов, А.В.Поляков и В.П.Соколов (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ИЗМЕРЕНИИ ПАРАМЕТРОВ

СИГНАЛОВ

Изобретение относится к радиоизмерениям.

Известно устройство для измерения параметров сигналов, содержащее датчик событий, ждущие мультивибраторы, генератор с программируемой частотой, коммутатор, кварцевый генератор, счетчик времени, выходной счетчик, блоки памяти, сравнивающее устройство, преобразователь, декадное времязадающее устройство, запускающий блок (17.

Однако данное устройство не обеспечивает достаточной точности.

Наиболее близким по технической сущности к изобретению является устройство, содержащее преобразователь частоты, выход которого соединен с п каналами, каждый из которых содержит m параллельно соединенных подканалов, включающий последовательно соединенные полосовой Фильтр и детектор огибающей, первый и второй выходы блока фазовой автоподстройки частоты каждого из и каналов через управляющий коммутатор соединены со входами счетчиков частоты

Доплера, третий выход блока фаэовой автоподстройки частоты каждого из и каналов через управляющий коммутатор соединен со входом блоков синхронизации и первым входом интеграторов, второй вход которых соединен с выходом соответствующего блока синхронизации, выход интегратора соединен с решающим устройством (27.

Однако это устройство характеризуется недостаточной достоверностью и относительно большой длительностью цикла обнаружения.

Целью изобретения является повышение достоверности результатов измерений.

Поставленная цель достигается тем, что в устройство, содержащее m каналов обнаружения, каждый из которых состоит иэ и каналов частотной селекции, вклюЧающих последовательно соединенные полосовой фильтр и детектор, и блока фаэовой автоподстройки частоты, смеситель, вход которого соединен с входной шиной, а выход — с входами полосовых фильтров всех и каналов частотной селек25 ции, коммутатор, вход которого соединен с выходами блоков Фаэовой автоподстройки частоты всех m каналов обнаружения, а соответствующие выходы коммутатора подключены к

30 двум входам каждого иэ двух счетчи935810 нов доплеронской частоты и входам двух блоков обработки, каждый из которых состоит иэ последователЬно включенных синхронизатора, интегратора, второй вход которого соединен с входом синхронизатора, и решаюцего блока, в каждый из m каналов обнаружения введены формирователь сигналов .сравнения и включенные последо вательно канальный коммутатор, формирователь кода, преобразователь коднапряжение и блок дискретной под стройки частоты, выход которого подключен к входу блока фазовой автоподстройки частоты, а в каждый из п каналов частотной селекции введен блок сравнения, один вход которого соединен с выходом детектора, а другой вход подключен к выходу формирователя сигналов сравнения данного канала обнаружения, причем входы каждого канального коммутатора соединены с выходами блоков сравнения данного канала обнаружения, второй выход канального коммутатора соединен с входом формирователя сигналов сравнения, а вторые входы всех блоков дискретной подстройки частоты соединены с выходом смесителя.

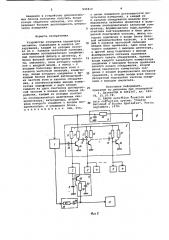

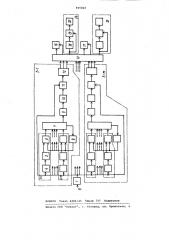

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Устройство содержит пресбраззватель 1 частоты, каналы 2-1,...,2-m об. аружеыия, каждый иэ которых вклю-. чает каналы 3-1,...,3-п частотной селекции, в состав которых входят полосовой фильтр 4, детектор 5 и блок 6 сравнения, канальный коммута-.ор ". Формирователь 8 сигналов сраныенья, формирователь 9 кода, преобраэова:ель 10 код-напряжение, блок 11 дискретной подстройки часто ты, блок 12 фаэоной антоподстройеи частоты.

В состав устройства также входят коммутатор 13, блоки 14 и 15 обработки, счетчики 16 н 17 доплеронской частоты. В состав пока обработки входят синхронизатор 18, интегратор 19 и решающий блок 20. Входной сигнал подан на входную шину 21.

Устройство работает следуюцим образом.

Hà нход преобразонателя 1 поступает один или одновременно. несколько сигналов, отличающихся по частоте, которые необходимо обнаружить и параметры которых требуется измерить.„В преобразователе 1 частоты происходит понижение частоты нходного сигнала. С выхода преобразователя частоты сигналы одновременно поступают ыа входы полосовых фильтров

2-m и на входы смесителей частот (не показаны), ыаходяцихся в блоках 11 дискретной подстройки частоты. Совокупность полосовых фильтров перекрывает весь диапазон ноэможных изменений частот приходящих сигналов, и сигналы проходят через те Фильтры, н полосах пропускания которых находятся их частоты. С выходов полосовых фильтров сигналы поступают на входы детекторов огибающих 5, где выделяются постоянные составляющие сигналов, которые поступают на первые входы блоков 6 соответствующих подканалон.

С выходов Формирователей 8 на вторые входы блокон 6 одновременно подаются сигналы сравнения, уронни

l5 которых меняются но времени. Как только уровни постоянных составляющих поступаюцих сигналов превысят уровни сигналов сравнения, на выходах соответствуюцих блоков сравщ нения появляются сигналы, которые поступают на коммутаторы 7. Коммутаторы останавливают работу Формирователей 8 и н То же время подклю чают к формирователям 9 тот подкаыал, в полосе пропускания фильтра которого находится частота входного сигнала. Формирователи кодов подканалон вырабатывают коды, соответствуюцие номерам подканалов, и эти коды поступают на преобразователи кодыапряжение. В преобразователях коднапряжение коды подкаыалов преобразуются н напряжения„ которые подстраивают упранляемые генератора {не показаны), находящиеся в блоках дискретной подстройки частоты кажl,IIoão иэ N каналов таким образом, что частоты сигналов, параметры которых нес бходимо измерить, после преобразования оказываются в полосах

"О захвата блоков 12 Фаэовой антоподстройки частоты.

Происходит синхронизация частот управляемых генераторов (не показаны) систем Фазоной автоподстройки частоты с частотами приходящих сигыалон, детектирование символов информации и выделение несуцих частот, имеющих доплеровское смещение. ОдHoBpBMQBHo ыа выходах блоков Фазо5О ной антоподстройки частоты вырабатыв отся сигналы, показывающие, что системы фазовой автоподстройкн час-.aты находятся в состоянии синхроыизма. г

По этим сигналам комм татор 13 производит подключение одного иэ блоков Фаэоной автоподстройки частоты к свободному счетчику 16,17,где производится измерение доплеронского смещения частоты, и к снободному блок;. обработки информации, состояцему из синхронизатора 18, интегратора 19 и решаюцего блока 20, в которых происходит выделение символов

65 информации.

935810

Введение в устройство дополнитепьных блоков позволяет получить более точную обработку сигналов, что обеспечивает большую достоверность резуль-, татов измерения.

Формула изобретения

Устройство измерения параметров сигналов, содержащее m каналов обнаружения, каждый из которых состоит иэ п каналов частотной селекции, включающих последовательно соединенные полосовой фильтр и детектор, и блока фазовой автоподстройки часто- !5 ты, смеситель, вход которого соединен с входной шиной, а выход — с входами полосовых фильтров всех и каналов частотной селекции, коммутатор, входы которого соединены с выходами блоков фазовой автоподстройки частоты всех m каналов обнаружения, а соответствующие выходы коммутатора подкачены к двум входам каждого из двух счетчиков доплеровс кой частоты и входам двух блоков обработки, каждый из которых состоит из последовательно включенных син- хронизатора, интегратора, второй вход которого соединен с входом син.хронизатора, и решающего блока, о т л и ч а ю щ е е.с я тем, что, с целью повышения достоверности результатов измерений, в каждый иэ

m каналов обнаружения введены формирователь сигналов сравнения и включенные последовательно канальный коммутатор, формирователь кода, преобразователь код-напряжение и блок диск ретной подстройки частоты, выход ко- . торого подключен к входу блока фаэовой автоподстройки частоты, а в каждый и каналов частотной селекции введен блок сравнения, один вход которого соединен с выходом детектора, а другой вход подключен к выходу формирователя сигналов сравнения данного канала обнаружения, причем входы каждого канального коммутатора соединены с выходами блоков сравнения данного канала обнаружения, второй выход канального коммутатора соединен с входом формирователя сигналов сравнения, а вторые входы всех блоков дискретной подстройки частоты соединены с выходом смесителя.

Источники информации, принятые во.внимание при экспертизе

1. ПатентСША 9 3842347, кл. 32478, 15.10.74.

2 ° ARGOS sate 08ite 8ocation and

date coHect1on system. "Centre

Nationag d Etudes Spat1a6es", Paris, september, 1978.