Фазосдвигающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистических

Республик

< 335819 (61) Дополнительное к авт. свид-ву (22) Заявлено 22 ° 08. 80(21) 2995520/18-21

Р1 М g> з

G 01 R 25/04 с присоединением заявки ¹ (23) Приоритет

Государственный комитет

СССР ио делам изобретений и открытий (ЗЗ) УДК 621. 317..77(088.8) Опубликовано 1506.82. Бюллетень ¹22

Дата опубликования описания 15. 06. 82 (72) Авторы изобретения

Б. К. Куприн, A. И. Днойниченко и В

;е

}

t ( (71) Заявитель (54) ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к фазосдвигающим устройствам, в которых изменение фазового сдвига и частоты сигналов зависит от внешних управляющих сигналов, и, н частности, может быть использовано при проверке измерителей моментов.

Известен фазовращатель, содержащий управляемий генератор с устройствами частотной и фаэоной подстройки частоты, выход которого подключен к двум идентичным пересчетным блоком, а также блок записи кода, две группы вентилей, блок аналоговой памяти и фильтр нижних частот (1).

Это устройство обладает сложной схемой и формирует сигналы со сдвигом фазы от 0 до 360

Наиболее близким к предлагаемому является устройство, содержащее блок задержки, выходной триггер и элемент совпадения р2)

Изменение фазового сдвига возможно a,èíòåðâàëå от 0 до 360о. Известное устройстно не обеспечивает непрерывного изменения фазы н диапазоне (-180o) (+180o)

Цель изобретения — расширение функциональных возможностей.

Указанная цель достигается тем, что н фазосднигающее устройство, содержащее дна триггера, блок задержки, выход которого соединен .-о вторым входом нторого триггера, и первый элемент совпадения, введены два сумматора, два дополнительных блока задержки, второй элемент ".îâïàäåíèÿ, два.формирователя и источник постоянного напряжения, выход которого соединен со вторым входом первого дополнительного блока задержки и первыми входами сумматороь одновременно, а вторые входы последних янляются входами устройотна, причем выход первого сумматора подсоединен к первым входам всех блоков задержки, а выход второго сумматора

20 ко вторым входам блока задержки и второго дополнительного блока задержки, при этом выход второго дополнительного блока задержки соединен с первым входом второго триггер»,. выход которого через второй форт.—

25 рователь подключен ко второму выходу устррйстна, причем выход дополнительного блока задержки соединен одновременно с его входом управления и первыми входами элементов совпадения, вто30 рые входы которых подсоединены к ныхо935819 дам первого триггера, первый выход которого соединен через первый формирователь с первым выходом устройства, кроме того выходы первого и второго элементов совпадения подсоединены ко входам управления блока задерж- ки и второго дополнительного блока задержки соответственно.

При этом блок задержки состоит из интегратора, вход которого является первым входом блока, а выход соединен10 с первым входом компаратора, второй вход которого является вторым входом блока, а выход компаратора через .формирователь соединен с выходом блока, причем вход управления интегратора HH-;I} 5 ляется входом управления. блока задержки.

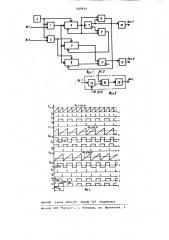

На фиг.1 приведена структурная схе.ма устройства; на фиг.2 — структур-! ная схема блока задержки; на фиг.3эпюры сигналов на выходах узлов устройства.

Фазосдвигакщее устройство содержит первый и второй сумматоры 1 и. 2, источник 3 постоянного напряжения, первый и второй дополнительные блоки 4 и 5 задержки, .блок 6 задержки, первый триггер 7, первый и второй элементы 8 и 9:-. совпадения, первый формирователь 10, второй триггер 11 и второй формирователь 12.

Блоки 4, 5 и 6 задержки содержат интегратор 13, компаратор 14 и формирователь 15.

Устройство работает следуюцим образом.

Фазовые датчики измерения крутящих моментов вырабатывают два сигнала где (в -- круговая частота напряжения питания датчиков;

Я. — круговая частота врацения роторов датчиков;

Ч() - угол сдвига фазы, пропор- 4 циональный крутящему моменту.

Фазосдвигаюцее устройство должно вырабатывать сигналы, подобные сигналам (1) . 50

На первый вход устройства (Вх.1) подается напряжение, задающее величину Р, а на второй вход (Вх.2) задающее величину Ч . Напряжение на входах устройства могут быть описаны 55 выражениями Ьх < о1 = o ""F

B Ì .rj 02, (2) 6Î где Р - частота вращения ротора датчика;

8 масштабный коэФфициент, см

В. с рад

- угол сдвига фазы;

8 — масштабный коэффициент, В рад

Источник 3 вырабатывает постоянное напряжение О, сигнал на выходе первого сумматора 1 описывается выражением

О1 к, 106мл+ (q и )В=к,(„4 сиЯ Г+К где К; К„- коэффициенты передачи сумматора 1 по первому и второму входам соответственно.

Напряжение U< подается на Вх.1 блока 4 задержки и,интегрируется интегратором 13 этого узла. Сигнал на его выходе (ъ-4 (ъ-4 184 о (4) где 9 - время интегрирования, отсчитанное относительно момента сброса.

Напряжение Ъ 4 нарастает. Пока не изменяется полярность напряжения на выходе компаратора 14 блока 4.

При изменении напряжения на выходе компаратора 14 срабатывает формирователь .15, вырабатывающий короткий импульс (U4 фиг.3). Этим импульсом сбрасывается в ноль интегратор 13 блока 4 (компаратор 14 возвращается в исходное состояние), изменяется состояние первого триггера 7. Этот процесс повторяется циклически.

Изменение состояния первого триггера 7 происходит в моменты, когда выполняется условие

" -Ф "" " g. (5) (а)=к О где К ;К - коэффициенты (4-М- 4- "а передачи компаратора 14 . блока 4 по первому и второму входам соответственно.

При выполнении условия

@- М- -1 1 1 О1

I И-4- 2.

44-4- 1 "13-4 " - Ы4 ® 14-i-y Ug период повторения сигналов первого триггера 7 равен

27 (6)

7 у+Я а круговая частота

935819 т.е. круговая частота триггера 7 равна круговой частоте сигнала сигн. л дп я получен и я выходн о ro си гн ал а синусоидальной формы, в качестве формирователей 10 и 12 используются филь-5 тры. В этом случае на первом выходе устройства (Вых.l) имеем

11в „„— -Е sin ((u ) t.j . (7)

На выходах-элементов 8 и 9 совпадения получаем последовательности 10 коротких импульсов с частотой следования Ю и сдвинутых между собой на время 0,5 Т7. Импульсы U ; Ug сбрасывают в ноль интеграторы 13 блоков 5 и 6 соответственно. 15

Сигнал на выходе второго сумматора 2 описывается выражением

О =К 1ощ " К )3 = КУ j egg<+ т j. () g (f) г где К у К вЂ” коэффициенты пере 20 дачи сумматора 2 по первому и второ.му входам соответственно.

Интеграторы 13 блоков 5 и 6 ин- 25 тегрируют напряжение Пл . Компараторы 14 изменяют полярность выходного сигнала при изменении знака разности напряжений U< и U . Формирователи

l5 вырабатывают короткие импульсы в момент положительных (для рассматриваемого случая эпюр сигналов, фиг.2) перепадов напряжения на выходах компараторов 15. Эти импульсы (Q, U ) изменяют состояние триггера ll, сигнал которого, пройдя через формирователь 12, поступает на выход 2 устройства.

Если сигнал на выходе 1 устройства постоянен, то частота сигналов триггера ll равна частоте Ы7, а сигналы сдвинуты по фазе на величину, пропорциональнуЮ сигналу, заданному пр входу 2 устройства, при этом момент 9 и 8 появления импульсов

Пь и U<, отсчитанный от момента-сбро-4э са интегратора 13 блока б определяется выражением

Ф+ 7с

9 -9 = 9 ° (9)

Импульс U появляется в момент .времени 0,5 T, а оканчивается в мо7 мент времени Т . Импульс U появляется в момент времени О, а оканчивается в моМент времени (0,5 .T +G ).

При этом частота повторения обоих сигналов одинакова.

Положительный эффект заключается в расширении функциональных возможностей при упрощенном процессе регулирования,достигаемом за счет того, что процессы регулирования происходят под воздействием внешних аналоговых напряжений, причем раздельно регулируется частота и фаза сигналов и диапазон изменения фазы 180 -0 -180

Формула изобретения

1. Фазосдвигающее устройство, содержащее два триггера, блок задержки, выход которого соединен с вторым входом второго триггера, и первый элемент совпадения, о т л и— ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей, в него введены два сумматора, два дополнительных блока задержки, второй элемент совпадения, два формирователя и источник постоянного напряжения, выход которо-. го соединен с вторым входом первого дополнительного блока задержки и первыми входами сумматоров одновременно, а вторые входы последних являются входами устройства, причем выход первого сумматора подсоединен к первым входам всех блоков задержки, а выход второго сумматора - к вторым входам блока задержки и второго дополнительного блока задержки, при этом выход второго дополнительного блока задержки соединен с первым входом второго триггера, выход которого иерез формирователь подключен к второму выходу устройства, причем выход дополнительного блока задержки соединен одновременно с его входом управления и первыми входами элементов совпадения, вторые входы которых подсоединены к выходам первого триггера, первый выход которого соединен через первый формирователь с первым выходом устройства, кроме того выходы первого и второго элементов совпадения подсоединены к входам управления блока задержки и второго дополнительного блока задержки соответственно.

2. Устройство по п.l, о т л ич а ю щ е е с я тем, что блок задержки состоит из интегратора, вход которого является первым входом блока, а выход соединен с первым входом коипаратора, второй вход которого является вторым входом блока, а выход компаратора через формирователь соединен с выходом блока, причем вход управления интегратора является входом управления блока задержки.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 492825, кл. G R 25/04, 1972.

2. Авторское свидетельство СССР

Р 373644, кл. 6 01 и 25/04, 1971.