Импульсный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

В.Ф. Кукушкин, В.А. Гречихин и Т.И. Крутова (72) Авторы изобретения (73) Заявитель (54) ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО

НАПРЯЖЕНИЯ тель (1).

Изобретение относится ко вторич- ., ным источникам электропитания на полупроводниковых приборах и может быть использовано в радиотехнике, автомати ке и вычислительной технике.

Известен импульсный стабилизатор постоянного напряжения, содержащий последовательный LDC-фильтр, ключевой регулятор, управляемый транзисторный мультивибратор с балансным транзисторным усилителем, эмиттерный повторитель и импульсный усилиОднако это устройство имеет низкий КПД и сложную схему узла регулирования частоты переключения ключевого регулятора.

Известен импульсный стабилизатор напряжения, содержащий последовательный LDC-фильтр, ключевой регулятор, подключенный параллельно элементам

DC-фильтра, управляемый блокингенератор, блок управления, узел регулирования частоты, эмиттерный повторитель и импульсный усилитель (2).

Недостатками этого стабилизатора являются сложность блока управления и частотная модуляция управляющего сигнала. Последний недостаток практи" чески исключает возможность реализа- ции стабилизатора повышенной надежности.

Наиболее близким по технической сущности к предлагаемому является импульсный стабилизатор напряжения с блоком для управления шириной импульсов в регулируемых источниках питания, содержащий ключевой регулятор, подключенный параллельно выходным выводам стабилизатора,. транзистор, эмиттер которого подключен к общей шине стабилизатора, а коллектор, соединенный со входом ключевого регулятора, через коллекторный резистор подключен ко входной шине стабилизатора, соединенной через базовый резистор с базой этого тран935910 зистора, подключенной к выходу хронирующего конденсатора, блок управления, вход которого через резистивный делитель напряжения соединен с выходом стабилизатора, генератор тактовых импульсов и фильтр. Второй вывод хронирующего конденсатора соединен с .выходом специального формирователя импульсов, вход которого соединен с выходом генератора такто- >О вых импульсов. Упомянутый базовый резистор шунтирован управляемым сопрот .влением, управляющий вход которого подключен к выходу блока управления (3), 3»

Недостатками такого стабилизатора являются сложность, обусловленная применением специального формирователя импульсов и управляемо -о сопротивления, и низкий КПД, обусловленный низкой крутизной одного из фронтов входного сигнала ключевого регулятора, а именно — фронта, который формируется через блок управления. Последнее определяется тем, что д» в процессе формирования фронта не обеспечено замыкание петли положительной обратной связи.

Целью предлагаемого изобретения является упрощение стабилизатора и повышение его КПД.

Указанная цель достигается тем, что в стабилизатор постоянного на.пряжения, содержащий ключевой регулятор, подключенный параллельно вы3» ходным выводам стабилизатора, транзистор, эмиттер которого подключен к общей шине стабилизатора, а коллектор, соединенный со входом ключевого регулятора, через коллектор4О ный резистор подключен ко входной шине стабилизатора, соединенной через базовый резистор с базой этого транзистора,подключенной к выходу хронирующего конденсатора, блок управле4» ния, вход которого через резистив- ный делитель напряжения соединен с выходом стабилизатора, генератор тактовых импульсов и фильтр, введен резистор, один вывод которого подключен к выходу ключевого регулятора, »о другой — ко второму выводу хронирующего конденсатора и к выходу блока управления, вход которого подключен к выходу генератора тактовых импульCGB.

5»

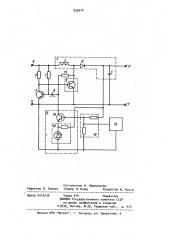

На чертеже представлена схема предлагаемого импульсного стабилизатора постоянного напряжения.

Стабилизатор содержит последовательный LOC-фильтр 1, ключевой регулятор 2, подключенный параллельно выходным выводам стабилизатора, транзистор 3, эмиттер которого подключен к общей шине 4 стабилизатора, а коллектор, соединенный со входом ключевого регулятора 2, через коллекторный резистор 5 подключен ко входной шине 6 стабилизатора, соединенной через базовый резистор 7 с базой транзистора 3, подключенной к выводу хронирующего конденсатора 8, блок 9 управления, вход которого через резистивный делитель 10 напряжения соединен с выходом 11 стабилизатора, генератор 12 тактовых импульсов и вновь введенный резистор 13, один вывод которого подключен к выходу ключевого регулятора 2, а другой— ко второму выводу хронирующего конденсатора 8 и к выходу блока 9 управления, вход которого подключен к выходу генератора 12 тактовых импульсов. В простейшем варианте блок 9 управления содержит транзистор 14, эмиттер которого соединен с выходом

1 параметрического стабилизатора 1 напряжения, а база и коллектор служат соответственно входом и выходом блока 9.

Устройство работает следующим образом.

При поступлении короткого импульса положительной полярности с генератора 12 тактовых импульсов на вход блока 9 управления транзистор 14 этого устройства входит в насыщение, а напряжение хронирующего конденсатора

8, имеющее полярность, указанную на чертеже, обеспечивает запирание транзистора 3, вследствие чего отпирается ключевой регулятор 2. С этого момента времени начинается накапливание энергии в элементе L фильтра 1 и перезаряд хронирующего конденсатора 8.

По окончании запускающего импульса с генератора тактовых импульсов 12 продолжается перезаряд хронирующего конденсатора 8 и накапливание. энергии в элементе L фильтра 1, поскольку потенциал обкладки конденсатора 8, соединенной с резистором 13, фиксирован на низком уровне из-за насыщенного состояния ключевого регулятора 2 (при этом транзистор 14 блока 9 управления работает в инверсном режиме и потенциал его коллектора практически равен потенциалу его эмиттера)..

9359

После того, как вследствие перезаряда хронирующего конденсатора током, протекающим через базовый резистор 7, напряжение на базе .транзистора 3 достигает отпирающего уровня, начинает- ся рост коллекторного тока этого транзистора и процесс запирания ключевого регулятора 2. При этом рост выходного. напряжения ключевого регулятора 2 приводит к замыканию петли 10 положительной обратной связи через резистор 13,. хронирующий конденсатор 8 и транзистор 3, обеспечивая крутой фронт запирания ключевого регулятора 2. Длительность интерва- 15 ла времени, в течение которого ключевой регулятор 2 находится в режиме насыщения, зависит (при фиксированных значениях сопротивления базового резистора 7, емкости хронирую- щ щего конденсатора 8 и частоты запускающих импульсов) от величины напряжения, до которого зарядится хронирующий конденсатор 8 к приходу следующего запускающего импульса с 23 выхода генератора 12 тактовых импульсов, а это напряжение автоматически устанавливается таким (путем усиления транзистором 14 сигнала разности выходных напряжений резис- 30 тивного делителя 10 и параметрического стабилизатора 15), чтобы поддерживать на практически неизменном уровне выходное напряжение импульсного стабилизатора при изменении входного 3 напряжения, нагрузки и других дестабилизирующих факторов.

При этом фактически введение резистора 13 с указанными связями обеспечивает получение ждущего мультивиб-,и3 ратора, одно из плеч которого выполнено на.транзисторе 3, а другоена ключевом регуляторе 2. Это обстоятельство упрощает разработку.резервированного стабилизатора предлага- емого типа.

Повышение крутизны фронтов сигнала управления ключевым регулятором 2, обусловленное отмеченным замыканием петли положительной обратной связи, позволяет в несколько раз (2-4) снизить по сравнению с известным пере" ключательные потери ключевого регулятора, следовательно, повысить КПД стабилизатора, особенно при повышенной частоте коммутации ключевого регулятора, обеспечивающей минимизацию

10 6 габаритно-массовых характеристик стабилизатора. Упрощение we импульсного стабилизатора по сравнению с известным определяется тем, что простой блок 9 управления выполняет в нем и функции усилителя - формирователя импульсов, а в сочетании с введенным резистором 13 - Функции, эквивалентные функциям управляемого сопротивления известного. Причем, это упрощение ведет к дополнительному повышению КПД стабилизатора.

Таким образом, технико-экономический эффект от реализации предло" женного импульсного стабилизатора постоянного напряжения определяется

его упрощением и повышением его КПД.

Формула изобретения

Импульсный стабилизатор постоянного напряжения, содержащий ключевой регулятор, подключенный параллельно выходным выводам стабилизатора, транзистор, эмиттер которого подключен к общей шине стабилизатора, а коллектор, соединенный с входом ключевого регулятора, через коллекторный резистор подключен к входной шине стабилизатора, соединенной через базовый резистор с базой этого транзистора, подключенной к выводу хронирующего конденсатора, блок управления, вход которого через резистивный делитель напряжения соединен с выходом стабилизатора, генератор тактовых импульсов и фильтр, о т л и ч а ю щ и йс я тем, что, с целью упрощения стабилизатора и повышения его КПД, в него введен резистор, один вывод которого подключен к выходу ключевого регулятора; другой - к второму выводу хронирующего конденсатора и к выходу блока управления, вход которого подключен к выходу генератора тактовых импульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Ю 440659, кл. G 05 F I/56„ 1974.

2. Виленкин А.Г, Импульсные транзисторные стабилизаторы напряжения.

И., "Энергия", 1970, с. 61.

3. Заявка ФРГ и 2608172, кл. G 95. F 1/48, 1977.

935910

Заказ 4210/50

Тираж 914 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель О. Мещерякова

Редактор Л. Повхан Техред М.Тепер Корректор М. Коста