Устройство для умножения матричного типа

Иллюстрации

Показать всеРеферат

и 935948

ОП ИСАНИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическнк

Республик (6! ) Дополнительное к авт. свид-ву (22) Заявлено 15.09,80 (2! ) 2085660/18 24 (5т)М. Кл.

@06 F 7/52 с присоединением заявки М

)ееударетеаный кемнтет

СССР (23) Приоритет (53) УДК 681. .325(088.8) но делам нзобретеннй н атермтнй

Опубликовано 15.06.82. Бюллетень № 22

Дата опубликования описания 15.06.82

А. И. Буртов, Ю. С. Ицкович, Л. Я. Лапкин, B. Г, Носов и А. H. Шполянский (72) Авторы изобретения (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЧНОГО

ТИПА

Изобретение относится к вычислитель ной технике и может быть использовано в быстродействующих арифметических устройствах различных цифровых малога« баритных комплексов, например, в устройствах цифровой фильтрации.

Известно матричное множительное устройство, содержащее две идентичные мат . рицы умножения, подключенрые свими выходами к первым входам двух сумматоров, две шины сомножителей, связан» ные через регистры и коммутаторы со входами матриц умножения. При этом матрица умножения с сумматором, подключенным к ее выходу, образует наращим ваемый матричный элемент, входом наращивания которого является второй вход сумматора, а выходом - выход сумматора..

Выход первого наращиваемого малерично го элемента соединен со входом второ го наращиваемого элемента, выход кото» рого подключен. к выходу устройства, При построении умножителей большой разря жостк наращиваемый матричный

2 элемент может быть выполнен в виде наращиваемого мощен умножения, Вследствие того, что быстродействие такого усчройства, главным образом„зависит от -быстродействия выходных сумматоров наращиваемых матричных элементов, в нем обеспечивается высокое быстродействие (1) °

Недостатком такого устройства явш » ется большой обьем оборудования, обусловленный наличием дополнительных регистров слов сомножителей, регистра сдвига, двух коммутаторов, регистра за держи и. 1

Известно матричное устройство для умножения и сложения, содержащее мат . рицу сложения, которая содержит !т!-1

I5 разрядных сумматоров, расположенных в )! линейках матрицы (где )! 7i, а Щ < - разряднос ть множителя), причем, (И-2) старШих выхода сумматоров млад,шей линейки соответственно соединены с -иеодами первой группы сумматоров, средней линейки (где (< СИ), младшие

935948

2; выходы первого сумматора младшей линейки соединены соответственно с младшими входами первой группы. сумматора старшей. линейки, (И-2) старших входа первой группы которого соединены с соответствующими выходами первого сумматора средней линейки, выходы второго сумматора средней линейки соответственно соединены с входами второй группы сумматора старшей линейки (2) .

rJ

Недостатком известного устройства является его высокая сложность, обусловленная наличием большого числа двухвходовых вентилей.

Цель изобретения - сокращение оборудования при сохранении быстродействия.

Поставленная, цель достигается тем, что в устройство введены Ф групп двухвходовых элементов И-НЕ по И в каждой

t руппе, (И +N) элементов НЕ и (yI+N) входовой

2О сумматор, причем первый вход ц ) -ro элементаИ-НЕ (4=1,..., И, ) =1..., <) соединенс соотвествующим входом множимого устройства, вторые входы элементов И-HE каждой группы объединены и подключены к соответствующему входу множителя устройства, входы младших разрядов сумматоров матрицы сложения объединены и подключены к шине логической единицы, Зд входы первой группы сумматоров младшей линейки матрицы сложения соединены соответственно с выходами элементов И-НЕ первых A/3 групп, входы второй группы сумматоров средней линейки соединены с выходами элементов И HE вторых Pal/3 групп, выходы элементов И-НЕ последних групп соединены соответственно со старшими входами сумматоров средней линей.ки матрицы сложения, выходы (И-1) младших элементов И-НЕ последних И/3 групп coellHHeHbr соответственно с входами второй группы сумматоров младшей линейки, матрицы сложения, выходы сумматора старшей линейки и младшие выходы второго. сумматора младшей линейки соот -" вественно соединены с входами элементов

НЕ, выходы которых соединены соответственно с входами сумматора.

Сущность изобретения состоит в том, что в матрице сложения суммируют инверсии частичных произведений, предварительно сформированные с помощью элементов И-НЕ, ввводят в сумматоры матриц поправку, обеспечивающую формирование на ее выходе инверсии произ- л ведения обрабатываемой части сомножителей, инвертируют инверсию произведения

И суммируют ее в (И +И)- входовомсумматоре с формируемым аналогично прсизведением apyroA части сомножителей.

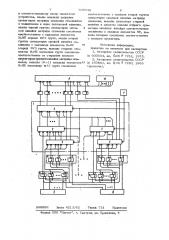

На чертеже представлена структурная схема устройства.

Устройство содержит матрицу 1 сложения, которая состоит из -1 Vl -разрядных сумматоров 2, элементы 3 И-НЕ, объединенных в kM групп 4, вход я множимого, вход 6 множителя, шину 7 логической единицы, элементы 8 HE, (И+ Ф)axonoaoé сумматор 9. для наращивания разрядности в устройстве предусмотрена шина 1О наращивания разрядности.

В устройстве (-2) старших выходов сумматоров 2 младшей линейки соответственно соединены с Р входами первой группы сумматоров 2 средней линейки (где g< Pc И ), младшие выходы первого сумматора 2 младшей линейки соединены соответственно с младшими входами первой группы сумматора 2 старшей линейки (И -2) старших входа первой группы которого соединены с соответствующими выходами первого сумматора 2 средней линейки, выходы второго сумматора 2 средней линейки соответственно соединены с входами второй группы сумматора 2 старшей линейки, первый вход 6) -го элемента И-НЕ (1 =1,..., и, g =1,... М ) соединен„с соответствующим входом 5 множимого устройства, вторые входы элементов 3 И-НЕ каждой группы обьединены и подключены к соответствующему входу 6 множителя устройства, входы младших разрядов сумматоров 2 матрицы 1 сложения обьединены и подключены к шине 7 логической единицы, входы первой группы сумматоров 2 младшей линейки матрицы 1 сложения соединены соответственно с выходами элементов

3. И-НЕ первых И/3 групп, входы второй группы сумматоров 2 средней линейки соединены с выходами элементов 3

И-НЕ вторых И"/3 групп, выходы старших элементов 3 И-НЕ последних групп соединены соответственно со старшими входами сумматоров 2 средней линейки матрицы 1 сложения, выходы (у -1) младших элементов 3 И-НЕ последних

Ю/3 групп соединены соответственно с входами второй группы сумматоров 2 младшей линейки матрицы 1 сложения, выходы сумматора 2 старшей линейки и младшие выходы второго сумматора 2 младшей линейки соответственно соединены с входами элементов 8 НЕ, выходы которых соединены соответственно с входами сумматора 9.

Устройство работает следующим образом.

Сигналы множимого и множителя в прямом коде поступают соответственно через входы 5 и 6 на первые и вторые 5 входы элементов 3 И-НЕ. Элементы

3 И-НЕ каждой группы 4 управляются разрядом множителя так, что число на выходе последующей группы имеет вдвое больший вес, чем на выход предыдущей.

Число на выходе группы 4 представляет .собой инверсию частичного произведения множимого на соответствующий разряд .мн ож ителя.

Обозначив множимое через Х, а мно-. житель через У, и используя двоичное представление чисел, записывают И -разрядное число Х и М -разрядное число У в виде И

Х=,2 х 2.

1=1

И4

У= 3s г.

141 где Х -, У1 — значение 1 -х разрядов чи4 ° селХиУ, Инверсия частичного произведения на выходе 1-ой группы элементов 3 И-НЕ с учетом веса разряда множителя равна

A-=X3- г." " ) З0

1 1 где А . — 1. — разрядное частичное про I изведение (1=1, 2,... YYI ).

Учитывая, что инверсию (обратный ход) некоторого И -разрядного числа В можно

0 записать в виде 5--2 -9-2, представляютз5 инверсии частичных произведений А, следующим образом:

A =ХЧ„2. --2-Х „Я. -2.;

Сумма частичных произведений (3) представляет собой 8+I11-разрядное число 45 которое с учетом выражения (1) может быть представлено в виде

С = Я." Xg 3 -(g + 2 о., + 2 - 1 И) (Ч)

1(ля получения инверсии произведения

ХУ необходимо в выражении (4) компен50 сировать выражения в скобках. Для этого на входы переносов младших разрядов сумматоров 2 матрицы 1 сложения подают компенсирующий сигнал поправки от шины

7 логической единицы. Образовавшийся на М выходе MBTpBIlbI 1 сложения инверсный код произведения инвертируется элементами 8 НЕ. С выхода элементов 8 HE IIpoизведения обрабатываемых разрядов сомножителей поступает на первые входы (Ю + Itl1)-входового сумматора 9, на вторые входы которого одновременно от шины 10 наращивания разрядности поступает произведение другой части сомножителей. После суммирования на выходах сумматора 9 оказывается сформированным полное произведение сомножителей, При построении многоразряасых множительных устройств такого типа в отличие от из-вестного, ситнапы переноса распространяются одновременно и независимо во всех устройствах, вследствие чегобыстродействие всего устройства опреде ляется быстродействием одного устройства. Поэтому при увеличении разрядности сомножителей для сохранения высокого быстродействия не приходится увеличивать быстродействие сумматоров матрицы сложения, как в известном, .что позволяет использовать в матрице простые сумматеры, и следовательно, упростить устройство в целом без снижения быстродействия, Формула иэобре тек ия

Устройство для умножения матричного типа, содержащее матрицу сложения, которая содержит l и-разрядных сумматоров, расположенных в К линейках матрицы (где Я7 —, а )м- разрядность. М множителя), причем (И -2) старшие выходы сумматоров младшей линейки соответственно соединены с p axolIBMH первой группы сумматоров средней линейки (где 1(СИ), младшие выходы первого сумматора младшей линейки соединены соответственно с младшими входами первой группы сумматора старшей линейки, (М-2) старших входа первой группы которого соединены с соответствующими выходами первого сумматора среа ей линейки, выходы второго сумматора среАней линейки соответственно соединены с входами второй группы сумматора стар шейлинейки, отличающееся тем, что, с целью сокращения оборудования при .сохранении быстродействия, в него. введены И1 групп двухвходовых эле ментов -HE по И в каждой группе, (Ф +Уп) элементов HE и (yl +ю1)-входовбй сумматор, причем первый вход ц -го элемента И-НЕ (1=1,". И, =1"" а ) соединен с соответствующим входом множимого устройства, вторые входы элементов И-,НЕ каждой груйпы обьединенг. к соответствующему входу множителя устройства, входы младших разрядов сумматоров матрицы сложения обьединены и подключены к шине логической единицы, входы первой группы сумматоров млад- 5 щей линейки матрицы сложения соединены соответственно с выходами элементов

И-HB первых Эи/3 групп, входы второй группы сумматоров средней линейки соединены с выходами элементов И-НЕ вторых .И /3 групп, выходы старших эле ментов И-НЕ последних групп соединены соответственно со старшими входами сумматоров средней линейки матрицы сложения, выходы (И:1) младших элементов 1.

И-НЕ последних И /3 групп соединены соответственно с входами второй группы сумматоров младшей линейки матрицы сложения, выходы сумматора старшей линейки и младшие выходы второго сумматора младшей линейки соответственно соединены с входами элементов НЕ, выxollbI которых соединены соответственно с входами сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 600554, кл, 606 F 7/52, 1975.

2.,Авторское свидетельство СССР

No. 169881, кл. 06 F 7/50, 1963 (прототип).

ВНИИПИ Заказ 4213/52, Тираж 731 Подписное

Филиал ППП Патент», r. Ужгород, ул., Проектная, 4