Цифро-частотный интегратор

Иллюстрации

Показать всеРеферат

Союз Советских

Социапистичвсиих

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ .К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (ii) 935955 (61) Дополнительное к авт. свид-ву (22)З я»ено 14 12.79 (21) 2855382/18-24 с присоединением заявки,% (23) Приоритет (5>)>. К>.

G 06 F 7/64

9вударстеалный комитет

СССР ао делам изобретений и открытнй (5З) УДК 681. 323 (088.8) Опубликовано 15. 06. 82. Бюллетень М 22

Дата опубликования описания 17.06.82 (72) Авторы изобретения

И.И. Холкин, Е.И, Кашицын, M.Í. Левин, И.Б. Никифоров и А.А. Логинов

« (71) Заявитель. (54) ЦИФРО-ЧАСТОТНЫЙ ИНТЕГРАТОР

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых интегрирующих машин, цифровых дифферен" циальных анализаторов, различных цифро-аналоговых и частотно-импульсных

3 вычислительных устройств.

Известно цифровое сглаживающее устройство, состоящее иэ двоичных умножителей, реверсивного счетчика, 10 распределителя импульсов, причем реверсивный счетчик имеет обратную связь с последнего знакового разряда на все разряды счетчика, кроме первого, а на входе счетчика подключен распре15 делитель импульсов, управляющие входы которого соединены со знаковыми разрядами. При размыкании контура обратной связи и подаче импульсов приращений на вход распределителя такое устройство может служить цифро-частотным интегратором и позволяет получать знакопеременную подынтегральную функцию $1).

Известное устройство имеет следующие недостатки: при смене знака подинтегральной функции требуются 2 такта, что ухудшает быстродействие устройства; значение подынтегральной функции представляется в прямом коде, что затрудняет сопряжение такого устройства с ЦВН, в которой данные представляются как правило в дополнительном двоичном коде.

Известно устройство, содержащее регистр подынтегральной функции, в качестве которого используется реверсивный счетчик, опорный делитель частоты и схемы И, ИЛИ, причем выходы счетчика, и делителя частоты соединены со входами схем И, а выходы последних подключены ко входам схемы ИЛИ, выход которой является выходом устройства (2).

Недостатком такого устройства является невозможность использования

его при получении энакоперемемных значений подынтегральной функции, пред93595

5 . 4

cTBBJlReMblx в дополнительном двоичном коде.

Цель изобретения - расширение функциональных воэможностей за счет получения знакопеременных значений подынтегральной функции, представляемых в дополнительном двоичном коде.

Поставленная цель достигается тем, что в цифро-частотный интегратор, содержащий реверсивный счетчик, опор- " ный делитель частоты, группу элементов И и элемент ИЛИ, причем вход счетчика подключен к входу приращений подынтегральной функции интегратора, ! выход каждого разряда счетчика подключен к выходной шине подынтегральной функции интегратора, вход опор ного делителя частоты подключен к входу опорной частоты. интегратора, первый вход каждого элемента И группы подключен к выходу соответствующего разряда счетчика, второй вход каждого элемента И группы подключен к соответствующему выходу опорного делителя частоты, выходы элементов И группы. подключены к входам элемента ИЛИ, введены триггер знака, три схемы И и триггер, причем вход триггера знака подключен к выходу старшего разряда реверсивного счетчика, выход триггера знака подключен к выходной шине подынтегральной функции к первому входу первого элемента И, второй вход которого подключен к входу опорной частоты интегратора, выход> ! элемента ИЛИ подключен к первому входу второго элемента И и устанЬвочному входу триггера, прямой выход которого подключен к второму входу второго элемента И, выход которого яв- . е ляется первым выходом интегратора, выход первого элемента И подключен к первому входу третьего элемента И и входу сброса триггера, инверсный выход которого подключен к второму м входу т рет ье го элемента И, выход которого является вторым выходом интегратора.

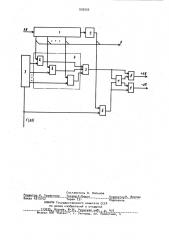

На чертеже изображена структурная схема цифро-частотного интегратора.

Интегратор содержит реверсивный счетчик 1, триггер знака 2, опорный делитель частоты 3, группу элементов И 4, элемент ИЛИ 5, первый элемент И б, триггер 7, второй и третий элементы И 8 и 9.

Устройство работает следующим образом.

При положительном значении подынтегральной функции триггер знака 2 находится в нулевом состоянии, первый элемент И 6 закрыт, триггер 7 в единичном состоянии, и на выходе интегратора образуются только положительные приращения в виде импульсов, поступающих через второй элемент И 8 с выхода элемента ИЛИ 5. В этом случае устройство работает точно так же как и известный цифро-частотный интегратор.

Значение кода подынтегральной функции у определяется суммой поступивших на вход счетчика приращений Ьу.

Делитель частоты осуществляет деление опорной частоты F и гормирование импульсных последовательностей с часF Р тотами., —,— . Причем эти им к пульсы "не совпадают друг с другом во времени. Тактовые импульсы, поступающие на вход опорного делителя с частотой Г, представляют собой приращения независимой переменной Ьх. На ! выход элемента ИЛИ проходят только те импульсные последовательности с опорного делителя частоты, которым соответствуют единичные состояния разрядов счетчика. Таким образом, число выходных импульсов (сумма приращений д2) определяется выражением

К к- к,У а . 2дх, 2к K-1 где а .= 0,1 — состояния разрядов счетчика, или при достаточно малом периоде чередования тактовых импульсов b,x х

„J (х)мх. о

При отрицательном значении подынтегральной Функции, которое представляется в дополнительном двоичном коде, триггер знака 2 открывает первый элемент И 6, и число импульсов на выходе устройства представляет собой разность импульсов с выхода элемента ИЛИ и импульсов потока Г. Iloскольку частота импульсов на выходе элемента ИЛИ 5 всегда меньше частоты Г, то в этом случае на вых!оде третьего элемента И 9 находятся только отрицательные приращения .Ь Z число которых определяется выражением

2 С 6к. 2 ! где а к - состояния разрядов счетчи9359

1 " I

0,25

0,125

t5 (0,875-1)F =

=-0,125

-1 О 111

-0,125 го

-0,25 (0,75-1)" =

=-0,25F

-1 0 1,1 0 ка для отрицательного числа у, представленного в дополнительном коде.

В таблице дана работа устройства в момент перехода счетчика через "0" и образования в нем отрицательного S числа (значение в счетчике выражено в десятичном коде).

ЬУ Удес

-1 О 010 0,25F

-1 О 001 0,125f

-1 0 000 О

Значение подынтегральной функции у действительно представляется гЗ в дополнительном коде, причем частота FZ приращений д2 определяется значением этого кода как для положительных, так и отрицательных величин у, а знак приращений определяется вы- ьо ходами второго и третьего элементов И.

Причем для схемы знака подынтегральной функции не требуется дополнитель" ных тактов °

Таким образом, в отличие от из" естного цифро-частотного интеграто а предлагаемый интегратор имейт бо-лее широкие функциональные возможности, т.е. позволяет получать знакопеременные значения подынтегральной о функции, представленные в дополнительном двоичном коде. Это упрощает сопряжение его с цифровой вычислительной машиной, данные в которой также представляются в дополнительном коде. Кроме того, при смене знака подинтегральной функции не требуется . дополнительного такта.

Формула изобретения

Цифро-частотный интегратор, содер- ур жащий реверсивный счетчик, опорный

5 jrà 6 делитель частоты, группу элементов И и элемент ИЛИ, причем вход счетчика подключен к входу приращений подынтегральной функции интегратора, выход каждого разряда счетчика подключен к выходной шине подынтегральной функции интегратора, вход опорного делителя частоты подключен к входу опорной частоты интегратора, первый вход каждого элемента И группы подключен к выходу соответствующего разряда счетчика, второй вход каждого элемента И группы подключен к соответствующему выходу опорного делителя частоты, выходы элементов И группы подключены к входам элемента ИЛИ, о т л. и ч аю шийся тем, что, с целью расширения функциональных возможностей за счет получения знакопеременных зна ений подынтегральной функции в дополнительном коде, в него введены триггер знака, три элемента И и триггер, причем вход триггера знака под ч ключен к выходу старшего разряда реверсивного счетчика, выход триггера знака подключен к выходной шине подынтегральной функции и первому входу первого элемента И, второй вход которого подключен к входу опорной частоты интегратора, выход элемента ИЛИ подключен к первому входу второго элемента И и установочному входу триггера, прямой выход которого подключен к второму входу второго элемента И, выход которого является первым выходом интегратора, выход первого элемента И подключен к первому входу третьего элемента И и входу сброса триггера, инверсный выход которого подключен к второму входу третьего элемента И, выход которого является вторым выходом интегратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

g 155044, кл. 606 F 15/00, 1963.

2. Патент СВА У 2910237, кл.235150,3, опублик. 1959, (прототип).

935955

Составитель В. Вальков

«Редактор M. Ïàðôåíîâà Texgeg К.Мы ьо Корректор М 1аро и

Заказ 1i213/52 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1130Я Москва Ж-)5 Раушская набд g. 4/5

Филиал ППП "Патент", г-. Ужгород, ул, Проектная,