Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистически« республик

ОП ИСАНИЕ

ИЗОВРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii 935959

{61) Дополнительное к авт. свид-ву

{22)Заявлено 07.07.80 {21) 2995857/18-24 с присоеднненнеэт заявки J4

{23) Приоритет (Ы)М. Кл..0 06 F 9/22

9кудэрстеонвй квн«тет

СССР

«е дэлэн «забретен«й я этэрытяй (53) УДК 681. 325 (088.8) Опубликовано 15.06.82. Бюллетень М 22

Дата опубликования описания 17.06.82

{72) Автор . изобретения

И. Б. 1Иапиро! (. /

{71) Заявитель (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

Изобретение относится к вычислительной технике и может быть использовано s универсальных и специализированных цифровых вычислительных машинах.

Известно микропрограммное устройство управления, содержащее память микрокоманд, регистр микрокоманд, дешифратор адреса оперативной памяти, оперативную память, блок реверсивных формирователей тога, дешифратор адреса микрокоманды, регистр адреса микрокоманды, блок усилителей чтения, коммутатор, шифратор и регистр регенерации (1 1.

Недостатком устройства является большой объем оборудования и незначительное быстродействие.

Наиболее близким к изобретению по технической сущности является микропрограммное устройство управления, содержащее блок памяти микропрограмм, блок проверки условий и регистры адреса (? ).

Однако известному устройству присущи низкое быстродействие и сложность.

Поставленная цель достигается тем, что в микропрограммное устройство уп5 равления, содержащее блок памяти микропрограмм, блок проверки условий и два регистра адреса, причем группа информационных выходов блока проверки условий соединена с группой информационных входов первого регистра адреса, выходы первого и второго регист1 ров адреса соединены соответственно с первым и вторым адресными входами блока памяти микропрограмм, первая группа выходов которого соединена с первой группой входов блока проверки условий, вторая группа входов которого соединена с группой входов условий устройства, вторая группа выходов блока памяти микропрограмм является группОЙ Йнформационных ВыхОдОВ устрОйст ва, введены регистр микропрограммы, блок памяти адресов возврата и men мент НЕ, причем управляющий выход бло9359 ка проверки условий соединен с установочным входом первого регистра адреса и через элемент НЕ соединен с установочным входом второго регистра адреса, управляющий выход блока памяти микропрограмм соединен с установочным входом регистра микроподпрограммы, выход которого соединен со входом блока памяти адресов возврата, грулпа выходов которого соедине- 10 на с группой информационных входов второго регистра адреса, группа информационных выходов блока проверки условий соединена с .группой инфорМационных входов регистра микропод- 15 программы.

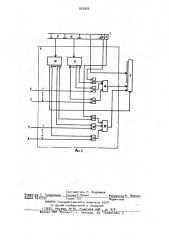

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - блоксхема ..блока проверки условий.

Устройство содержит блок 1 памяти

20 микропрограмм, регистры 2 и 3 адреса, блок 4 проверки условий, регистр 5 микроподпрограммы, блок 6 памяти адресов возврата, элемент НЕ 7, группу

25 информационных выходов 8 устройства и группу входов 9 условий устройства.

Блок проверки условий содержит дешифраторы 10 и 11, группы элементов И 12 и 13 и элементы ИЛИ l4 и 15.

Устройство работает следующим образом.

Когда не происходит обращение к микроподпрограмме на выходах блока 1 с помощью синхронизирующих сигналов

{не показаны) производится последовательное формирование микрокоманд.

Причем операционная часть каждой микрокоманды поступает по выходам 8 в операционные узлы, а адресная часть на блок 4 проверки условий, на который по входам 9 поступают также осведомительные сигналы. По результатам сравнения адресной части и осведомительных сигналов формируется адрес следующей микрокоманды, который записывается в регистр 2 адреса. При этом сигнал с управляющего выхода блока 4 проверки условий разрешает чтение информации из регистра 2 адреса, а сиг 50 нал с выхода элемента HE 7 запрещает чтение информации из регистра 8 адреса.

Рассмотрим работу устройства при выходе на микроподпрограмму. 55

Пуст ь на и нформац ионных выходах блока 4 сформирован последний адрес прерываемой программы. Этот адрес

59 с помощью си нх рани зи рующих сигналов записывается в регистр 2, при этом из блока 1 считывается последняя микрокоманда прерываемой микропрограммы, в управляющем разряде которой записана "1". flo фронту сигнала, поступающего с управляющего выхода блока 1 происходит запись в регистр 5 информации, находящейся на его информационных входах, т.е. последнего адреса прерываемой микропрограммы.

В следующем такте в регистр 2 адреса записывается адрес первой микрокоманды микроподпрограммы и начинается выполнение микроподпрограммы.

Второй и последующие адреса микрокоманд микроподпрограммы формируются так we как и в основной микроподпрограмме по информационным входам с помощью блока 4.

При этом сигнал с управляющего выхода блока 4 разрешает чтение ин1 формации из регистра 2, а сигнал с выхода элемента HE 7 запрещает чтение информации из регистра 3.

По последнему адресу прерванной микропрограммы, записанному в регистре 5 с помощью синхронизирующих сигналов, происходит считывание из блока б и запись в регистр 3 из соответствующей микроподпрограммы.

Таким образом при выполнении определенной микроподпрограммы в регистре 3 хранится адрес микрокоманды, с которой необходимо продолжать основную микропрограмму при выходе из микроподпрограммы.

В последней микрокоманде микроподпрограммы в адресной части содержится признак выхода из микроподпрограммы.

При этом сигнал с управляющего выхода блока 4 запрещает чтение информации из регистра 2, а сигнал с выхода элемента HE 7 разрешает чтение информации из регистра 3. Следующая микрокоманда считывается по адресу, хранящемуся в регистре 3 и таким образом продолжается выполнение прерванной микропрограммы.

Изобретение позволяет получить выигрыш по быстродействию для алгоритмов, в которых из каждой микрокоманды возможен переход на одну микроподпрограмму и переход на микроподпрограмму осуществляется по адресу, записанному в микропрограмме, за счет исключения из блока памяти микропрограмм микрокоманд входа в микроподпрограмму.

5 9359 в которых задается адрес возврата иэ микроподпрограммы. Кроме того, изобретение дает возможность упростить устройство за счет использования значительно меньшего объема блока памяти микропрограмм.

Формула и эобретения

1О

Микропрограммное устройство управления, содержащее. блок памяти микропрограмм, блок проверки условий и два регистра адреса, причем группа информационных выходов блока проверки ус- 1э ловий соединена с группой информационных входов первого регистра адреса, выходы первого и второго регистров адреса соединены соответственно с первым и вторым адресными входами бло-фо ка памяти микропрограмм, первая группа выходов которого соединена с первой группой входов блока проверки условий, вторая группа входов которого соединена с группой входов, условий 25 устройства, вторая группа выходов блока памяти микропрограмм является группой информационных выходов уст-.

99 6 ройства, о т л и ч а ю щ е е с я ем, что, с целью повышения быстродействия и упрощения устройства, в него введены регистр микроподпрограммы, блок памяти адресов возврата и элемент НЕ, причем управляющий выход блока проверки условий соединен с установочным входом первого регистра адреса и через элемент НЕ с установочным входом второго регистра адреса, управляющий выход блока памяти микропрограмм соединен с установочным входом регистра микроподпрограммы, выход которого соединен с входом блока памяти адресов возврата, группа выходов которого соединена с rpyti- пой информационных входов второго регистра адреса, группа информационных выходов блока проверки условий соединена с группой информационных входов регистра микроподпрограммы.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 519711, кл. G 06 Г 9/22 ° 1974.

2. Авторское свидетельство СССР

Н 643874, кл. G 06 F 9/22, 1976 (прототип).

935959

Филиал ППП "Патент", r. Ужгород, ул. Проектная, Составитель М. Кудряшев

Редактор Т. Пар©енова Техред К»4» Корректор М. НаРоши

Заказ 4213/52 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам. изобретений и открытий

113035 Москйа Ж-35 Раушская наб. д. 4/5