Устройство для управления доступом к магистрали

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соаетскик

Соцмалксткческкк

Республик 935961 (6I ) Дополнительное к авт. свид-ву (22) Заявлено 22.08.80 (2l ) 2977239/18-24 (5l)M. Кл. с присоединением заявки J%

GO6 F 0/46

Гааударстаенный камнтет (23) Приоритет

Опубликовано l5.06 82. Бюллетень № 22

Дата опубликования описания j 5 06 82 ао яелам нзобретеннй н аткрь1тнй (53) УДK 68>.

° 825(088.8) (72) Автор. изобретения

В. П. Молоков

Ъ, ь

Специальное конструкторское бюро промышленной айтоматики (7l ) Заявитель (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ДОСТУПОМ

К МАГИСТРАЛИ

Изобретение относится к вычислитель. ной технике и может быть использовано при создании микропроцессорных систем, использующих магистральный принцип связи.

Известно устройство управления доступом к магистрали, содержащее блок приоритета, выход которого подключен ко входам дешифратора, выходами соединенного с информационными входами запоминающего регистра, управляющий вход к оторого подключен к источнику синхронизируюших сигналов. На входы блока приоритета поступают сигналы запроса доступа к магистрали, а с выходов запоминающего регистра-выдаются сигналы подтверждения доступа к магистрали (lj.

Ю

Недостатками известного устройства являются необходимость синхронизации и низкое быстродействие, определяемое частотой синхронизации.

Наиболее близким по технической сущности к предлагаемому изоброте|ппо является многоканальное устройство приоритета, содержащее элемент И-НЕ, а в каждом канале - триггер, элемент ИЛИ, элемент ИЛИ-НЕ и элемент И, причем гасящий вход триггера соединен с соответствующим входом группы входов устройства, установочный вход триггеров каналов, кроме первого, соединен с прямым выходом триггера предыдущего канала, выход элемента ИЛИ каждого канала, кроме первого, соединен с первым вхо10 дом элемента ИЛИ предыдущего канала, прямой выход триггера последнего канала и выход элемента ИЛИ первого ка— нала через элемент И-НЕ соединен с устаноВочным входом триггера первого ка15 нала, а первый вход элемента ИЛИ пос леднего канала соединен с первым входом устройства, инверсный выход и установочный вход триггера канала через эл

20 мент ИЛИ-НЕ канала соединен с первым входом элемента И канала и соответствующим входом запускающего элемента

ИЛИ, выход элемента И канала соединен с соответствующим выходом грунты вы3 9З59 ходов устройства, а вход-выход, вход и выход коммутатора соединены соотвеч ственно с шиной обмена, с выходом за пускающего элемента ИЛИ и со вторыми входами элементов И каналов 12).

Недостатком известного устройства, яапяетса то, что с увеличением числа вход лв запросов к обмену, быстродействие улройства снижается пропорпионально числу этих входов и время появления 10 сигнала на И ом выходе подключения источника информации относительно появления сигнала на и -ом входе запроса к обмену в g раз больше, чем у первого выхода подключения источника информа- м ции

Белью изобретения является увеличеwe быстродействия устройства.

Поставлеаыя пель достигается тем„ что .в устройство для управления досту- уй пом к магистрали, содержащее М эле» ментов И-НЕ, алемент ИЛИ, выходы которого подключены к выходам элементов

И-НЕ, первые входы элементов И НЕ являются входами запроса устройства, 2 введены дешифратор, элемент задержки и Й элементов ИСКЛЮЧАЮШЕЕ ИЛИ, выходы которых являются выходами разрешения устройства, группа информационных входов дешифратора со-;-динена с соотвеч ствуюпами выходами алементов И-НЕ, выходы элемента ИЛИ подключнйы к управляющему входу дешифратора и ко входу алемента задержки, выход которого подключен к первому входу первого элемента ИСКЛЮЧАЮШЕЕ ИЛИ, q -й вы35 ход дешифратора (1 3. - И) подключен ко второму входу 1 го алемента ИСКЛЮ

ЧАЮШЕЕ ИЛИ, первому входу < + го злсмента ИСКЛЮЧА10ШЕЕ ИЛИ и второму

Щ входу 1 -го элемента г";НЕ.

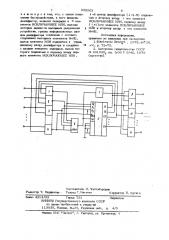

На чертеже представлена блок-схема предлагаемого устройства.

Устройство содержит элементы

И-НЕ 1-4, выход каждого из которых подключен к соответствующему входу группы информационных входов дешифратора 5 и к соответствующему входу элемента

ИЛИ 6, выход которого соединен с упраьляющим входом дешифратора 5 и со вхс дом блока задержки 7, выход последнего подключен к одному иэ входов элемента.

ИСКЛЮЧАЮШЕЕ ИЛИ 8, первый выход дешифратора 5 подключен ко второму входу элемента ИСКЛЮЧАЮШЕЕ ИЛИ 8, к первому входу элемента ИСКЛЮЧАЮШЕЕ ИЛИ 9 и к одному из входов элемента И-HE 1, второй выход дещифратора

61 4

5 соединен со вторым входом элемента

ИСКЛЮЧАЮШЕЕ ИЛИ 9, к первому входу элемента ИСХЛЮЧАЮШЕЕ ИЛИ 10 и к одному из входов элемента И-НЕ 2, третий выход дешифратора подключен ко второму входу алемента,ИСКЛЮЧАВШЕЕ ИЛИ 10 и к одному из входов. элемента И-НЕ 3, .1 -ый выход дешиф ратора соединен со вторым входом элемента ИСКЛЮЧАЮШЕЕ ИЛИ 11 и с одним:из входов элемента И-НЕ 4, другие входы элементов И-НЕ 1-4 со единены с источникамн запросов доступа к маги страли.

Предлагаемое устройство работает следующим образом.

На входы устройства поступают, например, единичные уровни сигналов запроса доступа к магистрали. Сигналу згйроса, поступающему на 4 -ый вход, соответствует единичный уровень си; нала на а -ом выходе устройства. В случае поступления на входы устройства нескольких сигналов запроса устройство воспри« нимает только один из них и формирует только один сигнал подтверждения на выходе. Другие запросы обслуживаются только после снятия обслуживаемого запроса.

В исходном состоянии при отсутствии запросов на доступ к магистрали на пер-. вые входы алементов И-НЕ 1-4 поступают сигналы, соответствующие логическому нулю, при атом на выходах з емен— тов И-НЕ 1-4 появляются сигналы, соответствующие логической еди тче, которые поступают на входы элемента ИЛИ 6.

На выходе элемента ИЛИ 6 появляется единичный сигнал, который поступает на уп1авляюакй вход и на вход блока задержки 7. Время задержки сигнала в блоке задержки 7 равно времени раопрост ранения сигнала от управляющего входа. Состояние сигналов на выходах дешифратора описываются следующими логическими уравнениями: ф

С-С,У, У, У,, ° в °

Сь Со Уо У У У У У °

° ° Ф

Ф

С С Уо У У -У - я У, .

В соответствии с уравнениями на выходах дещифратора 5 присутствуют единичные сигналы, при этом на выходах элементов ИСКЛЮЧАЮШЕЕ ИЛИ 8-11 присутствуют нулевые сигналы, что соот

5 035961 ь чение, а сигналы на выходах С -С1 остаются в единичном состоянии. При этом на входы элемента ИСКЛЮЧАЮLUEE ИЛИ 8 поступают нулевые сигналы и не его выходе также появляется нуле вой сигнал. На вход элемента ИСКЛЮЧАЮШЕЕ ИЛИ 10 поступают сигналы раз» ных уровней и на его выходе появляет» ся единичный сигнал, который соответствует наличию сигнала запроса на входе элемента И-НЕ 3. На вторые входы эпементов И-НЕ 2 и И-НЕ 1 поступают нулевые сигналы с выходов С, С дешифратора 5, запрещающие прохождение сигналов, поступающих на первые входы элементов И-НЕ 1, И-HE 2,.до тех пор пока на его входах У -У„ „ и С не появятся единичные сигналы

Таким образом, если ус.ройство находится в исходном состоянии и íà его

1 -ый зход поступает сигнал запроса. дос тупа к магистрали, то на выходах С„ -С„, появяются сигналы нулевого уровня, а .на ыходах С. -С„остаются сигналы

1 единичного уровня, сигнал подтверждения д.>ступа сформируется на выходе 1 -rc элемента ИСКЛЮЧАЮШЕЕ ИЛИ и время появления сигнала подтверждения относительно cm.нала запроса будет одинаковым ! для всех выходов.

Если д-я снятия сигнала запроса, т. е. до возврашения устройства в исходное сс стояние на другие входы залроса поступают сигналы, то и после снятия 1 -ого запроса сигнал подтверждения формирует -. ся в ответ на запрос, поступающий на

1+1 вход устройства. В этом случае обслуживание сигнала осуществляется без возврата устройства в ис одное состояние. Запросы с номерами, меныоими

1, воспринимаются устройством после возврата его в исходное состояние. првчем Обслркивание начинается с запроса, имеющего -пяыеньший номер.

Таким образом, введ ние в устройст во -дешифратора, блока задержки, элемен:г. ü ИСКЛЮЧАЮШЕЕ ИЛ!1 позволяет уве: ичить быстродействие устройства, имеющего И входов, в К раз. ветствует отсутствию сигналов подтверждения доступа к магистрали.

Если на вход элемента И-HE 1 постучает сигнал запроса поступа к магистрали, то при совпадении единичного уровня этого сигнала с единичным уровнем сигнала, поступающего с выхода дешифратс ра 5, на выходе элемента И-НЕ 1 формируется нулевой сигнал; который поступает на информационный вход дешифрато10 . ра 5 и на первый вход элемента ИЛИ 6, с выхода которого нулевой сигнал посту пает на управляющий вход и на вход блока задержки 7. Так как значение первого входа У входит во все уравнения, описывающие сигналы на выходах С -CN дешифратора 5, то на всех его выходах при этом присутствуют единичные сигналы, в этом случае на обоих входах элементовь ИСКЛЮЧАЮШЕЕ ИЛИ 9-11 при- 0 сутствуют единичные сигналы. На первый вход элемента ИСКЛЮЧАЮШЕЕ ИЛИ 8 с выхода блока задержки 7 поступает сигнал нулевого уровня, а на другой вход, элемента ИСКЛЮЧАЮШЕЕ ИЛИ 8 с выхода С„. дешифратора 5 поступает сигнал единичного уровня, в результате чего на его выходе формируется сигнал единичного уровня, который является ответным сигналом на сигнал, поступающий на вход 30 элемента -HE 1. После снятия сигнала запроса доступа к магистрали со входа элемента И-НЕ 1 устройство возвращает ся в исходное состояние.

Если на вход элемента И-НЕ 3 поступает сигнал запроса доступа к магистралИ. до снятия сигнала запроса со входа элемента И-НЕ 1, тосс выхода элемента

И-HE 3 снимается сигнал нулевого уров 40 ня, который поступает на информационный вход У2 дешифратора 5 и на третий вход элемента ИЛИ 6..Появление на входе У дешифратора 5 нулевого сигнала не изме няет состояние сигналов на выхОдах 45

С -С„ дешифартора 5,. так как они удер1 .живаются в единичном состоянии нуле- вым сигналом.на его входе УО. После снятия сигнала запроса на входе элемен

S0 та И-НЕ 1 сигнал на информационном вхоДе Уо ДешифРатоРа 5 и на пеРвом входе элемента ИЛИ 6 изменяет свой уро» уровень на единичный. При этом на в1.ходе элемента ИЛИ 6 присутствует ну» левой сигнал, так как íà его третий вход

55 поступает нулевой сигнал с выхода элемента И-НЕ 3. Согласно логическим . уравнениям исигналы на выходах С, С2 дешифратора принимают нулевое зна-, Формула изобретения. Устройство для управления доступом к магистраля, содержащее Й элементов И-НЕ, эл:-мент ИЛИ, входы которого подключены к выходам элементов -HE„ первые входы элементов И-НЕ ямяются входами запроса устройства, о т л и—

7 935961 8 ч а ю щ е,е с я тем, что, с целью ловы- 3 -й выход дешифратора (=1-И) подклю чен к второму входу -го элемента дешифратор элемент задержки и Й we ИСКЛЮЧАЮШЕЕ ИЛИ, первому входу ментов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы (+1)-го элемента ИСКЛЮЧАЮШЕЕ которых являются выходами разрешения s ИЛИ и второму входу 4 -го элемента устройства, группа иифорлационных входов дешифратора фра ра соединена с соответ Источники информации, ствуювп ми выходами элементов И-НЕ, принятые во внимание при экспертизе Ъ с входок элемента задержки, выход ко- 2. Авторское свидетельство СССР торого подключен к первому входу пер- ¹ 631920> кл. 506 F 9/46, 1978 вого элемента ИСКЛЮЧАЮШЕЕ ИЛИ, (прототип).

Заказ 4214/53 Тщ 31

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москве, Ж 35, Раушская наб., д. 4/5

Подписное

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4

CocTBBHTBBb П. Чистобородов

Редактор, Т. Парфенова Техред Т.Мат очка Корректор В. Бутята