Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

Союз Советских

Социалистических

Республик (и)936031

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 16.05.80 (21) 2925794/18-24 (51) М. К .

G I1 С 27/00 с присоединением заявки №вЂ”

Г447Аарстеаиай кемктет

СССР (23) Приоритет—

Опубликовано 15;06.82. Бюллетень № 22 (53) УДК 681.327..66 (088.8) ll0 делам кзееретенкй и еткрмтий

Дата опубликования описания 15.06.82 (72) Авторы изобретения

В. Н. Осипов и,Л. А. Дубицкий

) .,Львовский ордена. Ленина политехнический институт им.,Ленинского комсомола (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРО1 1СТВО

Изобретение относится к вычислительной технике и предназначено для запоминания мгновенных значений и может быть использовано в аналоговых и в аналого-цифровых вычислительных устройствах.

Известно замкнутое аналоговое запоминающее устройство, содержащее операционные усилители, ключи, конденсаторы памяти. В замкнутых устройствах применение операционных усилителей, охваченных общей обратной связью, позволяет повысить точность, причем в некоторых устройствах достигается дополнительное повышение точности за счет компенсации ошибок усилителей (1) .

Однако известное аналоговое запоминающее устройство замкнутого типа обладает недостаточным быстродействием, так как операционные усилители работают в режиме большого сигнала со значительными динамическими перегрузками. Поэтому одним из главных факторов, ограничивающих быстродействие (время выборки, скорость слежения) является недостаточная скорость нарастания на выходе применяемых усилителей. Введение цепей коррекции частотных характеристик усилителей, обеспечивающих устойчивость, включение конденсаторов памяти в цепи нагрузки усилителей приводит к уменьшению скорости нарастания и к снижению быстродействия.

Наиболее близким к предложенному по

5 технической сущности является аналоговое запоминающее устройство, которое содержит основной усилитель, первый и второй ключи, соединяющие соответственно вход и выход устройства с неинвертирующим входом ос1в новного усилителя, выход которого через третий ключ подключен к инвертирующему входу основного усилителя и к одной обкладке конденсатора памяти, другая обкладка которого подключена к шине нулевого потенциала, дополнительный усилитель, 15 подключенный выходом к выходу устройства, инвертирующим входом через резисторы— к выходу устройства и к выходу основного усилителя, соединенного инвертирующим входом с неинвертирующим входом дополнительного усилителя (2).

В режиме хранения второй ключ замкнут, а первый и третий ключи разомкнуты. Конденсатор памяти заряжен до напряжения, соответствующего предшествующему отсчетуПри поступлении команды на переход уст936031

45

3 ройства в режим выборки первый и третий ключи замыкаются, а второй размыкается.

Входное напряжение поступает на неинвертирующий вход основного усилителя. Дифференциальное напряжение, присутствующее на входах основного усилителя, в первый момент времени после переключения устройства может достигать значительных величин. Например, при синусоидальном входном сигнале оно может составлять 2Ц», где U»1 — амплитудное значение входного сигнала. Основной усилитель при этом оказывается в динамической перегрузке. Конденсатор памяти заряжается со скоростью, не превосходящей максимальную скорость нарастания на выходе основного усилителя с подключенной емкостной нагрузкой. Этот процесс занимает значительную часть времени выборки. Увеличение скорости нарастания выходного напряжения основного усилителя связано со значительными трудностями ввиду емкостного характера нагрузки и необходимости введения цепей частотной коррекции, обеспечивающих устойчивость устройства как в режиме выборки, так и в режиме хранения. Недостаточная скорость нарастания приводит также к ограничению по максимально допустимой скорости изменения входных сигналов, являющейся одной из основных характеристик быстродействия устройства.

Целью изобретения является повышение быстродействия аналогового устройства.

Поставленная цель достигается тем, что в аналоговое запоминающее устройство, содержащее первый усилитель, первый вход которого соединен с выходами первого и второго ключей, вход первого ключа является входом устройства, первый накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, другая обкладка конденсатора соединена с выходом третьего ключа, вход которого соединен с выходом первого усилителя, второй вход которого подключен к другой обкладке конденсатора, второй усилитель, выход которого является выходом устройства и соединен с входом второго ключа, введены повторитель напряжения, четвертый ключ и второй накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, а другая обкладка — с выходом четвертого ключа, с третьим входом первого усилителя и с первым входом второго усилителя, охваченного по второму входу обратной связью, третий вход второго усилителя подключен к выходу первого усилителя, четвертые входы первого и второго усилителей соединены с шиной нулевого потенциала, выход первого ключа соединен с входом повторителя напряжения, выход которого соединен с входом четвертого ключа.

1О

25 зо

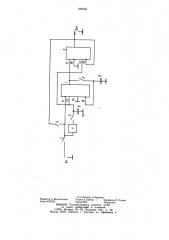

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит усилители 1 и 2, ключи 3 — 6, повторитель 7 напряжения, накопительные элементы, например конденсаторы 8 и 9, шину 10 нулевого потенциала, входы 11 — 14 усилителя 1, входы 15 — 18 усилителя 2.

Предложенное устройство функционирует следующим образом.

В режиме хранения ключ 4 замкнут, а ключи 3, 5 и 6 разомкнуты. Конденсатор 9 заряжен до напряжения, соответствующего предшествующему отсчету. Напряжение на конденсаторе 8, как будет показано, близко к нулю. При переходе в режим выборки ключ 4.размыкается, а ключи 3, 5 и 6 замыкаются. Напряжение от источника входных сигналов через замкнутый ключ 3 поступает на вход 11 усилителя 1, представляющего собой дифференциально-дифференциальный усилитель. Напряжение, близкое к входному, поступает также с некоторой задержкой на вход 13 усилителя 1. Задержка вызвана перезарядом конденсатора 9 с выхода повторителя 7. Повторитель 7 реализован по разомкнутой схеме и, следовательно, не содержит внутренних цепей коррекции.

Известно, что такие схемы, имеющие низкую точность, обладают предельным быстродействием, поэтому перезаряд конденсатора 9 может быть завершен за несколько десятков наносекунд. За это время напряжение на выходе усилителя 1, ввиду его инерции, не может измениться существенно. После перезаряда конденсатора 9 в процессе слежения за входным сигналом напряжение на выходе усилителя 2 и на конденсаторе 8 определяется из соотношения

К1 ) ((св(р(= ((вв(р) — (р — ((((в(р((() (1) где Uagp) — входное напряжение;

К1() — коэффициент передачи разомкнутого усилителя 1 по входам ll и 12;

К () — коэффициент передачи разомкнутого усилителя 1 по входам 12, 14;

К „(р) — коэффициент передачи повторителя 7.

В формуле не учтены погрешности, обусловленные напряжениями смещения нуля усилителя 1, его синфазными ошибками, так как рассматриваются только факторы, влияющие на быстродействие. Поскольку в формуле (1) коэффициенты i((,) и К (p) приблизительно равны и значительно больше единицы, а сомножитель 1 — Krt(p) близок к нулю, то напряжение 1 (ив(р) близко к нулю.

Усилитель 1 работает в режиме усиления малой разности напряжений, присутствующих на входах 11 и 13, и его быстродействие определяется практически малосигнальными характеристиками. Скорость изменения на20

9360 пряжения на выходе усилителя 1 значительно ниже, чем скорость изменения входного сигнала.

Таким образом, ограниченная скорость нарастания усилителя 1 не приводит к уменьшению быстродействия устройства, посколь— ку напряжение на выходе усилителя 1 и на конденсаторе 8 изменяется незначительно.

Конденсатор 9 заряжается с выхода повторителя 7, построенного по разомкнутой схеме и не содержащего цепей коррекции.

Ошибки усилителя 2 можно не учитывать, !О поскольку он в режиме хранения охвачен вместе с усилителем цепью общей обратной связи и подавление его ошибок в устройстве очевидно. Поэтому можно предположить, что коэффициенты передачи напряжений с входов замкнутого усилителя 2 к его выходу равны по абсолютной величине единице, а напряжения смещения нуля и синфазные ошибки по его входам отсутствуют. Поэтому напряжение на конденсаторе 9 в режиме выборки

31

Устройство обеспечивает высокую точность даже при значительном отличии коэффициента передачи повторителя от единицы и малых величинах К, и К2.

Таким образом, предложенное устройство не уступая известному устройству по точнос; ти, значительно превосходит его по быстродействию. В предложенном устройстве ограничения по скорости нарастания усилителя 1, охваченного в режиме выборки обратной связью, не приводят к ухудшению параметров устройства, характеризующих быстродействие (время выборки, скорость слежения), поскольку усилитель 1 в режиме выборки используется для усиления малых сигналов. В предложенном устройстве сочетается высокое быстродействие, свойственное разомкнутым схемам аналоговых запоминающих устройств, и высокая точность, достигнутая в лучших замкнутых устройствах.

Формула изобретения

1- с9 UÂX Кп (2)

Напряжение на конденсаторе 8 в режиме выборки к, к, к, 1 се 1 вх (-1 п), „+1/ol + Uoz ®

1+Кг 1+ к2 !+к, где Uol — напряжение смещения нуля усилителя 1 по входам 11 и 13 с учетом синфазных ошибок;

Uo2 — напряжение смещения нуля усилителя 1 по входам 12 и 14 с учетом синфазных ошибок.

Напряжение на выходе устройства в режиме хранения к -ь, (/вмх 1/вх "o (1 "и) VBx (1+g)(.g) o

К! -1 ° к2 цц(0+к,х1+к ) ц62 ГК5г! кт и)

Как следует из выражения (4), напряжения

Uol и Uo2 подавляются в устройстве соответственно в К2 и К! раз.

Далее их можно не учитывать. Тогда абсолютная погрешность составит

1+К1Ф К в UBx =VBx вых вх(I Kll) (!+К )(нк,) (5) Если предположить, что К,= К = К, то /вх = /вх кп

2 (6) где ЬКп — погрешность коэффициента передачи повторителя 7.

Можно считать, что погрешность, обусловленная неидеальностью повторителя, подавляется в К/2 раз.

Пусть К,= К2 — — 100, а Кд — — 0,98. Тогда

ЬЦ х согласно (5)

Ь(.1вх = 0,0004! 1вх

bUBx = — х 100 /o = 0 04 /oЬУ вх

Аналоговое запоминающее устройство, содержащее первый усилитель, первый вход которого соединен с выходами первого и второго ключей, вход первого ключа является входом устройства, первый накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, другая обкладка конденсатора соединена с выходом третьего ключа, вход которого соединен с выходом первого усилителя, второй вход которого подключен к другой обкладке конденсатора, второй усилитель, выход которого является выходом устройства и соединен с входом второго ключа, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены повторитель напряжения, четвертый ключ и второй накопительный элемент, например конденсатор, одна из обкладок которого соединена с шиной нулевого потенциала, а другая — с выходом четвертого ключа, с третьим входом первого усилителя и с первым входом второго усилителя, охваченного по второму входу обратной связью, третий вход второго усилителя подключен к выходу первого усилителя, четвертые входы первого и второго усилителей соединены с шиной нулевого потенциала, выход первого ключа соединен с входом повторителя напряжения, выход которого соединен с входом четвертого ключа.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3696305, кл. 330-51, опублик. 1972.

2. Авторское свидетельство СССР № 482815, кл. G 11 С 27/00, 1974 (прототип) .

936031

Составитель А. Воронин

Редактор Л. Веселовская ТехредА. Бойкас / Корректор Е.Рошко

Заказ 4222/56 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и оч крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патгент», г. Ужгород, ул. Проектная, 4