Резервированное запоминающее устройство

Иллюстрации

Показать всеРеферат

И С A H К Я (>936035

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву— (22) Заявлено 22.08.80 (21) 2976391II18-24. с присоединением заявки №вЂ” (23) Приоритет— (51) М. К .

G 11 С 29/00

Гасударственный кемитет

СССР

Опубликовано 15.06.82. Бюллетень № 22

Дата опубликования описания 15.06.82 (53) УДК 681.327 (088.8) пе делам изабретеннй и аткрмтий (72) Авторы изобретения

В. Н. Харитонов, В. Я. Мусиенко, Е. Я. Белалов, Н. Н. Журавский, А. Г. Забуранный, Э. В. Рудаков, С. П. Саламатов и А. М. Селигей

Киевский ордена Трудового Красного Знамени завой вычислительных и управляющих машин (71) Заявитель (54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к запоминающим устройствам.

Известно резервированное запоминающее устройство, содержащее модули памяти, шины интерфейса, блоки анализа и управления (1) .

Недостатком этого устройства являются большие аппаратурные затраты.

Наиболее близким по техническому решению к предложенному является резервированное запоминающее устройство, содержащее модули памяти, узел реконфигурации, узел выборки модуля, узел управления цепями реконфигурации, устройство отображения, узел контроля по паритету (2) .

Недостатком этого устройства является то, что логический адрес каждого модуля памяти жестко связан с логическими адресами предыдущих модулей памяти и влияет на логические адреса последующих модулей памяти. Это приводит к тому, что при исключении неисправного модуля памяти автоматически меняются логические адреса и последующих модулей памяти, что делает невозможным использование информации в них. Кроме того, исключенный модуль памяти становится недоступным процессору, 2 что делает невозможными тестовые проверки этого модуля памяти. Количество резервных модулей памяти в этом устройстве задается с помощью перемычек, а сами резервные модули памяти процессору в нормальном режиме работы недоступны. Это делает невозможным оперативное изменение количества резервных модулей памяти, например, в связи с изменением класса решаемых задач.

Кроме того, в этом устройстве сложный интерфейс связи с процессором. Указанные обстоятельства снижают надежность этого устройства.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее блоки памяти, подключенные к блоку выборки информации и блоку управления, и блок диагностики, первые вход и выход которого соединены соответственно с первым выходом и входом блока

2о управления, вторые вход и выход которого соединены соответственно с выходом и первым входом блока выборки информации, а третий вход блока управления является входом устройства, введены коммутатор

936035 входных данных, коммутатор адресных сигналов и накопитель, входы которого подключены к выходам коммутатора входных данных и коммутатора адресных сигналов и третьему выходу блока управления, а выход — к вторым входам блока выборки информации и блока диагностики, входы коммутатора адресных сигналов соединены с четвертым выходом блока управления, вторым выходом блока диагностики и входом устройства, входы коммутатора входных данных подключены к пятому выходу блока управления и входу устройства.

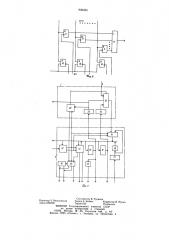

На фиг. 1 изображена структурная схема резервированного запоминающего устройства; на фиг. 2 — функциональная схема блока выборки информации; на фиг. 3 функциональные схемы блока диагностики и блока управления.

Устройство содержит блок 1 диагностики, блок 2 управления, блок 3 выборки информации, блоки 4,1 — 4.N памяти (где N целое число), коммутатор 5 адресных сигналов, накопитель 6, состоящий из N регистров, коммутатор 7 входных данных. Устройство имеет вход 8.

Блок 3 выборки информации содержит элементы И 9, элементы И вЂ” НЕ 10 и элемент ИЛИ 11.

Блок 2 управления содержит узел 12 приоритета, формирователь 13 временных интервалов, регистр 14 входных данных, формирователь 15 контрольных разрядов, регистр 16 адреса, регистр 17 выходных данных, контрольный регистр 18, распределитель 19, узел управления 20, выходной коммутатор 21.

Блок диагностики 1 содержит дешифратор 22 направлений, управляющий регистр

23, регистр 24 сбойного адреса и коммутатор 25.

Устройство работает следующим образом.

При включении питания блок 2 управления вырабатывает серию управляющих сигналов, по которым в накопитель 6 записывается начальное распределение блоков 4 по математическим адресам. Адрес начального распределения и данные начального распределения поступают в накопитель 6 из блока 2 управления через соответствующие коммутаторы 5 и 7. В результате начального распределения каждому математическому адресу блока 4 ставится в соответствие единственный заранее определенный для данного адреса блок 4, который и будет доступен при обращении по заданному математическому адресу. Далее блок 2 переводит коммутатор 5 в режим приема старших разрядов адреса с входа 8 устройства, а накопитель 6 — в режим считывания информации, после чего устройство ожидает запроса на использование.

При обращении к устройству процессор (не показан) выставляет на входе 8 адрес, данные (при операции записи), код опера5

4 ции и сигнал запроса на обращение. Старшие разряды адреса поступают в блок 2 и через коммутатор 5 — в накопитель 6.

При этом по этому адресу происходйт считывание слова из накопителя 6, которое поступает в блок 3. Если хотя бы в одном разряде считанного слова имеется единичная информация и соответствующий блок 4 имеется в наличии, то блок 3 вырабатывает сигнал, подтверждающий доступность адресуемого объема памяти, который поступает в блок 2. Получив этот сигнал, а также сигнал запроса на обращение от процессора, при условии, что поступивший от процессора адрес не входит в зону адресов блока 1 диагностики, блок 2 управления выдает в блок 3 потенциал выборки. По этому потенциалу блок 3 выдает потенциалы выборки тем блокам 4, которым в считанном из накопителя 6 слове соответствуют единицы.

После этого блок 2 осуществляет обращение к блокам 4 в соОтветствии с заданным алгоритмом. Все необходимые адресные, етробовые и другие сигналы поступают ко всем блокам 4 из блока 2.

В том случае, если блок 2 не получит от блока 3 сигнал подтверждения доступности адресуемого объема памяти, устройство уведомляет процессор о неправильной адресации путем, например, задержки сигнала окончания операции обращения либо другим способом, что вызывает в процессоре прерывание по соответствующему признаку.

Если при обращении к устройству схемами контроля, находящимися. в блоке 2, будет обнаружена ошибка, блок 2 выдает в блок 1 диагностики строб, по которому в блоке 1 диагностики фиксируется состояние устройства в момент ббнаружения ошибки. Блок 2 уведомляет процессор об ошибке либо выдачей контрольного бита, либо иным способом. Процессор при этом может начать выполнять программу обработки прерывания по ошибке.

Записывая предварительно в управляющий регистр 23 блока 1 диагностики признак обращения к какому-либо из остальных регистров блока 1 диагностики, процессор затем читает состояние соответствующего регистра. Таким же образом, записывая предварительно в управляющий регистр 23 блока 1 диагностики признак обращения к накопителю 6 и адрес конкретного слова, процессор может прочитать содержимое всего накопителя 6. Определив по старшим разрядам адреса, записанного в регистрах блока 1 диагностики, математический адрес блока 4, при обращении к которому была обнаружена ошибка, и имея распределение блоков 4 по математическим адресам, процессор определяет физический неисправный модуль 4, а затем производит программным способом реконфигурацию памяти устройства.

Реконфигурация памяти устройства производится путем изменения содержимого

936035 накопителя 6. При этом в управляющий в регистр 23 блока 1 диагностики предвари- в тельно записывается признак обращения у к накопителю 6 и адрес ячейки, содержимое с которой нужно изменить. Затем производит- в ся запись в накопитель 6 информации, ко- 5 а торая поступает с входа 8 через коммута- в тор 7. с

Формула изобретения

Предложенное устройство позволяет сократить потери информации при перераспределении памяти, упростить внешниЙ интерфейс памяти, оперативно изменять количество резервных блоков памяти, ускорять тестовые проверки памяти, производить тестовые проверки неисправных блоков памяти под любыми логическими адресами.

Кроме того, предложенное устройство обеспечивает контроль и сохранность . информации при перераспределении памяти.

Резервированное запоминающее устройство, содержащее блоки памяти, подключенные к блоку выборки информации и блоку управления, и блок диагностики, первые

6 ход и выход которого соединены соответстенно с первыми выходом и входом блока правления, вторые вход и выход которого оединены соответственно с выходом и перым входом блока выборки информации, третий вход блока управления является ходом устройства, отличающееся тем, что,. целью повышения надежности устройства, оно содержит коммутатор входных-данных, коммутатор адресных сигналов и накопитель, входы которого подключены к выходам комI 0 мутатора входных данных и коммутатОра адресных сигналов и третьему выходу блока управления, а выход — к вторым входам блока выборки информации и блока диагностики, входы коммутатора адресных сигналов соединены с четвертым выходом блока управления, вторым выходом блока диагностики и входом устройства, входы коммутатора входных данных подключены к пятому выходу блока управления и входу устройства.

20 Источники информации, принятые во внимание при экспертизе

1. Патент США № 4150428, кл. 364-200, опублик. 1979.

2. Патент США № 3803560, кл. 340-172.5, опублик. 1974 (прототип).

+

Puz 3

Составитель В. Рудаков

Редактор,Л. Веселовская Техред А. Бойкас Корректор И. Муска

Заказ 4222/56 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 l 3035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5 филиал ППП «Патент», г. Ужгород, ул. Проектная, 4