Генератор ступенчатого напряжения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()936404

Союэ Советски к

Социалистические

Республик (6I ) Дополнительное к авт. свнд-ву 11 687571 (22) Заявлено 31, 10.80 (21) 2999686/18-21 с присоединением заявки И (23) П рноритет (51)Nl. Кл.

Н 03 К 4/02 еввудерствеккЫ квинтет

СССР

00 ямам кзобретеви11 и открытки

Опубликовано 15.06.82 ° Бюллетень № 22

Дата опубликования описания 15.06.82 (5Ç) УДК 621. 373 (088.8) (72) Автор изобретения

В. А. Кошечкин

Горьковский филиал Всесоюзного научно-иссле института нормализации в машиностроении го (71) Заявитель (54) ГЕНЕРАТОР СТУПЕНЧАТОГО НАПРЯЖЕНИЯ

Изобретение относится к импульсной технике и может быть использовано например, в системами автоматического регулирования.

По основному авт. св. N - 687571 известен генератор ступенчатого на5 пряжения, содержащий цифр о-аналоговый преобразователь, триггер, счетчик импульсов, коммутатор, выходы счетчика импульсов соединены с входа- 0 ми коммутатора, выходы которого соединены с входами цифро-аналогового

C преобразователя, а. выход старшего разряда счетчика импульсов соединен с входом триггера, выход кото- 1 рого соединен с управляющим входом коммутатора 11.

Недостатком устройства является. ограниченность диапазона функций фор- 20 мируемого напряжения.

Целью изобретения является расширейие диапазона функций формируемого напряжения.

По ст авл енная цель достигается тем, что в генератор ступенчатого напряжения, содержащий цифро-аналоговьгй преобразователь, триггер, счетчик импульсов, коммутатор, выходы счетчика импульсов соединены с входами коммутатора, выходы которого соединены с входами цифро-аналогового преобразователя, а выход старшего разряда счетчика импульсов соединен с входом триггера, выход которого соединен с управляющим входом коммутатора, введены делитель частоты, включенный между вхоДной шиной устройства и входом счетчика импульсов, блок синхронизации, выход которого подключен к входу синхронизации цифро-аналогового преобразователя, входы которого подключены к соответству" ющим управляющим входам блока синхронизации, счетный вход которого подключен к входу делителя частоты, а синхронизирующий вход — к выходу делителя. частоты.

3 93640

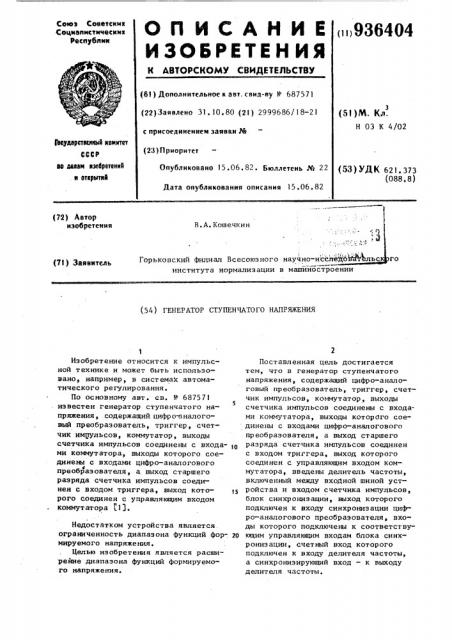

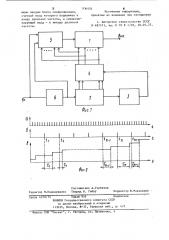

На фиг. I приведена структурная схема на фиг. 2 — эпюры напряжений, поясняющие работу схемы.

Устройство содержит цифро-аналоговый преобразователь l, счетчик 2 импульсов, триггер 3, коммутатор

4, блок 5 синхронизации, делитель

6 частоты.

Устройство работает следующим об. разом, 10

Поступающая «а вход и-разрядного счетчика 2 импульсная последовательность (фиг. 2б) после делителя 6 чаcrortt преобразуется им в прямой и обратный коды количества поступивших импульсов. Коммутатор 4 в зависимости от состояния триггера 3 управления подключает к цифро-аналоговому преобразователю I прямые (инверсные) выходы счетчика 2, На счетный вход блока 5 синхронизации поступает импульсная последовательность (фиг. 2а) . Синхронно с этим, импульсы, сформированные путем деления частоты входной импульсной последовательности фиг. 2б1 поступают на вход синхронизации блока 5 синхронизации. В момент поступления s -ro импульса на вход синхронизации блока 5 синхронизации и на вход счетчика 2, с выхода коммутатора 4 поступает прямой (инверсный) код на управляющие входы блока

5 синхронизации и цифро-аналогового преобразователя 1, соответствующий записи 1-ro импульса в счетчике 2.

При этом блок 5 синхронизации формирует импульс запуска, задержанный относительно переднего фронта t-ro синхро-импульса, поступающий с выхода

40 блока 5 синхронизации на вход синхронизации цифро-аналогового преобразователя 1. Величина задержки Т °

1 (фиг. 2в) определяется кодом записи

j-ro импульса, поступающего с выхода коммутатора 4. Код записи 1-го

45 импульса управляет динамической памятью блока синхронизации, с помощью которой в блоке синхронизации с поступлением j-ro синхронизирующего импульса разрешается счет к оличества опорных импульсов, поступающих на счетный вход блока 5 синхронизации и разрешается сравнение формируемого текущего кода количества опорных импульсов с кодом, формируемым.динамической памятью блока синхронизации, в момент сравнения которых с выхода блока 5 синхронизации посту1 пает на вход синхронизации цифроаналогового преобразователя 1 импульс запуска. При нос тупл енин на вход синхронизации цифро-аналогового преобразователя l., функционирующего в ждущем режиме, импульса запуска, на его выходе формируется i-я ступень восходящей (нисходящей) ветви напряжения. Длительность ступени определяется моментом поступления (i+1) -го импульса на вход синхронизации цифро-аналогового преобразователя 1.

Таким образом введение делителя

6 частоты и блока 5 синхронизации, в котором информация о величине сдвига импульса запуска, поступающего на вход синхронизации цифро-аналогового преобразователя относительно переднего фронта синхроимпульса, поступающего на вход синхронизации блока 5 синхронизации, может закладываться в динамическую память блока 5, которая позволяет управлять длительностью формируемых ступенек восходящей (нисходящей ) ветви сигнала.Это, в свою очередь, открывает возможность формирования ступенчатого сигнала с огибающей, изменяющейся во времени по требуемому закону (отрезки экспоненты, семейства отрезков парабол, семейство отрезков гипербол и т.д.) . При этом динамическая память блока 5 синхронизации может быть выполнена как с использованием регистров памяти при задании информации о величине задержки импульса запуска относительно синхроимпульса с помощью таблиц, так и в соответствии (при известных соотношениях изменения длиа тельности ступенек) логическому закону изменения задержки импульсов запуска логической схемой и блока 5.

Фоомула изобретения

Генератор ступенчатого напряжения, по авт. св, Ф 687571 о т личающийся тем,что,с целью расширения диапазона функций формируемого напряжения, в него введены делитель частоты, включенный между входной шиной устройства и входом счетчика импульсов, блок синх— ронизации, выход которого подключен к входу синхронизации цифро-аналогового преобразователя, входы которого подключены к соответствующим управля5 ющим входам блока синхронизации, счетный вход которого подключен к входу делителя частоты, а синхрониэирующий вход — к выходу делителя частоты.

936404 б

Источники информации, принятые во внимание при экспертизе

1 ° Авторское свидетельство СССР

К- 687571, кл. H 03 К 4/02, 20.01.77.

Составитель А.Горбачев

Редактор M.Íåäoëóæåíêo Техред И. Гайду . Корректор 10.Макаренко

Заказ 4258 75 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб °, д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4