Устройство для установки триггерных схем в исходное состояние

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республми

O Il И C А Н И Е ()936408

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ: (61) Дополнительное к авт. свнд-ву (22) Заявлено 18.07. 80 (21) 295 7626/18-21 с присоединением заявки М (23) П риоритет (51) М. Кл.

Н 03 К 5/13

Н 03 К 3/286

1нвударетеанные кемнтет

CCCP ае делен нзебретеннй н открытий

Опубликовано 15.06. 82. Бюллетень № 22

Дата опубликования описания 15.06. 82 (53) УДК 62! .374:

: 681. 325 (088.8) (72) Авторы изобретения

В.А.Кизуб, В.М.Костылев и В.А.Кутузов (71) Заявитель (54) УСТРОЙСТВО ДЛЯ УСТАНОВКИ ТРИГГЕРНЫХ

СХЕМ В ИСХОДНОЕ СОСТОЯНИЕ

Изобретение относится к вычисли тельной технике и автоматике и может быть использовано при создании вычислительных устройств, работающих при сбоях питания.

Известны устройства для установки триггерных схем с использованием вспомогательных источников напряжения 613 °

Недостатком этих устройств является ограничение области применения вследствие необходимости дополнительного источника питания.

Известно также устройство для установки триггерных схем в исходное состояние, в котором используются интегрирующие цепи и делители на резисторах, включенные по мостовой схеме f2).

Однако надежность работы этого устройства зависит от балансировки диагоналей мостовой схемы, а длительность импульса установки зависит от глубины провала питакенего напряжения, вследствие чего известные устройства не реагируют . на кратковременные провалы питающего напряжения. А так как триггерные схемы уст ройства автоматики и вычислительной техники могут произвольно переключиться, даже при кратковременных провалах питающего напряжения, то указанные недостатки могут привести к неправильному их функционированию и снижению надежности их работы.

Цель изобретения — повышение надежности работы устройства при крат" ковременных пропаданиях питающего напряжения.

Поставленная цель достигается тем, что в устройство для установки триггерных схем в исходное состояние, содержащее два делителя на резисторах, где интегрирующие цепи, два компаратора и буферный усилитель, :причем первые входы компараторов соединены со средними точками делителей тра резисторах, а вторые входы—

3 93640 со средней точкой интегрирующих цепей, выход буферного усилителя соединен со средней точкой второй интегрирующей цепи, шина питания компараторов и буферного усилителя соединена с резисторами интегрирующих цепей и первым резистором второго делителя, а общая шина - с вторыми -резисторами делителей, конденсатором второй интегрирующей цепи и с конден- О сатором зашунтированной резистором первой интегрирующей цепи, введены диод, одновибратор, элемент И и дополнительный конденсатор, при этом анод диода соединен с первым резистором первого делителя, а катод — с резистором первой интегрирующей цепи, вход одновибратора и первый вход элемента И, соединены с выходом первого компаратора, а выход одновибра« тора соединен с вторым входом элемента И, выход которого соединен с входом буферного усилителя, обкладка дополнительного конденсатора, шины питания одновибратора и элемента И соединены с шинами питания и устройства.

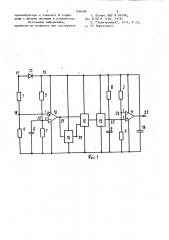

На фиг. 1 представлена схема устройства для установки триггерных схем в исходное состояние на фиг. 21

30 диаграммы, поясняющие работу устройства..

Устройство содержит резисторы

2, 3, 4 и 5, конденсатор 6, резистор 7 и 8, конденсатор 9,компараторы 10 и 11, буферяай усилитель

12, диод 13, одновибратор 14, элемент 1 5,,конденсатор 16..

Позициями 17-25 обозначены точки схемы, для которых приведены временные диаграммы, поясняющие работу устройства (фиг. 2).

Первый вход компаратора 10 соединен с.резисторами 1 и 2, второй вывод резистора 1 соединен с анодом диода 13. Второй вход компаратора

10 соединен с резисторами 5 и 7 и . первой обкладкой конденсатора 6, второй вывод резистора 5 соединен с катодом диода 13, с первой шиной питания компараторов !О и 11, одновибратора 14, элемента 15 И и буферного усилителя 12, второй вывод резистора 7 соединен со второй обкладкой конденсатора 6, со вторым выводом резистора 2 и второй шиной пита- SS ния компараторов 10 и 11 одновибратора 14, буферного усилителя 12 и элемента 15 И. Выход компаратора 10

8 4 соединен с первым входом элемента

15 И и входом одновибратора 14, выход которого соединен с вторым входом элемента 15 И. Выход элемента 15 И соединен с входом буферного усилителя 12, выход которого соединен с вторым входом компаратора 11, резис-, тором 8 и первой обкладкой конденсатора 9. Второй вывод резистора 8 соединен с первой шиной питания, а вторая обкладка конденсатора 9 — с второй шиной питания. Первый вход компаратора 11 соединен с резисторами 3 и 4, вторые выводы которых соединены соответственно с первой и второй шинами питания. Обкладка конденсатора 16 соединены с шинами питания.

Устройство работает следующим образом.

При нормальном питщщем напряжении первый вход (плюс) компаратора !

О (фиг. 1) находится под высоким потенциалом относительно второго (минус ) и на его выходе присутствуют высокий уровень напряжения, который поступает на первый вход элемента

15 И, на второй вход которого также поступает высокий уровень напряжения. В результате на выходе элемента

15 И присутствует высокий логический уровень, который подается на буферный усилитель 12.. При этом выходной транзистор усилителя 12 заперт, а конденсатор 9 заряжен почти до напряжения питания, поэтому второй вход (плюс) компаратора 11 находится под высоким потенциалом относительно первого хода (минус) и на его выходе присутствует высокий логический уровень.

Если цепь от источника питания, подключаемого к точке 17, прерывается, потенциал первого входа (плюс) компаратора 10 скачком понижается почти до нулевого уровня и становится ниже потенциала на втором входе (минус),-удерживаемого на высоком уровне конденсатором. В результате изменения знака разности между входными напряжениями на выходе компаратора 10 происходит переключение сигнала с высокого на низкий уровень.

При этом запускается одновибратор

14, вырабатывающий импульс низкого .логического уровня длительностью, равной длительности полного разряда конденсатора 9 через открытый транзистор буферного усилителя 12. Присутствие низкого логического уровня

936408 6 между собой и известными элемента ми схемы, позволяют увеличить надежность работы устройства при кратковременных пропаданиях питающего наб пряжения.

Формула изобретения

Устройство для установки триггерных схем в исходное состояние, содержащее два делителя на резисторах, две интегрирующие цепи, два компаратора и буферный усилитель, причем первые входы компараторов соеди. нены со средними точками делителей на резисторах, а вторые входы — со средней точкой интегрирующих цепей, выход буферного усилителя соеднней со средней точкой второй интегрирующей цепи, шина питания компараторов и буферного усилителя соединена с резисторами интегрирующих цепей и первым резистором второго делителя, а общая шина — с вторыми резисторами делителей, конденсатором второй интегрирующей цепи и с конденсатором зашунтированной резистором первойй интегрирующей цепи, о т л ич а ю щ е е с я тем, что, с целью повышения надежности работы устройства, в него введены диод, одновибратор, элемент И и дополнительный конденсатор, при этом анод диода соединен с первым резистором первого делителя, а катод — с резистором первой интегрирующей цепи, вход одновибратора и первый вход элемента

И соединены с выходом первого компаратора, а выход одновибратора соединен с вторым входом элемента И, выход которого соединен с входом буферного усилителя, обкладки дополнительного конденсатора, шины питания

5 на любом из выходов элемента !5 И открывает выходной транзистор буферного усилителя !2 ° Поэтому при переключении сигнала на выходе компаратора 10 с высокого на низкий логический уровень происходит полный разряд конденсатора 9 через открытый транзистор буферного усилителя

12. При восстановлении напряжения питания в точке 17 (в какой-бы момент времени оно не произошло) потенциал на первом (плюс J входе компаратора 10 становится выше потенциала на втором входе (минус ) компаратора !О, и на его вцходе появляется высокий логический уровень, поступающий на первый. вход элемента

IS И. Если при этом формирование импульса низкого уровня формирователем

14 окончено, то на выходе элемента 20

15 И появляется высокий логический уровень. Выходной транзистор буферного усилителя 12 за-срывается, и начинается заряд полностью разряженного конденсатора 9 через резистор 8. 2S

Если. восстановление напряжения питания в точке 17 происходит раньше, чем закончится разряд конденсатора

9, то импульс низкого уровня одновибратора 14 задержит .переключение сиг- за нала на выходе элемента 15 И на время, необходимое для полного разряда конденсатора 9.

Импульс предварительной установки вырабатывается на выходе компаратора !1 во время зарядки конденса-. тора 9 через резистор 8. При восстановлении питания напряжение на делителе, состоящем из резисторов 3 и 4, возрастает быстрее, чем на конден- 4О саторе 9, т.е. на первом входе (минус.) компаратора 11 во время заряда конденсатора 9 потенциал выше, чем на втором входе (плюс ) компаратора, поэтому на его выходе присутствует низкий логический уровень. После того, как конденсатор 9 зарядит-, ся, потенциал второго входа (плюс компаратора 11 становится выше потенциала первого: входа, и на выходе компаратора ll устанавливается высокий логический уровень.

Таким образом, сигнал на выходе компаратора 11 можно использовать в качестве сигнала первоначальной установки триггерных схем.

Введение в устройство диода, одновибратора, элемента И И конденсатора с соответствующими связями

Устройство обеспечивает стабильный по длительности импульс установки независимо от глубины:провала и длительности пропадания питающего напряжения.

Использование предлагаемого устройства позволяет исключить воэможv ность BpoHssoJIbHol переключения триггерных схем, вследствие пропадания напряжения питания, т.е. увеличить достоверность.и надежность работы устройства автоматики и вычислительной техники.

7 одновибратора и элемента И соединены с шинами питания и устройства.

Источники информации, принятые во внимание при экспертизе

936408

1. Патент ПНР Р 99798, кл. Н 02 Н 7/20, 1979.

2. "Электроника", 1974 Ф" 25 с ° 47 (прототип).

936408

Составитель С.Пронин

Редактор Н.Киштулинец Техред И. Гайду Корректор N.макаренко

Заказ 4256 75 Тирж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4