Многопороговый логический элемент

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ » 936427 (6! ) Дополнительное к авт. свид-ву (22)Заявлено 23.10.80 (2}) 2995491/18-21 с присоединением заявки J4 (23) Приоритет

Опубликовано 15.06 82. Бюллетень № 22

Дата опубликования описания 15,06.82 (51)М. Кд.

Н 03 К 19/02

3еоударстеенный комитет

СССР по делам изаоретений и открытий (53) УД К 62». .374(088.8) (72) Авторы изобретения

И, А, Пальянов, M. Ф. Шакиров, B. И. и И. А. Чернакова

Омский политехнический институт (7!) Заявитель

4 1 (54) МНОГОПОРОГОВЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 4

Изобретение относится к автоматике и вычислительной технике, в частности к элементам пороговой логики.

Известен многопороговый логический элемент, содержащий линейный сумматор и последовательно включенный с ним дискриминатор (11 .

Недостатком известного многопороговэго логического элемента является низкая технологичность из-за наличия цепи пос10 ледовательно соединенных резисторов, определяющих пороги срабатывания, многопорогового дискриминатора. В процессе изготовления к этим резистораМ предъявляются повышенные требования по точнос15 ти, поскольку отклонение от номинала хотя бы одного резистора приводит к изменению порогов срабатывания логических элементов многопорогового дискриминатора. Особенно высоки требования к точности изготовления резисторов многопорогового дискриминатора при большом числе порогов многопорогового логического элемента.

Наиболее близким по технической сущности к предложенному является многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы, подключенный через разделительные диоды к первому входу логического элемента И-НЕ, образую|пего дискриминатор и резисторы, определяющие пороги срабатывания 32) .

Недостатком извес тного устройства является низкая технологичность и точность при бопьшом числе порогов срабаты- вания, На точность данного устройства существенное влияние также оказывает разброс входных характеристик логичеоких элементов -HE, входящих в мноГопороговый дискриминатор, особенно проявляющийся при изменении температурных условий работы. Кроме того, известное устройство характеризуется низкими фунвциональными возможностями, не позволя ющими-реализовать на нем более о мой микропороговой функции.

27 4

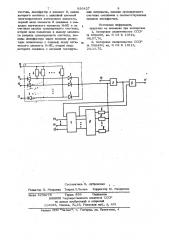

На чертеже представлена стр ктурная схема многопорогового логического элемента., Многопороговый логический элемент содержит линейный сумматор 1, состоящий из входных диодов 2, разделительных ди55 одов 3, и резисторов 4, образующих резисторную матрицу, дискриминатор на логическом элементе И-НЕ 5, весовые резисторы 6, определяющие порог срабатывания дискриминатора, суммирующий счет

40 чик 7, дешифратор 8 и элемент И 9.

Каждая пара диодов 2 и 3 линейного сумматора в точках, обьединяющих их аноды через резисторы 4, определяющие вес входов, подключена к положительному по45 люсу источника питания 10, Катоды диодов 3 объединены и подсоединены к первому входу логического элемента -HE

5 и через резисторы 6 к выходам дешиф

pBTopG 8. Входы дешифратора 8 сое50 динены с выходами суммирующего счет чика 7, младший разряд которого соединен еще и с одним входом логического элемента И 9, Второй вход последнего соединен с выходом логического элемента И НЕ 5 и со счетным входом суммирующего счетчика 7. Выход элемента

И 9 подключен к выходной клемме мно3 9364

Цель изобретения - расширение функциональных возможностей (реализация большего числа мноГопороговых функций), повышение технологичности и точности при большом числе порогов. 5

Поставленная цель достигается тем, что в многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов и резисторной матрицы и разделительных диодов, 10

1 выход линейного сумматора подключен к первому входу логического элемента, И-НЕ, образующего дискриминатор, и весовые резисторы, дополнительно введены суммирующий счетчик, дешифратор и эле- 15 мент И, выход которого соединен с выходной клеммой многопорогового логического элемента, первый вход элемента И соединен с выходом логического элемента

И-НЕ и со счетным входом суммирующе- р0 го счетчика, второй вход подключен к выходу младшего разряда суммирующего счетчика, выходы дешифратора через весовые резисторы подключены к первому входу логического элемента И-НЕ, второй р5 вход которого соединен с клеммой тактирующих импульсов, выходы суммирующе

ro счетчика соединены с соответствующИми входами дешифратора. гопорогового логического элемента 11.

Второй вход логического элемента И-НЕ

5 соединен с клеммой 12 тактирующих импульсов. На входы 13 линейного сумматора 1 поступают входные переменные многопорогового логического элемента. Входы 14 являются информационными входами суммирующего счетчика 7, Вход

15 является входом предварительной записи информации в двоичный счетчик. Источник питания .на чертеже не показан.

Многопороговый логический элемент работает следующим образом.

Перед подачей входных сигналов в клеммы 13 линейного сумматора 1 в суммирующий счетчик 7 производится запись информации путем подачи кода в клеммы 14 и импульса записи на вход

15, Йвоичньп код, записываемый в суммирующий счетчик 7, определяет количество порогов у многопорогового логического элемента. Не теряя общности рассуждений положим, что в счетчик 7 записан код

О О... О, то значит, что число порогов многопорогового логического элемента равно числу резисторов 6. двоичный код на выходе суммирующего счетчика 7 определяет какой из резисторов 6 подключен через соответствующий выход дешифратора 8 к отрицательному полюсу источника питания. Ивоичный код

О О... 0 на входах дешифратора 8 обуславливает подключение к отрицательному полюсу источника питания резистора 6, определяющего порог срабатывания Т1, код 0 О... 01 вызывает подключение резистора 6, соответствующего порогу срабатывания T (T< (Т ...

Ilocne занесения информации в суммирующий счетчик 7, в клеммы 13 поступают входные сигналы, которые в произвольных комбинациях запирают диоды. 2. Одновременно с поступлением входных сигналов в клемму 12 поступают тактовые импульсы. Если на входы 13 линейного сумматора 1 поступает комбинация входных переменных, для котоl1 рой Q X ° 03) (Т. )то ToK oT положительного

1- 1 полюса источника питания 10 через резисторы 4 и сдответствующие входному коду открытые диоды 3 переключаются в цепь резистора 6, соответству|ощего порогу Т„, вызывая на нем падение напряжения, недостаточное для срабатывания дискриминатора на логичеаком элементе

-HE 5. Тактовые импульсы, подаваемые в клемму 12, в этом случае не проходят

5 9364 на счетный вход суммирующего счетчика

7, состояние которого остается исходным

О О ... О, Поскольку на выходе младшего разряда суммирукяцего счетчика 7 присутствует уровень логического нуля, то и на выходе. 11 многопорогового логического элемента также присутствует уровень логического нуля.

Пусть теперь на входы 13 линейного сумматора 1 подана комбинация вход- 1о

1l ных переменных, дпя которойТ, «4,», Х. щ. C

1 1= (Т; В этом случае ток от положитепьного полюса источника питания 10 через резисторы 4 и открытые диоды 3 пере-. ключается в цепь резистора 6, соответствующего порогу Т, вызывая на нем падение напряжения, достаточное для срабатывания дискриминатора на логическом элементе И-HE 5. Тактовые импульсы, подаваемые в клемму 12 проходят на выход элемента 5 и поступают на счетный вход суммирующего счетчика

7. При этом состояние суммирующего 25 счетчика 7 изменяется с О О... О на

О О... 01, вызывая тем самым изменение порога срабатывания дискриминатора за счет подключении к отрицательному nomocy источника питания резистора 6, оп- зо ределяющего порог срабатывания То, Поскольку дпя поступившей на входы 13 ком1. Т3 бинации вхоiаых сигналов „Х. с4). g T,òî з

i=1 потенциала от протекании тока через ре- 35 зистор 6, соответствующий порогу Тп, становится недостаточно для срабатывания дискриминатора на логическом элементе И-HE 7 и поступление тактирующих импульсов на вход суммирующего 4о счетчика 7 прекращается. На выходе 11 многопорогового логического элемента, в этом случае, формируется уровень напряжения логической единицы, так как на выходе младшего разряда счетчика 7 и 45 выходе элемента И-НЕ 5 присутствуют уровни напряжения логической единицы.

Аналогичным образом происходит работа многопорогового логического элемен та и при других комбинациях сигналов на о входах 13 линейного сумматора 1. При этом тактирующие сигналы проходят на счетный вход суммирующего счетчика 7

П до тех пор, пока величина C X. Ы. пре1=1 1. 1 55 восходит или равна порогу цзабатывания, определиемому кодом, находящемся на суммирующем счетчике 7. Если величина

27 6 р и Х .. Ю большего четного порога и, 1 1

1=1 меньшего нечетного, то после прекращения поступления тактирующих импульсов на счетный вход суммирующего счетчика

7, младший разряд последнего устанавливается в нулевое состояние. При этом на выходе многопорогового логического элемента 11 формируется уровень поги-! и ческого нуля. Если величина Х .с4

1. поступившая на входы линейного сумматора 1 большего нечетного порога, но меньше четного, то после остановки суммирующего счетчика 7 в его младшем разряде находится единица, которая и определяет единичное значение функции на выходе

11 многопорогового логического элемента.

Если перед поступлением входных сигналов на суммирующем счетчике 7 установлен код, отпи шый от кода 0 О...

0, то многонороговый логический элемент реализует другую переключа тельную функцию. При этом наименьший порог срабатывания дискриминатора определяется начальным кодом, установленным на счетчике.

Указанные изменения в структуре многопорогового логического элемента позволяют повысить его технологичность и точность за счет исключения из его с;семы цепи последовательно включенных резисторов, определяющих пороги срабатывания дискриминатора, а также за счет того, что в дискриминаторе используетси только однй логический элемент -HE.

Кроме того, расширяются функциональные возможности предложенного элемента, поскольку он позволяет реализовать нес колько различных переключательных функций, число которых равно числу порогов в многопороговом логическом элементе.

Ф ормула из обре тен ия

Многопороговый логический элемент, содержащий линейный сумматор, состоящий из входных диодов, резисторной матрицы и разделительных диодов, выход линейного сумматора подключен к первому входу логического элемента И-НЕ, образующего дискриминатор, и весовые резисторы, отл ичающ ийся тем, что, с целью расширения функциональных возможностей, повышения технологичности и точности при большом числе порогов, он дополнительно содержит суммирующйй

7 936427 8 счетчик, дешифратор и элемент И, выход щих импульсов, выходы суммирующего которого соединен с выхолной клеммой счетчика соединены с соответствующими многопорогового логического элемента, входами дешифратора. первый вход элемента И соединен с выходом логического элемента И-НЕ и со Источники информации, счетным входом суммирующего счетчика, принятые во внимание при экспертизе второй вход подключен к выходу младше- 1. Авторское свидетельство СССР го разряда суммирующего счетчика, вы- M 608266, кл. Н 03 К 19/42, ходы дешифратора через весовые резио- 06.07.76. торы подключены к первому входу логи- ð .2, Авторское свидетельство СССР ческого элемента -HE, второй вход1 Мо 538490, кл. Н 03 К 19/12, которого соединен с клеммой тактирую- 24. 11.75. г

Составитель Н. Дубровская

Редактор И. Ми;гровка ТехредЛ.Пекарь Корректор Ю, Макаренко

\ Ве М Ю ° и

Заказ 4258/76 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4