Формирователь сигнала цифровой следящей развертки

Иллюстрации

Показать всеРеферат

(72) Автор изобретея11я

Ю. И Попашенко (71) Заявятель (54) ФОРМИРОВАТЕЛЬ СИГНАЛА ЦИФРОВОИ

СЛЕДЯЦЕЙ РАЗВЕРТКИ

Изобретение относится к телевиде нию и может использоваться в телевизионных измерительных и следящих системах, использующих передающие телевизионные трубки без накопления зарядов.

По основному авт. св. У 692lll известен формирователь сигнала цифровой следящей развертки, в котором коррекция сигнала развертки обеспечивается смещением растра на фотокатоде передающей трубки синхронно с колебаниями относительно ее проекции объекта. Формирователь содержит сумматор кодов, на первый вход которого поступает код с регистра развертки, а на второй - код поправки, пропорциональный мгновенному смещению проекции объекта. Результирующий код переносится на регистр памяти, свя- 2о занный с цифроаналоговым преобразователем, выход которого через усилитель соединен с отклоняющей катушкой (1).

Недостатком данного формирователя является введение кода поправки только в моменты времени поступления тактовых импульсов, что снижает эффективность.коррекции при высоких относительных скоростях перемещения проекции объекта (когда за период повторения тактовых импульсов перемещение проекции объекта равно или больше половины размера проекции апертуры), Цель изобретения — повышение эффективности коррекции при высоких отсительных скоростях перемещения проекции объекта.

Указанная цель достигается введением в совокупность признаков формирователя последовательно соединенных инвертора, триггера с раздельными входами и первого элемента И, включенных между четвертым выходом блока эадвржки и входом регистра развертки, причем второй вход первого элемента И соединен с первым выходом блока задержки, последовательно соезаписи второго слагаемого сумматора

4 кодов и на вход разрешения записи дополнительного регистра 11 памяти, при этом в.сумматор 4 кодов и в дополнительный регистр памяти переносится значение кода поправки с анаI лого--цифрового преобразователя 3, и в сумматоре 4 кодов производится операция алгебраического сложения кодов координаты и поправки. С четвертого выхода блока 9 задержки задержанные на 3Т тактовые импульсы поступают на вход разрешения записи

3 93645 диненных дополнительного регистра памяти, цифрового компаратора, второго элемента И, на второй вход кото-. рого поступают мультитактовые импульсы, элемента ИЛИ, включенного между третьим выходом блока задержки и его входом, а также дополнительного блока задержки, подключенного "к второму входу элемента ИЛИ, причем вход дополнительного блока щ задержки и второй вход триггера с раздельными входами подключены к входу тактовых импульсов, при этом четвертый выход блока задержки соединен с вторым входом первого регистрд памяти, выход триггера с раздельными входами - с третьим входом второго элемента И, а вторые входы дополнительного регистра памяти и цифрового компаратора соединены с выходом аналого"цифрового преобразователя.

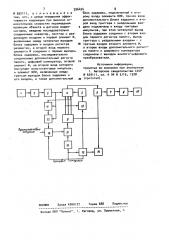

На чертеже показана блок-схема устройства.

Формирователь содержит датчик 1 угловых перемещений, фазочувствитель- >> ный амплитудный детектор 2, аналогоцифровой преобразователь 3, сумматор 4 кодов, регистр 5 развертки, первый регистр 6 па;-яти, цифроаналовый преобразователь 7, усилитель

8 сигнала развертки, блок 9 задержки, отклоняющую катушку 10, дополнительный регистр 11 памяти, цифровой компаратор 12, первый элемент И 13, инвертор 14, триггер 15 с раздельными входами, второй элемент И 16, эле; мент ИЛИ 17, дополнительный блок 18 задержки.

Формирователь работает следующим образом.

Мгновенное значение угла наклона платформы по данной координате измеряется датчиком 1 угловых перемещений, сигнал которого демодулируется фаэочувствитепьным амплитудным детектором 2 и преобразуется в код поправки аналого-цифровым преобразователем 3, выход которого соединен со входом второе слагаемое сумматора

4 кодов, входом дополнительного регистра памяти 11 и первым входом цифрового компаратора 12. Вход первое слагаемое сумматора 4 кодов соединен с выходом регистра 5 развертки. На каждом шаге развертки, соответствующем изменению кода регистра развертки на единицу младшего разряда, в сумматоре кодов 4 производится алгебраическое (с учетом знака

4 4 поправки) сложение кода координат регистра 5 развертки с кодом поправки отклонения аналого-цифрового преобразователя 3. На счетный вход ре гистра 5 развертки, соединенный с входом установки нуля сумматора 4 кодов, через блок 9 задержки и первый элемент И 13 поступают тактовые импульсы с выхода элемента ИЛИ 17, задержка этих импульсов относительно импульсов на выходе элемента ИЛИ 17 равна нулю. Тактовые импульсы устанавливают в нуль сумматор 4 кодов и продвигают на единицу младшего разряда регистр 5 развертки. С второго выхода блока 9 задержки тактовые импульсы, задержанные на время

Т, поступают на вход разрешения записи первого слагаемого сумматора

4 кодов, при этом текущий код координаты с регистра 5 развертки переносится в сумматор 4 кодов. С третьего выхода блока 9 задержки задержанные на время 2Т тактовые, иипульсы поступают на вход разрешения первого регистра 6 памяти и на вход инвертора 14, разрешая запись в первый регистр памяти кода результата с выхода сумматора 4 кодов и устанавливая триггер 15 с раздельными Входами в состояние логического нуля.

Величина времени задержки Т должна быть достаточной для окончания переходных процессов в сумматоре 4 кодов.

Таким образом, при каждом шаге развертки положение проекции апер- туры на фотокатоде диссектора определяется как кодом регистра 5 развертки, так и коДом поправки отклонения аналого-цифрового преобразователя 3, которые суммируются с учетом знака кода поправки отклонения.

936454 6

8 промежутке между тактовыми импульсами текущее значение кода поправки на выходе аналого-цифрового преобразователя 3 сравнивается со значением кода поправки, записанным .в дополнительный регистр 11 памяти при определении кода перемещения апертуры в предыдушем такте, цифровым компаратором 12. Если разность текущего и запомненного значений 10 кора поправки превышает по модулю заданную величину, то выходной сигнал цифрового компаратора изменится с запрещающего на разрешающий для второго элемента И -16. Поскольку на 1S втором входе управления второго элемента И 16, соединенном с инверсным выходом триггера 15 с раздельными входами, также имеется разрешающий потенциал (поскольку триггер щ установлен в нуль на последнем эта.пе формирования кода смещения апертуры), мультитактовый импульс пройдет через элемент И 16 и элемент

ИЛИ 17 на вход блока 9 задержки и zs произведет описанные выше для тактоеого импульса операции: установку в нуль сумматора кодов, запись в сумматор кода регистра развертки, запись в сумматор кода поправки и за- зо пись результирующего кода в первый регистр 6 памяти, а также подтверждение нулевого состояния триггера

15 с раздельными входами. Но опера ция обновления кода на регистре 5 развертки не будет выполнена мульти тактовым импульсом, поскольку на втором входе первого элемента И 13. имеется запрещающий потенциал с прямого выхода триггера с раздельными входами 15, и мультитактовый импульс через первый элемент И 13 не проходит. Обновленное значение кода поправки одновременно с записью в сумматор 4 также записывается в до45 полнительный регистр памяти 11, что вызывает изменение выходного сигнала цифрового компаратора 12 с разрешающего на запрещающий. Прохождение последующих мультитактовых импульсов через второй элемент И 16 запрещается и схема находится в состоянии ожидания, сохраняющемся либо до: прихода очередного тактового импульса, либо до момента изменения кода по правки отклонения на заданную величи- 5 ну относительно записанного в дополнительный регистр 11 памяти значения.

3а счет введения обновленного значения кода поправки отклонения не обусловлено моментом поступления очередного тактового импульса, а производится в каждый момент времени, когда разность между введенным значением кода поправки и его текущим значением превышает заданную величину, предлагаемый. формиро-. ватель обеспечивает более эффективную коррекцию положения апертуры при высоких относительных;скоростях перемещения проекции объекта.

Для того, чтобы процессы формирования кода положения апертуры, вызы ваемые тактовыми и мультитактовыми импульсами, не перекрывались во времени, введен дополнительный блок

18 задержки, вход которого соеди- нен со входом установки единицы триггера 15 с раздельными входами,. а выход — со вторым входом элемента ИЛИ 17. Дополнительный блок 18 задержки осуществляет задержку тактового импульса на время 3Т. Если тактовый импульс приходит со сдвигом по времени относительно мультитактового импульса, вызвавшего формирование обновленного значения кода положения апертуры, меньшим 3Т, то, установив триггер 15 с раздельными входами в положение единицы, он запрещает прохождение последующих мультитактовых импульсов через элемент И 16 и одновременно разрешает прохождение выходного импульса блока

9 задержки через первый элемент И 13 на счетный вход регистра 5 развертки. Через интервал времени 3Т, на котором закончится процесс формирования кода положения апертуры, вызванный приходом мультитактового импульса, тактовый импульс поступает с выхода дополнительного блока 18 задержки через элемент ИЛИ 17 на вход блока 9 задержки и вызывает новый процесс формирования кода положения апертуры.

Таким образом, исключается совмещение во времени одного и другого процесса формирования кода положения апертуры, т.е. наличие сигналов разрешения одновременно на двух входах управления сумматора кодов, приводящее к неоднозначности выходного кода сумматора. формула изобретения формирователь сигнала цифровой следящей развертки по авт. св.

936454

ВНИИПИ Заказ 4260/77 Тираж 688 Подписное филиал ПНП "Патент", г. Ужгород, ул. Проектная, 4

11 692111, отличающийся тем, что, с целью повышения эффективности коррекции при высоких относительных скоростях перемещения проекции объекта и датчика видеосигнала, введены последовательно соединенные инвертор, триггер.с раздельными входами и первый элемент И, включенные между четвертым выходом блока задержки и входом регистра развертки, а второй вход первого элемента И соединен с первым выходо блока задержки, последовательно соединенные дополнительный регистр памяти, цифровой компаратор, второй элемент И, на второй вход которого поступают мультитактовые импульсы, и элемент ИЛИ, включенНые между третьим .выходом блока задержки и

его входом, а также дополнительный блок задержки, подключенный к второму входу элемента ИЛИ, причем вход дополнительного .блока задержки и второй вход триггера с раздельными вхо$ дами подключены к входу тактовых импульсов, при этом четвертый выход блока задержки соединен с вторым входом первого регистра памяти, выход триггера с раздельными входами - с

<4 третьим входом второго элемента И, а вторые входы дополнительного регистра памяти и цифрового компаратора соединены с выходом аналого-цифрового преобразователя.

Источники информации, принятые во .внимание при экспертизе

1. Авторское свидетельство СССР

N 629111 кл. Н 04 N 3/16, 1978 (прототип).