Устройство для измерения временных параметров бега

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()936950

Союз Советских

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 24.01.80 (21) 2874025/28-12 с присоединением заявки №вЂ” (23) Приоритет— (51) M K, з

А 63 В 69/00

G 07 С 1/00

Гееударетееиимй июмнтет (53) УДК 685.6 (088.8 ) Опубликовано 23.06.82. Бюллетень № 23

Дата опубликования описания 23.06.82 ло делам изееретений и открытий (72) Авторы изобретения

М. А. Гладштейн, В. М. Комаров иШ А. Ушаков

Рыбинский авиационный технологический институт (7! ) Заявитель (54) УСТРОЛСТВО ДЛЯ ИЗМЕРЕНИЯ

ВРЕМЕННЫХ ПАРАМЕТРОВ БЕГА

Изобретение относится к устройствам для измерения времени и может быть использовано для регистрации временных параметров бега на спринтерские и стайерские дистанции.

Известно устройство для измерения временных параметров бега, содержащее стартовый пистолет, стартовые колодки и блок фотофиниша (1) .

Недостатками устройства являются низкая точность обусловленная использованием электромеханических секундомеров и реле, и узкие функциональные возможности, заключающиеся в малом количестве контролируемых параметров.

1Яель изобретения — повышение точности и расширение функциональных возможностей.

Поставленная цель достигается тем, что устройство для измерения временных параметров бега, содержащее стартовый пистолет, стартовые колодки и блоки фотофини- шей, имеет пульт управления, разрядные схемы совпадения, схему формирования адреса памяти, RS-триггер, последовательно соединенные кварцевый генератор, делитель частоты, счетчик, оперативное запоминаю2 щее устройство и десятичный индикатор времени и последовательно соединенные первый, второй и третий регистры входы синхронизации которых подключены к второму выходу делителя частоты, а входы первого регистра соединены с чувствительными элементами стартовых колодок и фотофинишей причем к первым входам разрядных схем совпадения подключены соответ твующие прямые выходы второго регистра, а к вторым— соответствующие инверсные выходы третьего регистра, первые входы схемы формирования адреса памяти соединены с выходами разрядных. схем совпадения, а первый выход — с входом оперативного запоминающего устройства, выход пульта управления соединен с вторым входом схемы формирования адреса памяти, выход RS-триггера соединен с входами сброса счетчика и делителя частоты R-вход соединен с вторым выходом схемы формирования адреса памяти и входом сброса первого регистра, а S-вход — с выходом чувствительного элемеита стартового, пистолета.

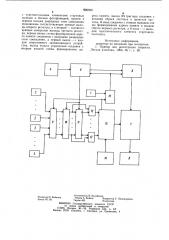

На чертеже представлена структурная схема устройства для измерения временных параметров бега.

936950

Устройство содержит стартовый пистолет I, стартовые колодки 2, блоки фотофинишей 3, последовательно соединенные кварцевый генератор 4, делитель 5 частоты, счетчик

6, оперативное запоминающее устройство 7 и десятичный индикатор 8 времени, последовательно соединенные первый 9, второй

10 и третий 11 регистры, входы синхронизации которых подключены к второму выходу делителя 5 частоты, а входы первого регистра 9 связаны с выходами стартовых колодок 2 и фотофинишей 3, разрядные схемы 12 совпадения, к первым входам которых подключены прямые выходы второго регистра 10, а к вторым — инверсные входы третьего регистра 11, схему 13 формирования адреса памяти, первые входы которой соединены с выходами разрядных схем !2 совпадения, а первый выход — с входом адреса оперативного запоминающего устройства 7, пульт 14 управления выход которого соединен с вторым входом схемы 13 формивания адреса памяти, RS-триггер 15, выход которого соединен с входами сброса счетчика 6 и делителя 5 частоты, R-вход — со вторым выходом схемы 13 формирования адреса памяти и входом сброса первого регистра 9, а

S-вход — с выходом стартового пистолета 1.

Устройство работает следующим образом

Сигнал, формируемый стартовым пистолетом 1, в момент выстрела устанавливает RS-триггер 15 в единичное состояние, разрешая, тем самым, работу делителя 5 частоты и счетчика 6. Через интервалы времени, определяемые требуемой точностью измерения необходимых параметров, на вход счетчика б с выхода делителя 5 частоты поступают импульсы, фиксируемые счетчиком 6.

Таким образом, состояние счетчика 6 фиксирует с требуемой точностью измеряемые интервалы времени. В момент окончания интервалов времени, представляющих собой измеряемые параметры (времена отрыва от стартовой колодки руки, ноги, пробега определенного отрезка дистанции и т.д.), очувствленные стартовые колодки 2 или фотофиниши 3, подключенные к первым входам первого регистра 9, формируют сигналы, фиксируемые им. Таким образом, состояние первого регистра 9 в текущий момент времени однозначно соответствует сработавшим стартовым колодкам или фотофинишам 3.

Изменение состояния первого регистра 9 фиксируется вторым регистром 10 в ближайщий полупериод измеряемого дискретного времени, что обеспечивается использованием двойной тактовой частоты (по отношению к частоте .сигнала, поступающего на вход счетчика 6) для его синхронизации.

В результате этого между состояниями второго 10 и третьего 11 регистров возникает рассогласование в соответствующем разряде, что вызывает появление сигнала на выходе соответствующей разрядной схемы 12 совпадения. По этому сигналу схема 13 фор5

Зо

55 мирования адреса памяти формирует адрес ячейки оперативного запоминающего устройства 7 и состояние счетчика 6, представляющее собой значение измеренного интервала времени, записывается в ячейку оперативного запоминающего устройства 7, соответствующую сработавшему датчику. Моменты Записи информации в оперативное запоминающее устройство 7 и изменения состояния счетчика 6 разнесены во времени, что обеспечивает безошибочную запись информации. По истечении следующего полупериода дискретного времени состояние второго регистра 10 переписывается в третий регистр

ll, что устраняет рассогласование между их состояниями и прекращает запись информации в оперативное запоминающее устройство 7.

Аналогичным образом происходит фиксация и запись в оперативное запоминающее устройство 7 всех измеряемых параметров, за исключением последнего.

При срабатывании последнего датчика (как правило, фотофинаша 3) хема 13 формирования адреса памяти, кроме адреса соответствующей ячейки оперативного запоминающего устройства 7, формирует сигнал, устанавливающий RS-триггер 15 и первый регистр 9 в начальное состояние. Сигналом с выхода RS-триггера 15 обнуляется делитель 5 частоты и счетчик б и устройство подготавливается к новому циклу работы.

Значения параметров, измереннь.х в окончившемся этапе тренировки спортсмена, храняться в ячейках оперативного запоминающего устройства 7. Эти значения по сигналам с пульта 14 управления могут быть выведены из оперативного запоминающего устройства 7 на десятичный индикатор 8 времени для их контроля.

Использование предлагаемого изобретения позволяет повысить точность измерения временных параметров бега и увеличить их количество, что ведет в конечном итоге, к повышению эффективности тренировок.

Формула изобретения

Устройство для измерения временных параметров бега, содержащее чувствительные элементы, расположенные на стартовых колодках и на стартовом пистолете, блоки фотофинишей, отличающееся тем, что, с целью повышения точности, оно имеет пульт управления, разрядные схемы совпадения, схему формирования адреса памяти, RS-триггер, последовательно соединенные кварцевый генератор, делитель частоты, счетчик оперативное запоминающее устройство и десятичный индикатор времени и последовательно соединенные первый, второй и третий регистры, входы синхронизации которых подключены к второму выходу делителя частоты, а входы первого регистра соединены

936950

Составитель В. Балабанов

Техред А. Бойкас Корректор У. Пономаренко

Тираж 400 Подписное

ВНИ И ПИ Государственного комитета СССР по делам изобретений н -открытий

113035, Москва, K — 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4

Редактор Н. Бобкова

Заказ 4111/6

5 с чувствительными элементами стартовых колодок и блоков фотофинишей, причем к первым входам разрядных схем совпадения подключены соответствующие прямые выхо.— ды второго регистра, а к вторым — соответствующие инверсные выходы третьего регистра, первые входы схемы формирования адреса памяти соединены с выходами разрядных схем совпадения, а первый выход — с входом оперативного запоминающего устройства, выход пульта управления соединен с вторым входом схемы формирования ад6 реса памяти, выход RS триггера соединен с входами сброса счетчика и делителя частоты, R-вход соединен с вторым выходом схемы формирования адреса памяти и входом сброса первого регистра, а S-вход — с выходом чувствительного элемента стартового пистолета.

Источники информации, принятые во внимание при экспертизе

1. Прибор для регистрации скорости.

Легкая атлетика, 1969, № 1, с. 28.