Устройство для амплитудного анализа импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистическими

Республик ю938176 (61) Дополнительное к авт. свид-ву (22)Заявлено 22.12.80 (21) 3223919/18-21 с присоединением заявки И (23)Приоритет (5! )М. Кл.

G О1 R 19/04

Гееударстевниый комитет

СССР ве аелам изобретений и открытий (53) УДК621..31У, 7(088.8) Опубликовано 23.06.82. Бюллетень № 23

Дата опубликования OAHcBHHQ 25.06 .82 (72) Автор изобретения

А. И. Шамов

Ф (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ АМПЛИТУДНОГО АНАЛИЗА

ИМПУЛЬСОВ

Изобретение относится к электроизмерительной технике и предназначено для использования в амплитудных анализаторах, обеспечивающих, в частности, отбор импульсов по амплитуде с детектора ядерных излучений.

Известно устройство для измерения импульсных сигналов, содержащее первичный электрический преобразователь, выход которого через фильтр нижних частот и многоотводную линию задержки подключен к аналого-цифровому пре" образователю, блок вычисления конечных разностей, входы которого соединены с отводами линии задержки, а вы-т5 ход — с входом блока вычисления дисперсий конечных разностей и с одним из входов блока запуска, усилитель, установленный между выходом блока вычисления дисперсий конечных разнос- го тей и другим входом блока запуска, формирователь Фиксированного временного интервала, вход которого подключен к выходу блока запуска, а выход— к входу блока управления, блок памяти информации, информационный вход которо го соеди не н с выходом ан алогоцифрового преобразователя, а управляющий вход — с выходом блока управления 11 j.

Известное устройство позволяет осуществлять воспроизведение общей формы импульсного сигнала, в том числе и его амплитуды. Однако использование для подобного воспроизведения значительного рора дискретных отсчетов сигнала предопределяет крайне низкое быстродействие подобного устройства.

Еще один его недостаток связан с весьма ограниченной областью практического применения.

Наиболее близким техническим решением является устройство для амплитудного анализа импульсов, содержащее компаратор, первый вход которого соединен с входной шиной, а второй и третий входы — с выходами основного и дополнительного преобразователей

3 93817 код-аналог, блок управления, запускающий вход которого подключен к входной шине, переключающий вход - к выходу компаратора, а синхронизирующий вход - к шине синхроимпульсов, регистр адреса, вход которого соединен с выходом блока управления, а одна из групп выходов - с входами основного преобразователя код-аналог, дополнительный регистр, выход которого под- 0 ключен к входу дополнительного преобразователя код-аналог, сумматор, входы которого соединены с другой группой выходов регистра адреса и выходом масштабирующего блока, связан- .1з ного с генератором импульсов, а выход - с входом блока памяти информации (2).

Недостатки указанного устройства связаны с существенной инерционностью измерения и неприемлемыми в ряде случаев погрешностями контроля.

Цель изобретения - повышение быстродействия и точности измерительного устройства.

Поставленная цель достигается тем, что в устройство для амплитудного анализа импульсов, содержащее компаратор, первый вход которого соединен с входной шиной, а второй и третий входы — с выходами основного и дополнительного преобразователей код-аналог, блок управления, запускающий вход которого подключен к входной шине, переключающий вход - к выходу ком- паратора, а синхрониэирующий вход - к шине синхроимпульсов, регистр адреса, вход которого соединен с выходом блока управления, дополнительный регистр, 40 выход которого подключен к входу дополнительного преобразователя коданалог, сумматор и блок памяти информации, введены блок памяти пороговых выборок, триггер группирования и блок совпадения, причем адресные входы бло- ка памяти пороговых выборок и блока памяТи информации соединены с информационными выходами регистра адреса,, вход триггера группирования подключен к управляющему выходу регистра адреса, один из выходов - к управляющему входу блока памяти пороговых выборок, а другой выход - к первому входу блока совпадения, второй вход блока совпадения соединен с выходом компаратора, >> третий вход - с шиной синхроимпульсов, а выход — с входом дополнительного регистра и счетным входом блока

6 ф памяти информации один из входов сумматора подключен к выходу блока памяти пороговых выборок, другой входк выходу дополнительного регистра, а выход - к входу основного преобразователя код-аналог.

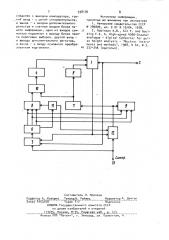

На чертеже представлена Функциональная схема предложенного устройства для амплитудного анализа импульсов.

В устройство входят компаратор 1, связанный с входной шиной 2, блок 3 управления, основной 4 и дополнительный 5 преобразователи код-аналог, регистр 6 адреса, дополнительный регистр 7, блок 8 памяти пороговых выборок, блок 9 памяти информации, сумматор 10, триггер 11 группирования, блок 12 совпадения, связанный, как и блок 3 управления, с шиной 13 синхроимпульсов.

Устройство работает следующим образом.

До начала анализа первого импульса в дополнительном регистре 7 3anv— ан "0", сигнал на входе дополнитель ного преобразователя код-аналог имеет начальное значение. Перед анализом каждого входного импульса триггср 11

;руппирования находится в таком состоянии, что запирает блок 12 совпадения и выбирает ту часть памяти в блоке 8 памяти пороговых выборок, в которой записаны верхние пороги всех цифровых окон.

При появлении анализируемого импульса на входной шине 2 запускается блок 3 управления, который с частотой синхроимпульсов опрашивает регистр 6 адреса. Последний управляет выборкой чисел из блока 8 памяти пороговых выборок. Вначале за каждый такт опроса регистр 6 адреса выбирает из блока 8 цифровой код верхнего порога одного из цифровых окон, который появляется на соответствующем входе сумматора 10. При этом на выходе сумматора 10 имеет место тот же код, поскольку на другом его входе присутствует код, соответствующий "0", записанному в дополнительном регистре 7.

На выходе основного преобразователя код-аналог 4 появляется сигнал, соответствующий этому коду. На компараторе 1 происходит его сравнение с входным сигналом. Если входной сигнал превышает верхний порог цифрового окна, то на выходе компаратора 1 формируется сигнал, разрешающий переключение блока 3 управления и запоминаФормула изобретения

Устройство для амплитудного анализа импульсов, содержащее компаратор, первый вход которого соединен с входной шиной, а второй и третий входыс выходами основного и дополнительного преобразователей код-аналог, блок управления, запускающий вход которого подключен к входной шине, переключаю щий вход — к выходу компаратора, а синхрониэирующий вход — к шине синхроимпульсов, регистр адреса, вход ко- . торого соединен с выходом блока управления, дополнительный регистр, выход которого подключен к входу дополнительного преобразователя код-ана- лог, сумматор и блок памяти информации, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и точности, в него введены блок памяти пороговых выборок, триггер группирования и блок совпадения, причем адресные входы блока памяти пороговых выборок и блока памяти информации соединены с информационными выходами регистра адреса, вход триггера группирования подключен к управляющему выходу регистра адреса, один из выходов — к управляющему входу блока памяти пороговых выборок, а другой выход - к первому входу блока совпадения, второй вход блока совпадения

5 9381 ние в регистре 6 адреса следующего цифрового окна. Этот же сигнал по соот ветст вующему входу под гот а вливает к отпиранию блок 12 совпадения. Однако по второму .входу блок 12 совпадения закрыт сигналом с триггера 11. На выходе блока 8 памяти пороговых выборок появляется код верхнего порога этого окна и соответственно меняется сигнал на выходе преобразователя Iî код-аналог 4. Далее опять происходит его сравнение с входным сигналом на компараторе 1.

Цикл повторяется до тех пор, пока не будет выбран соответствующий анализируемому импульсу ближайший верхний порог. Тогда на выходе компаратора 1 появляется сигнал запрета, который запирает по соответствующему входу блок 12 совпадения. На управляющемр0 выходе регистра 6 адреса появляется сигнал, перебрасывающий триггер 11.

Последний выбирает таперь в блоке 8 памяти пороговых выборок нижние пороги цифровых окон и подготавливает к И отпиранию блок 12 совпадения по своему входу °

В следующем цикле происходит выбор нижних порогов цифровых окон таким же образом,как и в первом случае. Зо

На компараторе 1 сравнивается сигнал с выхода основного преобразователя код-аналог 4 с входным импульсом. Если входной импульс превышает нижний порог, т. е. не соответствует

35 выбранному окну, то на выходе компаратора 1 появляется сигнал разрешения, отпирающий блок 12 совпадения.

Синхроимпульс проходит на счетный вход блока 9 памяти информации и записывается в канале, соответствующем выбранному дифференциальному цифровому окну. Импульс с выхода блока 12 совпадения поступает на счетный вход дополнительного регистра 7 и переключает его. На выходе дополнительного преобразователя код-аналог 5 появляется сигнал, соответствующий записанному в дополнительном регистре 7 коду. Этот сигнал вычитается из

50 сигнала на выходе основного преобра зователя код-аналог 4. Цифровой сигнал с выхода дополнительного регистра 7 складывается с сигналом выбранного цифрового порога с выхода блока 8 памяти пороговых выборок. На вы55 ходе основного преобразователя коданалог 4 появляется сигнал, соответствующий их сумме. На компараторе 1

76 6 сигналы с основногс 4 и дополнительного 5 преобразователей код-аналог вычитаются. Результирующий эффективный сигнал соответствует коду выбранного цифрового порога. При этом происходит сдвиг шкалы устройства при работе с цифровыми окнами.

Следующие циклы анализа происходят аналогично. После очередного анализа в дополнительный регистр 6. записывается единица, за счет чего происходит очередной сдвиг шкалы.

Таким образом, предложенное устройство позволяет непосредственно накапливать информацию в блоке памяти информации при выбранных цифровых дифференциальных окнах, что положительно сказывается на быстродействии устройства. Сдвиг шкалы обеспечивает высокую дифференциальную линейность задания цифровых окон, что, в свою очередь, обусловливает повышенную точность анализа.

938176

Составитель Л. Морозов

Редактор А. Козориз Texpe8М. Рейвес

Заказ 4453/68 Тираж 717

ВНИИПИ Государственного комитета по делам изобретений и открыти

113035 .Москва 8-35 Раушская наб.

Корректор А. Дзятко

Подписное

СССР и, д. 4/5

О филиал ППП "Патент", г. Ужгород, ул. Проектная, соединен с выходом компаратора, тре.. тий вход — с шиной синхроимпульсов, а выход -. с входом дополнительного регистра и счетным входом блока памяти информации, один из входов сум- 5 матора подключен к выходу блока памяти пороговых выборок, другой входк выходу дополнительного регистра, а выход - к входу основного преобразователя код-аналог. ,1О

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 789809, кл. G 01 R 19/04, 1978.

2. Robinson К.В., Gin F. апд Goulding F.S. А. High-speed 4096-Chaunel

analogue - digital Converter for pulse height analysis - "Nuclear instruments and methods", 1968, N 62, N 3, 237-246 (прототип).