Устройство для считывания информации из матричного накопителя

Иллюстрации

Показать всеРеферат

О Il И С А Н И Е (11)938315

ИЗОБРЕТЕНИЯ

К - АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Рес ублык (6I ) Дополнительное к авт. свил-ву М 767834 (22) Закалено 27.04.79 (2I )2759504/18-24 с присоелкиением заявки М (23) Приоритет—

Опубликовано 23,06,82, бюллетень,% 23

Дата опубликования описания 27.06.82 (Бl)М. Кл.

11 С 7lOO еееукерстеехный кемытет

СССР йе делам язееретеннй и открытка (53) УДК 681.

° 327.67 (088.8) В ° Q. Глушксв, А. Г. Жемейцев и В. А. МилошенсКйй»---=-:,, (72) Ааторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ

ИЗ МАТРИЧНОГО НАКОПИТЕЛЯ

Изобретение относится к вычислитем ной технике и может быть использовано при построении интегральных постоянньк запоминающих устройств..

Известно устройство для считывания информации, содержащее два дешнфратора, транзисторы выборки, а также запоминающие элементы, организованные в инде матрицы (1).

Однако это устройство отличается не- ® высоким быстродействием.

Известно устройство для считывания информации из матричного накопителя, содержащее информационные транзисторы, организованные в матрицу, а также транt5 эисторы, соединявшие информационные транзисторы с выходом разрядной шины и вынолняющие функции ключей (21.

Недостатком устройства является невысокое быстродействие.

По основному авт. св. М 767834 известно устройство содержащее информационные транзисторы, дешифрато. ры строк и столбцов, ключевые тран2 знсторы, элемент задетекки и шунтнруюший транзистор, при атом затворы инфорьмационных транзисторов, распопсекениык Ь каждой строке, объединены между собой н подключены к выходам дешнфратора строк, истоки всех информационньск тран» эисторов объединены и подкачены к пе не источника питания, стоки информационных транзисторов, располакенньа в ês2sдом столбце, объединены и подключены а истоку соответствутошего ключевого траи»

Bsc1 ора, затворы ключевых транаесторов" соединены с вьаодаьае дапатфратофа столтт цов, а стоки объединены и подключены к шине считывания сток шунтидлюаего транзистора также подключен к шине счвтывания исток к шине живого потец» циала, а затвор - через элемент аадерк ки к шине выборки (Э .

Потенциал всех строк с подключенными к ним затворами информкдианнье транмоторса изменяется от О до Е (Е - напряжение источника питании) и обратно с той же частотой,, с какой происходит обраце. транзисторы открыты, поццерживая тем самым потенциалы истоков ключевых транзисторов близкими к аЕ. При обращении к запоминающему устройству нулпsoN потенциал поцается на шину 27. По прихопу нулевого потенциала на шину выборки потенциалы выбранных выходов цешифраторов 17 и 18 понижаются цо 0, а потенциалы остальных выходов цешифраторов не изменяются. В результате это, го ключевой транзистор, поцключенный к выбранному выхопу цешифратора 18, открывается. Вместе с тем потенциал затворов цополнительных транзисторов повышается цо +Е, закрывая их. При этом, если на пересечении выбранных строки и стол6ца отсутствует информационный транзистор (что соответствует нулю двоичной информации), то емкость выбранного столбца разряжается через открытый ключевой транзистор, причем в течение времени один разряд идет на шину нулевого потенциала через открытый транзистор 20, и в это время шина 26 имеет потенциал, близкий к О, а в остальное время после закрывания трачэистора 20 оставшийся на шине заряц перераспрецеляется межпу емкостями. Вре мя выбирается таким, чтобы í апряжение на шине 26 в конечном счете не достигало порога срабатывания выходной схемы. Если же на пересечении выбранных строки и столбца матрицы имеется информационный транзистор (что соответствует единице двоичной информации), то, он открыт и протекающий через него ток стремится сохранить потенциал +Е на емкости.

Кроме того, транзистор обеспечивает поступление тока на шину 26 считывания.

Через время Т после начала обращения к ЗУ транзистор 20 закрывается, после чего начинает повышаться потенциал на шине 26 и по достижении величины порога срабатывания выходной схемы последняя срабатывает, завершая процесс считывания информации из запоминающего устройства. После этого на шину 27 подается потенциал .Е, что привош т к открыванию заряжающих транзисторов 2225 и шунтируюшего транзистора 20, а также к повышению потенциалов двух выходов дешифраторов, бывших выбранными в рассмотренном цикле считывания. Через . открытые заряжающие и шунтируюший транзисторы соответственно потенциал шины понижается цо О, а потенциал стоков заряжающих транзисторов повышаются до +Е.

Анализ работы устройства показывает, что время выборки информации (от мо3 9383 15 ние к ЗУ, что приводит к опрецеленным лагерям мощности, затрачиваемой на переэаряд емкостей строк в каждом цикле обращения. Кроме того, tro окончании считывания информации перед тем, как осуществить новое обращение к ЗУ, ненеобходимо повысить потенциал стоков всех информационных транзисторов, что осуществляется через открываемые цля этого информационные транзисторы. Мак- 1р симальное время, необходимое для tronзаряда стоков информационных транзисторов, имеет место в случае, когда в столбце находится лишь один транзистор, Раэмеры информационных транзисторов ограничены по известным причинам. Поэтому для заряда стоков этих транзисторов по окончании считывания информации требуется значительное время, что удлиняет цикл работы ЗУ, уменьшая тем самым его

20 быстродействие.

Бель изобретения — уменьшение потребляемой мощности и увеличение быстроде йствия.

Поставленная цель достигается тем, 23 что в устройство для считывания информации иэ матричного накопителя введены инвертор и элементы подзаряда на дополнительных транзисторах, истоки которых подключены к шине питания, затворы -к выходу инвертора, вход которого поцклю30 чен к шине выборки, а сток каждого дополнительного транзистора — к истоку соответствующего ключевого транзистора.

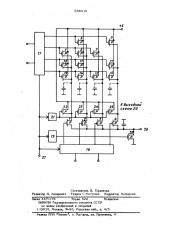

На чертеже приведена схема предлагаемого устройства.

3S

Устройство содержит ключевые транзисторы 1-4, информационные транзисторы 5-16, цешифраторы 17 и 18, элемент

19 задержки, шунтирующий транзистор

20, а также инвертор 21 и элементы под- Э заряда на дополнительных транзисторах

222 5 .

Информационные транзисторы организованы в матрицу 4х4. Например, в пер-вой строке закодирована информация

О 101, во второй — 1110 и т.д.

Предлагаемое устройство работает следующим образом.

При наличии на шине 27 потенциала, близкого к -E потенциалы всех выходов дэшифраторов 17 и 18 и затвора шунтирующего транзистора 20 близки к -Е, а потенциал затворов дополнительных транэисгоров 22-25 близок к О.В результате этого все информационные и ключевые 33 транзисторы закрыты. Шунтируюший транзистор 20 открыт, и потенциал шины 26 считывания близок к О. Все заряжающие

9383 мента срабатывания дешифраторов до срабатывания выхоа ой схемы) осталось таким же, как и в известном устройстве.

Время от окончания считывания информации до момента, когда можно вновь обра- > тнться к данному ЗУ, определяется главным образом временем, в течение которого потенциал стоков всех информационных транзисторов станет бсшэким к

+Е и значительно уменьшено по сравнению с известным устройством эа счет того, что в предлагаемом ЗУ заряд емкостей столбцов после считывания осуществляется пссредством дополнительных транзисторов 22-25, которых много мень- ше, чем ннфсрмационных и которые поэтому могут иметь большую крутизну, чем информационныа транзисторы. Это позволяет значительно сократить время востановления ЗУ, а значит и цикл его работы. Кроме того, при одном этом обращении к предлагаемому устройству потенци- ап swua одной строки матрицы и одной строки дополнительных транзисторов изменяется в пределах от +Е до О н обрат- но, в то время как в известном устройстве в каждом цикле в укаэанньас пределах изменяются потенциалы всех строк магри цы, кроме одной, срабатывают все, кроме одного, каскады дешифратора строк.

Таким образом, при расчете модности в известном устройстве необходмо учитывать потери мощности, вызванные про- . теканием сквозных токов во всех, кроме выбранного, выходных каскадных дешиф

15 d раторах строк, так как каскады эти переключаются дважды при каждом обращении к ЗУ. В предлагаемом же устройстве при каждом обращении срабагываег ,лишь один выходной каскад дешифратора строк.

Таким образом, мощность рассеивания в предлагаемом устройстве существенно меньше, чем в известном.

Ф ор мула и зобре гения

Устройсгво для считывания информации из матричного накопителя по авт. св.

¹ 767834, отличающееся тем, что, с целью повышения быстродеВ- ствия и уменьшения потребляемой мощности, в него введены инвертор и элементы подэаряда на дополнительных транзисторах, истоки которых подкщочены к шине питания, затворы к выходу инвертора, вход которого подключен к шине выборки, а сток каждого дополнительного транзистора —. к истоку соответствующего ключевого транзистора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 523455, кл. Cj 11 С 11/40, 1976.

2. Интегральные схемы на У<ЙП цриборЫ . Пер. с англ. иод ред. А.Н. Кар- мажнского. М., Мир, 1975, с. 439.

3. Авторское свидетем.ство СССР

¹ 767834, кл. Q 11 С 7/00, 1978.

9383 15

Составитель В. Гордонова

Редактор Н. Лазаренко Текред С.Мигунова Корректор М.Шароши

Заказ 4471/74 Тираж 622 По атисное

ВНИИПИ Государственного комитета СССР но делам изобретений и открытий

113О35, Москва, 5, Раушская наб., д. 4/5 г

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4