Устройство для контроля погрешности цифро-аналоговых преобразователей

Иллюстрации

Показать всеРеферат

Союз Советск и«

Социалистически« республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (!! ) 938389 (6! ) Дополнительное к авт. саид-ву (5l)N. Кл.

Н 03 К 13Г . (22)Заявлено 16.06.80 (2!) 2978311/18-21 с присоединением заявки И (23 ) П риоритет

Ртеудврственньй квинтет

CCCP

«е делам «зевратен«й

«вткрыт«й

Опубликовано 23.06.82, Бюллетень,% 23 (53) УДК 681.32. (088.8, Дата опУбликования описания 26.06.82 (72) Автор изобретения

Л. Г. Ходаков ют

/ (7!) Заявитель (5 4) УСТРОЙСТВО ДЛЯ КОНТРС!ПЯ ПОГРЕШНОСТИ

ПИФРО-АНАЛОГОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ!

Изобретение относится к аналого-цифровой вычислительной технике и может быть использовано для контроля цифроаналоговых преобразователей (UAH) при их промышленном производстве, а также в контрольно-проверочной аппаратуре вы5 числительно-управляющих комплексов.

Известно устройство для контроля погрешности ЖП, содержащее группы переключателей, подключаемых к узловым точ10 кам декодирующей резистивной сетки

Й -2Й контролируемого ИАП, блок управления, источник эталонных напряженйй и компараторы (1j .

Недостатком данного устройства явля- т5 ется необходимость подключения групп переключателей к узловым точкам декодирующей реэистивной сетки и -2Й, однако современные интегральные схемы UZI не . имеют выводов узлов декодирующей сетки.гв

Наиболее близким к изобретению по технической сущности является устройст во для контроля погрешности цифро-аналогощйх преобразователей, содержащее ге2 нератор импульсов, счетчик, контролируемый цифро-аналоговый преобразователь, интегратор, источник опорного напряжении, первый аналоговый запоминающий элемент, дифференциальный дискриминатор и вычи тающий усилитель, первый вход которого соединен с выходом контролируемого циф» ро-аналогового. преобразователя, второй вход вычитающего усилителя подключен к информационному входу первого анало» гового запоминакяцего элемента и к вы ходу интегратора, первый вход которого соединен с выходом источника опорного напряжения, выход генератора, импульсов, подключен .к первому входу счетчика, вы ходы которого подключены к цифровым входам контролируемого циерро-аналогово» го преобразователя (21 .

Недостатком известного устройс пиа является необходимость регулировки (подстройки) источников опорного напряжения и напряжения смещения для совмещения пилообразного напряжения иитегратора оо ступенчатым напряжением контролируемоro lIA11. Достигнутая совмещенность характеристик нарушается вследствие дрейфа параметров интегратора и источника напряжения смешения, что снижает достоверность контроля БАП. Погрешность конт;5 ролируемого КАП Ь,, содержит состав ляюшую д, определяемую неточностью совмещения характеристик интегратора и контролируемого ПАП и дрейфом их характеристикк, 30

11ель изобретения - повышение точносI ти контроля погрешности нелинейности преобразователей.

Поставленная пель достигается тем, / что в устройство для контроля погреш",)5 ности цифро-aíàëîãîâûõ преобразователей, содержащее генератор импульсов, счетчик, контролируемый цифро-aíàëîãîâûé преобразователь, интегратор, источник опорного напряжения, первый аналоговый запоминающий элемент, дифференциальный дискриминатор и вычитающий усилитель, первый вход которого соединен с выходом контро- лируемого ðî-аналогового преобразоватеЛя, второй вход вычитающего усилителя 25 подключен к информационному. входу первого аналогового запоминающего элемен та и к выходу интегратора, первый вход которого соединен с выходом источника опорного напряжения, выход генератора импульсов подключен к первому входу счетчика, выхсды которого подключены к тифровым входам контролируемого цнфро-аналогового преобразователи, введены сумматор, второй и третий аналоговые

3S эаноминающие элементы, блок управле= ния н коммутатор, аналоговый вход которого соединен с выходом вычитаюшего усили геля, первый выход коммутатора подключен к выходу дифференциального дискриминатора, второй выход коммутатора соединен с информационным входом третьего аналогового запоминающего элемента, выход которого подключен ко второму входу интегратора, третий выход

45 коммутатора соединен с информационным входом второго аналогового запоминающего элемента, первый вход сумматора подключен к первому выходу первого ана« логового запоминающего элемента, второй вход сумматора соединен с выходом второго аналогового запоминающего элемен- та, выход сумматора подключен к анало говому входу контролируемого шфро-аналогового преобразователя, выходы блока управления соединены с управляющими входами счетчика, интегратора, коммутатора первого, второго и третьего анал<ьговых запоминающих элементов.

3 938389 ф

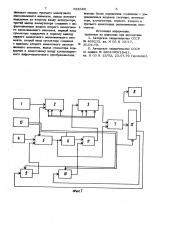

Иа фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие принцип совмещения характеристик интегратора и ПАП.

Устройство для контроля ЦАП содержит генератор 1 импульсов, счетчик 2, контролируемый ЦАП 3, источник 4 опорного напряжения, интегратор 5, аналоговый запоминающий элемент 6, вычитаю щий усилитель 7, дифференциальный дискриминатор 8, первый и второй дополнительные аналоговые запоминающие элементы

9 и 10, сумматор 11, коммутатор 12 и блок 13 упраиления. Выход генератора 1 соединен с первым входом счетчика 2.

Выходы разрядов счетчика 2 соединены с цифровыми входами контролируемого

ПАП 3, выход которого соединен с первым входом вычитаюшего усилителя 7, второй вход которого соединен с выходом интегратора 5.

Первый вход интегратора 5 соединен с источником 4 опорного напряжения, а выход интегратора подключен к первому входу аналогового запоминающего элемен та 6. Выход вычитаюшего усилителя 7 подключен к первому входу коммутатора

12, первый выход которого подключен к входу дифференпиального дискриминатора

8, а два других выхода - к первым входам дополнительных аналоговых эапоми» наюших элементов 9 и 10. Выход перво го дополнительного аналогового запоминающего элемента 9 подключен ко второ му входу интегратора 5, выход второго запоминающего элемента 10 - к первому входу сумматора 11, второй вход которого подключен к выходу основного аналогового запоминающего элемента 6, а выход - к аналоговому входу контролируемого ПАП 3. Вторые входы интегра тора 5, аналоговых запоминающих элементов 6, 9 и 10, коммутатора 12 и счетчика 2 подключены к выходам блока 13 управления.

Работа устройства состоит иэ двух этапов подготовительного и основного (рабочего). В процессе подготовительного этапа блок 13 управления в момент времени t (фиг. 2) устанавливает счеч чик 2 в нулевое состояние,. вследствие чего на выходе контроцируемого ИАП 3 устанавливается напряжение, соответствующее нулевому коду. Соответственно выход вычитаюшего усилителя 7 через коммутатор 12 подключается к первому входу первого дополнительного запоминающего элемента 9, подключенного ко входу интегратора 5. На выходе вычитаюшего

5 9383 усилителя 7 появляется напряжение, со- ответствующее разности нулевого напряжения UAfl 3 и выходного напражения интегратора 5. Вследствие наличия отрицательной обратной связи вычитаюший уси . литель 7 устанавливает на дополнительном запоминающем элементе S напряжение 0 „ которое обеспечивает компенсацию напра

1 жвний смешения и дрейфа 00 интегратора 5, и смешения выходного напряжения ЦАП 3 1е при нулевом коде U An

"О "иНт ЦАП

"Зэ = . <+ K p И где К„- коэффициент передачи ннтеграTopB y

К -коэффициент усиления вычитаюшего усилителя; Ь** 1 коэффициент обратной связи, При значении К 10 10 комненса5 диа обеспечивается.

В момент времени hg (фиг. 2) запус кается счетчик 2, а интегратор 5 начинает интегрировать напряжение источника

4, В момент = (2 - 1) соответствую

O щего наличию всех «1 на цифровых входах ЦАП 3 блок 13 управления формирует сигнал н коммутатор 12 подключает вычитающнй усилитель 7 к первому входу дополнительного запоминающего элемента 10. Основной аналоговый запоминающий элемент 6 подключается к выходу интегратора 5, а счетчик 2 устанавливаетса в единичное состояние. С выхода

UAn 3 поступает напряжение, соответст5 вукяцее полному напряжению UAII при единичном коде на цифровых кодах.

ОU,дп оп* инт ЦАР где К» коэффнпнент передачи инИНТ

° 40 тегра тора;

К1 Ап- коэффициИент передачи БАП.

На выходе второго дополнительного аналогового запоминакядего элемента 10 в течение времени t устанавливается

45 напряжение

Устройство дла контроля погрешности цифро-аналоговых преобразователей, со держащее генератор импульсов, счетчик, контролируемый цифроаналоговый преобразователь, интегратор, источник опорного напряжения, первый аналоговый запоминающий элемент, дифференциальный дискриминатор н вычнтаюший усилитель, первый вход которого соединен с выходом контролируемого цифро-анапогового преобразователя, второй вход вычитаюшего усилителя подключен к информационному входу первого аналогового запоминаю щего элемента и к выходу интегратора, первый вход которого соединен с выходом источника опорного напражения, вы ход генератора импульсов подключен к первому входу счетчика, выходы которого подключены к цифровым входам контроли руемого нифро-аналогового лреобразова тена, о т л и ч а ю m е е с я тем, что, с целью повьппения точности контроля погрешности нелинейности преобразовате-. лей, в него введены сумматор, второй и третий аналоговые запоминакицие элементы, блок управлении и коммутатор, ана логовый вход которого соединен с выходом вычитаквцего усилителя, первый выход коммутатора подключен к выходу дифференциального дискримийатора, второй .выход коммутатора соединен с кнформа0

О lhHT О ийт ц An

ЗэГ 3+kp, Таким образом, на выходе сумматора

1 30

11 устанавливаетса напряжение Don в ре ""и тате чего Qn инт= о инт+ з Кцм что определяет совмещение линейной ха - " рактеристики,интегратора со ступенчатой характеристикой ЦАП. После автоматичес

И кого совмещения граничных точек харак теристик контролируемого ПАП и интегрв . тора начинаетса второй основной этап работы устройства.

89 d

В момент времени t блок 13 управления запускает счетчик 2, а интегратор 5 начинает интегрировать напражение источника 4. Одновременно счетчик 2 управ лает контролируемым КАП 3, который формирует пилообразное напряжение в со ответс твин с напряжением, пас тупакхцим на .его аналоговый вход с выхода сумматора 1 1. Напряжение контролируемого

ЦАП 3 вычитается из пилообразного на. пряжения интегратора 5 с помощью вычитаюшего усилителя 7 и через коммутатор

12, управляемый блоком 13 управления в поступает на вход дифференциального ди скриминатора 8.

Изобретение позволяет повысить точность контроля погрешности БАП и стабильность устройства за счет автоматического совмещении характеристик интет

pampa и контролируемого UAll, исключе ния регулировок при смене образпов контропируемых ЦАП и исключения влияния дрейфов напряженна смещения 0 интегратора и напряжения источника смешениа.

Формула изобретения

9383 цищщым входом третьего аналогового запоминающего элемента, выход которого подключен ко второму входу интегратора, третий выход коммутатора соединен с информационным входом второго аналогово- 5

ro запоминающего элемента, первый вход сумматора подключен к первому выходу первого аналогового запоминающего элемента, второй вход сумматора соединен с выходом второго аналогового запоми. вяющего элемента, выход сумматора подключен к аналоговому входу контролируемого цифро-аналогового преобразователя, 89 8 выходы блока управления соединены с управлякицими входами счетчика, интегратора, коммутатора, первого, второго и третьего аналоговьи запоминающих элементов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

% 469212, кл. Н 03 К 13/17, 30.04. 75.

2. Авторское свидетельство СССР по заявке % 2801093/18-21, кл. Н 03 К 13/02, 23.07.79 (прототип).

Фаа 8

Составитель А. Симагин

Редактор Г. Ус Техред С. Мигунова Корректор. У. Пономаренко

Заказ 4479/78 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-ЗБ, .Рауяская наб., д. 4/5

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4