Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

ОПИСЛНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик ())) 938396 (61) Дополнительное к авт, саид-ву(22) Заявлено 24,12.80 (21) 3222304/1 8-21 с присоединением заявки № (23) Приоритет

Опубликовано 23.06.82. Бюллетень № 23 дата опубликования описания 23.06.82 (53)M. Кл, 1

H 03 К 13/175 фктударстююиб камвтет

ЧСФР аю делам взабретеннй н втхрьпвЯ (53) УДК 681.325 (088.8) (72) Автор изобретения

В. Н. Семенчук (71) Заявитель (54) АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к импульсной технике и может быть использовано в преобразователях, входящих в систему регистрации быстропротекаюших процессов, а также в высокоскоростных цифровых приборах.

Известен конвейерный аналоге-цифрс вой преобразователь, содержащий блоки сравнения, ключи, линии задержки, шифратор и сумматор напряжений, причем пре; образуемый сигнал подается одновременно на блок сравнения и линию задержки, подключенную к одному из входов сумматора. На вторые входы блоков сравнения подключены эталонные напряжения, выхо- >5 ды блоков сравнения соединены с управляющими входами ключей и входами шифратора, через которые подключаются эталонные напряжения с обратным знаком на второй вход сумматора. го

Каждый блок сравнения осуществляет сравнение входного сигнала своим эталон ном. Значения эталонов в блоках сравнения разливаются на заданное число кван2 тов, выходные сигналы блоков сравнения управляют ключами, при этом на вход сумматора подается только эталон, соотг ветствуюший сработавшему блоку сравнен ния с максимальным эталонным напряже F нием, а остальные ключи не срабатывают.

3а счет линии задержки происходит синхронизация моментов прихода на вход сумматора эталонного и входного сигна лов (1).

Недостатками преобразователя являются невысокая точность изза того, что входной сигнал проходит через линию за держки, в результате чего происходит искажение сигнала, и низкое быстродействие из- а наличия линий задержек.

Кроме того, в данном устройстве на— рушается синхронизация из-)а неодновременного поступления на входы сумматора входного сигнала и эталонного напряжения за счет разброса параметров линий задержки, достигающих, :30%.

Наиболее близким к изобретению по технической сущности является аналого938396 цифровой преобразователь (A1jI1), использующий принцип стробирования "на лету и. содержащий набор делителей типа напряжения, сложные компараторы, обладающие i памятью типа триггера«защелки, логические элементы, выполняющие функцию антисовпадений, постоянную память на основе диодной матрицы, блок управления, выходной регистр-, причем, первые входы компараторов соединены с делителем напряжения, вторые - с блоком

1 управления, третьи - co входом преобразуемого сигнала, выходы компараторов соединены со входами логических элементов антисовпадений, выходы кото - рых подключены к диодной матрице, имеющей выходы, соединенные с выходным регистром.

Процесс преобразования в таком AUII состоит в образовании с помощью набора компараторов и дополйительной логичеокой цепи адресного импульса, который считывает из постоянной памяти нужный результат. Наличие схемы стробирования позволяет принудительно устанавливать на выходе компаратора одно фиксированное; состояние независимо от изменения вход ного сигнала в промежутках между coceA- ними стробами, а наличие триггерной памяти фиксирует на выходе компаратора 30 то логическое состояние, в котором он находился в момент подачи на триггер разрешающего потенциала (2 j.

Недостатками преобразователя явля-. ются сложность схемного решения из<за

35 наличия блока управления, постоянной па мяти, которая должна иметь все возмож ные комбинации в требуемом порядке, неоднозначность моментов срабатывания

eg} . триггеров при подаче на них разрешающего сигнала, когда на входах компараторов действует один и тот же сигнал, потеря информации в промежутках между соседни,« ми стробами, а также низкое быстродействие.

Пель;.изобретения - повышение точнос ти и увеличения быстродействия преобразо вания.

Поставленная цель достигается, тем, что аналогоцифровой преобразователь., содержащий триггеры регистра, компараторы, первые -входы которых соединены с выходами делителя напряжения, вторые входы - с шиной входного сигнала, а выходы соединены с первыми входа.и соо ветствуюших элементов антисовпадений, вторые входы которых соединены с выходами предшествующих компараторов, а второй вход старшего элемента антисовпадений соединен с обшей шиной, введены вычитатели,, элемент НЕ, формирователи коротких импульсов, усилитель напряжения и элемент ИЛИ, входы которого через формирователи коротких импульсов соединены с соответствукяцими выходами

1 комцараторов, а выход соединен со счет1 ными входами триггеров регистра, при этом первые входы вычитателей соединены с шиной входного сигнала, вторые входыс выходами делителей напряжения, управляющие входы вычитателей, кроме нулево,- го, соединены с выходом соответствую щего элемента антисовпадения и с D -входом соответствующего триггера регистра, а выходы соединенй с соответствующими входами усилителя напряжения, при этом управляющий вход нулевого вычитателя соединен через элемент НЕ с выходом первого хомпаратора, причем, шина

"Сброс" соединена с К -входами триггеров регистра, а выход усилителя напряжения соединен с шиной перехода на следующую декаду.

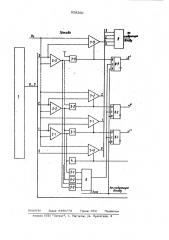

На чертеже представлена структурная схема одной декады АЦП.

Устройство состоит из делителя 1 напряжения, компараторов 2, элементов 3 антисовпадений,элемента HE 4, формирователей 5 коротких импульсов, элемента

ИЛИ 6, вычитателей 7 (О„. — 0> ), трщ геров регистра 8, усилителя 9 напряжения.

Устройство работает следующим об.. разом.

Входной нормированный сигнал подает- ся одновременно на компараторы 2 .и вы читатели 7 первой старшей декады. Каж.дый из компараторов осуществляет срав нение входного сигнала с своим эталоном. Значения эталонов компараторов различаются на заданное число квантов, которые выбираются в соответствии с нормированным сигналом. В нашем случае квант равен 0н: 10. Если компаратор сработает (U „. ) U q ), то выходные сигналы этих компараторов поступают на цепочку элементов 3, которые преобразуют их таким образом, что выходной сигнал, соответствующий "1, остается толыко на одной шине, которая соответствует наивысшему номеру сработавшего компаратора; Этот сигнал является одновременно разрешающим и информационным. Разрешающим для выдачи результата вычитания (ц„„- ) . ) на усилитель 9, у которого коэффициент усиления равен 10. Инчитания, так как этот процесс осуществляется одновременно с сравнением, и разность между входным напряжением и эталоном всегла готова к подключению на вход усилителя, и все операции кодирования выполняются одновременно.

Аналого-цифровой преобразователь, содержащий триггеры регистра, компарато,- ры, первые входы которых соединены с выходами делителя напряжения, вторые входы — с шиной входного сигнала, а выходы соединены с первыми входами соответствующих элементов антисовпадений, вторые входы которых соединены с выходами предшествующих компараторов, а второй вход старшего элемента антисовпадений соединен с обшей шиной, о т л ич а ю ш и и с я тем, что, с целью повы щения точности и ° увеличения быстродействия преобразования, введены вычитатели, элемент НЕ, формирователи коротких импульсов:, усилитель напряжения и элемент ИЛИ, входы которого через формирователи коротких импульсов соединены с соответствующими выходами компараторов, а выход соединен со счетными входами триггеров регистра, при этом первые входы вычитателей соединены с шиной входного сигнала, вторые входы.- с выходами делителей напряжения, ynpahляюшие входы вычитателей, кроме нулевого, соединены с выходом соответствующего элемента антисовпадення и с .D-входом соответствующего триггера регистра, а выходы соединены с соответствующими входами усилителя напряжения, при этом управляющий вход нулевого вычитателя соединен через элемент НЕ с выходом первого компаратора, причем шина

Сброс" соединена с Р, -входами триггеров регистра, а выход усилителя напряжения соединен с шиной перехода на следуюшую декаду.

Источ ники информации принятые во внимание при экспертизе

1. Гитис Э.И. Преобразователи информации для электронных цифровых вычислительных устройств. М., Энергия", 1970, с. 314-318.

2. "Зарубежная радиоэлектроника, 1975, Л 1,. с. 88, 89 (прототип).

5 93839 формационным для выходного регистра 8.

Усиленный сигнал подается на следующую декаду для дальнейшего преобразования, которая выполнена по такой же схеме, как и старшая декада, за исключением делителя 1 напряжения, который является обпгим для всех декад.

Преобразование входног сигнала каждой . декады, величина которого меньше кванта эталонного напряжения осушествля- 0 ется при помощи нулевого вычитателя.

В этом случае ни один из компараторов не срабатывает и первый компаратор через элемент НЕ 4 дает разрешение на подключение входного сигнала ко входу усилителя напряжения. Дальнейшее преобразование в следующей декаде проиоходит по приведенной выше схеме, Для записи сигнала в триггеры регистра используются короткие импульсы, сформированные формирователями 5 из перепада уровня напряжения в момент переключения компараторов в состояние логиче кого "О" или "1". Эти синхроимпульсы через элемент ИЛИ поступают на счет- ные входы триггеров регистра и приводят установку триггеров в состояние в зависимости от информации на )3 -входах.

Точность преобразования увеличивает ся эа счет того, что в устройстве seer 30 да срабатывает только один компаратор в каждой декаде и производится запись

«нформации в выходной регистр. Сработавший компаратор является источником стробирующего сигнала. Кроме того, в компараторах существует эона неопределенности. При подходе сигнала к порогу срабатывания на выходе компаратора

qîýíèêàåò колебательный процесс. При этом возникают большие трудности при 40 считывании кода, связанные с возможностью возникновения погрешностей типа неопределенности считывания. С этой точки зрения в устройстве с помощью формирователя выделяется только один сигнал соответствующий этому моменту переключения компаратора.

В предлагаемом устройстве исключена возможность потери информации между соседними стробами, как это наблюдается 50 в известном, потому что компараторы непрерывно следят за превышением сигналом заданного минимального порогового уровня.

В предложенном устройстве нет потери времени на выполнение операции выФормула из обретения