Аналого-дискретный преобразователь

Иллюстрации

Показать всеРеферат

Сотоэ Советскнк

Соцнапнстнческни

Респубпнк

О П И С А Н И Е ()938397

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. саид-ву (51) M. Кл.

Н 03 К 13/20

{22)Заявлено 30,08.79(2{) 283.66:{ 5/т 82 с присоединениен заявки,% (23) Приоритет

Опубликовано 23.06,82. Бюллетень _#_s 23

Дата опубликования описания 25.06.82 фкударстюай кенитет

СИР

ao asm» езабретений к открмткй (53) УДК 681.325 (088.8) (72) Авторы изобРетениЯ В.И.Иванов, Р-А.Д.Иванцив, В.А.Погрибной и М,П. Бырульник (7!) Заявитель, {54) АНАЛОГО ДИСКРЕТНЫЙ ПРЕОБРАЗОВАТЕЛЬ

Изобретение относится к автоматике и вычислительной технике и используется в системах автоматического контроля и распознавания образцов.

Известен аналого-дискретный. . преобра « зователь, включающий в себя оптронный многоустойчивый элемент, элемент ИЛИ, компаратор, триггер и элемент ЗАПРЕТ (x).

Недостатком известного устройства является низкая точность преобразования.

Цель .изобретения — повышение точности .рвоты устройства.

Поставленная цель достигается тем, что в известный аналого-дискретный пре- 1> образова тель, содержащий компаратор, первый вход которого соединен с входной шиной, второй вход — с шиной опорного пилообразного напряжения и первым входом пикового детектора, а выход - с zo первой выходной шиной и первым входом триггера, второй вход которого соединен с шиной опорного прямоугольного напряжения, а выход — с первым входом эле2 мента И, второй вход которого соединен с шиной сигнала управления и первым входом элемента ЗАПРЕТ, а выход — с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ЗАПРЕТ, а выход со . вторым входом пикового детектора, введены мультиплексор, дешифратор, и-разрядный регистр, И-разрядный счетчик, первый вход которого подключен к шине опорного прямоугольногб напряжения, второй вход - к шине "Сброс, а выходы — к адресному входу мультиплексора и к информационным входам И -разрядного регистра, вход сигнализации которого соединен с выходом элемента И, а выход — с второй выходной шиной и входами дешифратора, выход которого соединен с входами мультиплексора, выход которого соединен с вторым входом элемента .

ЗАПРЕТ.

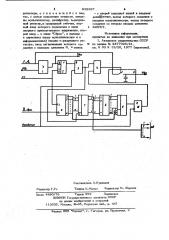

На чертеже представлена структурная схема аналого-дискре тного преобразователя.

938397

Преобразователь вк::;:дичает в себя компаратор 1, триггер 2, элемент И 3, элемент ИЛИ 4, пиковый детектор 6„||-разрядный счетчик 6, и -разрядный регистр

7, дешифратор 8, мультиплексор 9, эле- 5 мент ЗАПРЕТ 10, А налого-дискретный преобразователь работает следующим образом.

Первоначально, импульсом сброса, в момент начала поступлении пилообразного |О напряжения и -разрядный счетчик 6 устанавливается в начальное состояние. После этого на первый вход компаратора 1н на первый вход пикового детектора 5 подается опорное пилообразное напряжение частоты 5, на вход установки в нуль триггера 2 и на счетный вход счетчика

6 подается опорное прямоугольное напряжение частоты Й1, а на второй вход компаратора 1 - входйой сигнал, при этом сигнал управления, который подается на первый вход элемента И 3 и на запрещающий вход элемента ЗАПРЕТ 10, определяет режим работы аналого-дискретного преобразователя запоминание информации или слежение. При равенстве входного напряжения Ug с пилообразным напряжением частоты f, на компараторе

1 формируется импульс, устанавливающий триггер 2 в единичное состояние. 39

Триггер 2 находится в этом состоянии до момента црихода переднего фронта ближайшего импульса опорного прямоугольного напряжения, который перебросит его в нулевое состояние, в результа- 3> те чего сформируется импульс на выходе триггера 2. При наличии сигнала управления на слежение информации импульс с выхода триггера 2 проходит через элемент И 3, первый вход элемента

ИЛИ 4- и на второй вход пикового детектора 5. При этом на выходе пикового детектора 5 появится напряжение равное текущему значению пилообразного напряжения. Одновременно импульсы частоты

Nf поступа|от на счетный вход счетчика 6, После сформирования сигнала на выходе элемента И 3 состояние счетчика

6 переписывается в И-разрядный регистр

7 и на выходе h-разрядного регистра формируется код, соответствующий величине входного сигнала.

Сигналы с .выхода ||-разрядного ре-. гистра 7 поступают на дешифратор 8, в 55 результате на одном изую-выходов дешифратора 8, соответствующего комбинации на входе, появится сигнал. Выходы дешифратора 8 соединены со входами мультиплексора 9. Адресные входы му» льтиплексора 9 опрашиваются сигналами с выхода и-разрядного счетчика 6.

При совпадении кодов на адресных вхо-! дах мудьтиплексора 9 и выходах регистра 7 на выходе мультиплексора 9 появится сигнал, который повторяется пер||одически один раз за время существования пилообразного напряжения и соответствует моменту сравнения на компараторе входного сигнала с опорным, при этом сигнал с выхода мультиплексора 9 не проходит через элемент ЗАПРЕТ 10 и не поступит на элемент HlIH 4.

В режиме слежения выполняется сле дящее преобразование входной электрической величины постоянного напряжения во временной сдвиг (, и цифровой код.

B отличие от режима слежения, в режиме запоминании сигнал с мультиплексора 9 через элемент 10 и 4 поступит на второй вход пикового детектора 5., на его выходе появится напряжение, равное значению пилообразного напряжения в момент поступления команды на запоми-: нание, независимо от величины входного электрического сигнала. Кроме того, сигнал с выхода элемента И 3 прекращает поступать на вход синхронизации д-разрядного регистра 7 и код, установленный ранее в режиме слежения запоминается.

В режиме запоминания запоминается величина входного аналогового сигнала, производится дискретное преобразован|е входной аналоговой величины в аналоговое значение выходного напряжения 0 омх временной сдвиг и код.

Формула изобретения

А налого-дискретный преобразователь, содержащий компаратор, первый вход которого соединен с входной шиной, второй вход — с шиной опорного пилообразного напряжения и первым входом пикового детектора, а выход - с первой выходной шиной и первым входом: триггера, второй вход которого соединен с шиной опорного прямоугольного напряжения, а выход — с первым входом элемента И, второй вход которого соединен с шиной сигнала управления и первым входом элемента ЗАПРЕТ, а выход — с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента ЗАПРЕТ, а выход — со вторым входом пикового

Составитель A.Kóýíåöîa

Техред К.Мыцьо Корректор М. Шароши

Редактор Г.Ус

Заказ 4480/79 Тираж 959 Подпис ное

ВНИИПИ Государственного комитета СССР по делам -изобретений и открытий

113035, Москва, Ж З5, Раушская наб., д. 4/5

Филиал ППП «Патент, г. Ужгород, ул. Проектная, 4

5 938397 6 детектора, î т л и ч а ю m и и с я reM, — с.второй выходной шиной и входамн что, с целью повышения точности, введе-. дешифратора, выход которого соединен с ны мультиплексор, дешв ратор, И-разряд- входами мультиплексора, выход которого ный-регистр,N-разрядный счетчик, цер- соединен со вторым входом элемента вый вход которого. подключен к шине s ЗАПРЕТ. опорного прямоугольного напряжении, второй вход -. к шине «Сброс, а выходы— Источники информации, к адресному входу мультиплексора н к .принятые во внимание при эксцертизе информацнонньп4 входам Иразрядного ре- 1, Авторское свидетельство СССР гистра, вход сигнализации которого со-. 1О по заявке % 2477025/21, единен с выходом элемента И, + выход кл. Н 03 К 13/20, 3,977 (прототип).