Устройство для контроля схем сравнения

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

И ЗОВРЕТЕ Н ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Социалистических

Республик iii940162 (61) Дополнительное к авт. свид-ву (22) Заявлено 28.10.80 (21) 3219398/18-24 (5l)M. Кл.

G 06F 11/26 с присоединением заявки М (23)Приоритет

Ркуаарсиеа4 кемитат

ИВР ав двлаи нмбретевик и открытии (53) УДК681,326. .7(088.8) Опубликовано 30.06.82. Бюллетень 14 24

Дата опубликования описания 30.06.82

Ю. В. Шаирин

I (72) Автор изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СХЕМ

CPAB НЕНИЯ

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств проверки электронных блоков дискретной автоматики и вычислительных

5 машин.

Известно устройство для контроля схем сравнения, содержащее блок управления и два счетчика (1).

Однако указанное устройство малопроиз о водительно н практически непригодно для проверки схем сравнения чисел болыпих фотзматов.

Наиболее близким к предлагаемому является устройство для проверки схем сравнения, содержащее блок формирования сигнала сзиибки,, первый, второй; третий и четвертый триггеры, первый и второй регистры сдвига, причем единичный выход первого триггера. срединен с единич- 20 ным входом второго триггера и, с первым входом первого элемента И-ИЛИ, нулевой выход первого триггера соединен с пер вым входом второго элемента И-ИЛИ, 2 единичный выход второго триггера соеди нен с первым входсм блока формирования сигнала ошибки, выход которого являет» ся выходом устройства, выход контрощь» руемой схемы сравнения соединен с вторым входом блока формирования сигнала ошибки, третий вход которого соединен с единичным выходом третьего триггера, выходы первого и второго элементов

И-ИЛИ соединены с информационными вхэ дами первого и второго регистров сдвига соответственно, информапионные выходы первого и второго регистров сдвига соединены с первым и вторым входами конт ролнруемой схемы сравнения, выход переполнения первого регистра сдвига соеди нен со счетным входсм первого триггера и с вторыми входами первого и второго

=-лементов И ИЛИ, выход переполнения второго регистра .сдвига соединен с "..третьими входами первого и второго еле . ментов КИЛИ и со счетным входом четвертого триггера, нулевой выход «оь торого соединен с четвертыми входами эуют первую и вторую группу выходов устройства.

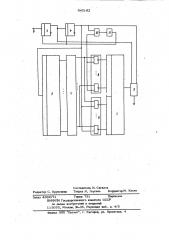

На чертеже представлена функциональ ная схема предлагаемого устройства.

Устройство содержит контролируемую схему 1 сравнения, счетчик 2, первый 3 и второй 4 триггеры, блок 5 фиксации ошибки, тактовый вход 6 устройства, дешифратор 7, первую 8 и вторую 9 груп--. пу элементов И, элемент И 10 и элемент

11 задержки.

Перед началом работы счетчик 2 устанавливается в нулевое состояние, а триггеры 3 и 4 в состояние 10 (цены уста новки не показаны). При этом на вход контролируемой схемы сравнения пост пает число A=1 (возбужден первый .выход дешифратора) и число В=О, на выходе схемы сравнения при правильной ее работе появляется сигнал х (А ) В).

С поступлением первого тактового импульса первый триггер 3 устанавливается в нулевое состояние, отключает or выходов дешифратора первую группу входов схемы сравнения, а на вторую группу входов схемы сравнения подается сиг нал B=l . Схема сравнения при правильной работе должна выработать сигнал х (А<В), с поступлением второго импульса на тактовый вход 6 устройства триггеры 3 и 4 устанавливаются в единичное состояние и, тем самым, на первую и вторую группу входов схем сравнения поданы равные числа, а контролируемая схема сравнения на своем выходе должна выработать сигнал x (A=B). До поступления третьего импульса на вход 6 устройства сйгнал с выхода элемента 11 задержки устанавливает триггеры 3 и 4 в состояние 10, а счетчик 2 — в состояние 1. Длительность задержки элемента 11 должна быть больше времени, необходимого для сравнения двух чисел, но меньше, чем период между двумя тактовыми сигналами.

Таким образом, каждый третий тактовый импульс вызывает увеличение значения счетчика 2 на единицу, на выходе дешифратора 7 возбуждается следующая шина и осуществляется проверка следующих входов контролируемой схемы сравнения. !

Через К переходов счетчика, что соответствует 3К тактам на входе устройства заканчивается полный цикл контроля схемы 1.

Работа логического блока 6 строится в соответствии с таблицей состояний.

3 .Ь40И первого и второго элементов И-ИЛИ, единичный выход четвертого триггера соединен с входом третьего триггера, тактовый вход устройства соединен с тактовыми входами первого и второго регистров сдвига (2 1

Известное устройство обладает недос таточно высокой надежностью функционирования, так как любой сбой регистров сдвига приводит к рассогласованию истинного 10 сипнала сравнения с задаваемым соответ ствуюшими. триггерами управления. В этом случае блок формирования сигнала

I ошибки вьщает ложный сигнал. Укаэанный недостаток обусловлен тем, что в извесь 5 ном устройстве число А формируется первым регистром сдвига, а число В - вторым. Регистры непосредственно связаны с входами проверяемой схемы сравнения, следовательно, они определяют, какой cw- p нал будет на выходе этой схемы. В то . время информацию о том, какой должен быть сигнал на выходе схемы сравнения задают триггеры, состояния которых . в общем случае не зависят от состояний ц5 указанных регистров сдвига.

Цель изобретения — повышение надежности работы устройства.

Поставленная цель достигается тем, что в устройство для контроля схем срав- 50 кения, содержащее блок фиксацииеошибки, элемент И, первый и второй триггеры, причем единичные выходы первого и вторь-. го триггеров соединены соответственно с первым и вторым входами блока фикса35 ции ошибКи, выход которого является выходом устройства, информационный вход устройства соединен с третьим входом блока фиксации ошибки, введены счетчик, дешифратор, первая и вторая группа эле40 ментов И и элемент задержки, причем тактовый вход устройства соединен со счет ным входом первого триггера, единичный выход которого соединен со счетным вхсьдом второго триггера, с первым входом

45 элемента И, с первыми входами всех; элементов И первой группы, единичный . выход второго триггера соединен с первыми входами всех элементов И второй группы, со счетным входом счетчика и с вторым входом элемента И, выход ко50 торого через элемент задержки соединен с установочными входами первого и второго триггеров, информационные выходы счетчика соединены с входами дешифратора, каждый выход которого соединен с

55 вторыми входами соответствующих элементов И первой w втоРой rPymt, выхэды элементов И первой и второй групп обра62 6 нуля (единицы) непосредственно на вход числа А, или числа В, или того и другого вместе определяется только состояниями триггеров 3 и 4. Состояния же этих триггеров однозначно расшифровываются логическим блоком 5 в жестком соотвеч ствии с соотношением чисел А и В. Таким образом, функции формирования соо яошения чисел на входах схемы сравнения и выдача информации об этом соотношении, т. е. выдача информации об истинном,ситънале сравнения, выполняют одни- и те же триггеры 3 и 4, что исключает выработку ложных сигналов ошибки блоком 5 даже при ненадежной работе любого из приме няемых в схеме двустабильных элементов.

Применение дешифратора, кроме указан ных преимуществ; позволяет непосредственно управлять цифровыми индикаторами для получения визуальной информации. о сравниваемых числах.

0.0

0

0

0 выход второго триггера соединен с первы. ми входами всех элементов И второй группы, со счетным входом счетчика и с вто рым входом элемента И, выход которого через элемент задержки соединен с уста новочными входами первого и второго триггеров, информационные выходы счетчика соединены с входами дешифратора, каждый выход которого соединен с вторыми входами соответствующих элементов

И первой и второй групп, выходы элемен тов И первой и второй групп образуют соответственно первую и вторую группу выходов устройства.

Источники информации, принятые во внимание при экспертиае

1. Авторское свидетельство СССР

% 584309, кл. GOGF 11/00, 1975. 2. Авторское свидетельство СССР по заявке М 2661590/18-24, к . 006 ф 11 02, 1978 (протот.ш),.

Ф о р.м у л а и з о б pere н и я

Устройство для контроля схем сравнения, содержащее блок фиксации ошибки, элемент И, первый и второй триггеры, причем единичные выходы первого и втс рого триггеров соединены соответственно с первым и вторым входами блока фикса ции ошибки, выход которого является вы- 4о ходом устройства, информационный вход устройства соединен с третьим входом блока фиксации ошибки, о т л и ч а ющ е е с я тем, что, с целью повышения надежности работы, в него введены счет- 5 чик, дешифратор, первая и вторая группа элементов И и элемент задержки, причем тактовый вход устройства соединен со счетным входом первого триггера, единичный выход которого соединен со счетным входом второго триггера, с первым входом элемента И, с первыми входами всех элементов И первой группы, единичный

5 9401

Любая другая комбинация сигналов йа входе блока 5 вызывает на его выходе сигнал логической единицы, указывающий на неисправность контролируеМой схемы сравнения. 5

Устройство для контроля схем сравнения обладает повышенной надежностью фушшионирования, так как счетчик с дешифратором не влияет на то, какой сигнал сравнения выработан проверяемой схемой, to а служат только для подвижения нуля (единицы) по всем разрядам чисел А и В.

Кроме того, счетчик с дешифратором исключают возможность проявления несколь, ких нулей (единиц) на входах проверяемой ts схемы. При таком построении при ненадежном счетчике имеем надежное устройство, так как сбой в счетчике приводит только к изменению номера разряда сравниваемых чисел, на который должен пос >О тупить нуль (единица). Подача же этого

040162

Составитель И. Сигалов

Редактор С. Крупенина Техред Л1. Гергель КорректорМ. Коста

Заказ 4669171 Тираж 731 Подписное

ВНИИПИ Государственного кааитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., a. 4/5 филиал ППП "Патент, г. Ужгород, ул. Проектная, 4