Устройство для контроля логических узлов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К, АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Соаетснии

Социалистические

Рвспубпии и 940163 (SI ) Дополнительное к авт. сеид-ву (22) Заявлено 30.04.81 (21) 3280402/18-24 (51) М. Кд.

G06 F 11/26 с присоединением заявки .% (23) Приоритет

9вуларстиеииы5 комитет

CCCP ао яелем изобретений и отирьпий

Опубликовано 30.06.82. Бюллетень №24

Дата опубликования описания 30.06.82 (53) УДК681.3 (088.8) Д.И. Павлов (72) Автор изобретения (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ

УЗЛОВ мент И (2.1, 1

Изобретение относится к вычислитель-1 ной технике и может быть использовано для построения управляющих автоматов и автоматов обработки дискретной измерительной информации высокой производи5 телъности.

Известно устройство, содержащее па-. мять, ксвмутаторы, регистр, счетчик, генератор, элемент И f 1).

Недостатком указанного устройства является недостаточная производитеп ность и низкие функциональные возможности.

Наиболее близким к предлагаемому является устройство, содержащее две памяти, генератор, счетчик, два дешифратора, триггер, группу комь.утаторов, элеИзвестное устройство недостаточно эффективно при усложнении или .смене контролируемых объектов.

11ель изобретения - повышение ксэф фициента использования оборудования.

Поставленная пель достигается тем, что в устройство для контроля логических узлов, содержащее генератор, счеч чик, выходы которого соединены с вхс дами первого дешифратора, второй де шифратор, две памяти, первую группу коммутаторов, триггер, элемент И, первый вход усгройства соединен с первыми входами триггера и счетника, первая и вторая группа входов устройства сое динены с первыми группами входов соот ветственно первой и второй памяти, введены два регистра, третий дешифратор, вторая группа коммутаторов, две группы триггеров, элемент задержки, причем выход генератора и второй вход устрой,ства через элемент И соединены с вторь м входом счетчика, третья группа входов стройства соединена с первыми входами коммутаторов первой грутпц1, выходы которых соединены с первыми группами входов первого и второго регистров, вторые группы входов которых соединены с выходами коммутаторов второй группы, %, 15

Z0

50 подается импульсный сигнал логического нуля, приводящий счетчик 2 и триггеры 3, 1l и 12 в исходное состояние.

Процесс считывания информации из памяти 9 и 10 аналогичен процессу записи

З5 и управляется генератором 1, счетчиком 2, дешифратором 6, триггером 3.

При этом айреса считывания определяются совокупностью сигналов на триггерах 12 ао и соответствующих входах устройства.

Необходимо учесть, что до подачи первого воздействия на обьект 17 значение сигналов на выходах заранее не предсказуемо. Поэтому памяти 9 и 10 запрог раммированы так> что на первом цикле работы в режиме считывания информация, считываемая из них, определяется лишь соотношением сигналов на входах регистров 4- и 5 и не зависит от выходных сигналов объекта 17. С момента времени, 50 вой и второй группах входов регистра 5.

55 При этом, если реакция обьекта соответ3 940 первые входы которых соединены с четвертой группой входов устройства, третий вход которого соединен с вторыми входшж коммутаторов первой и второй групп и с первыми входами первой и второй памяти, вторые группы входов которых соответственно через второй и третий дешифраторы соединены с выходами соот ветственно nepaoro и второго регистров, входы которых соединены с первым выходом первого дешифратора, второй выход которого соединен с вторым входом триг гера, выход которого соединен с вторыми входами первой и второй памяти, выходы которых соединены с первыми входами триггеров соответственно первой и второй групп, вторые входы которых соединены с третьим выходом первого дешифратора, четвертый выход которого соединен с третьим, входом триггера, выходом устройства и через элемент задержки с третьим входом счетчика, выходы триггеров первой группы соединены с группой выходов устройства, выходы триггеров второй группы соединены с третьими входами соответствующих ком» мутаторов второй группы, пятая группа входов устройства соединена с третьими входами коммутаторов первой группы первый вход устройства соединен с третьи ми входами триггеров первой и щгорой групп.

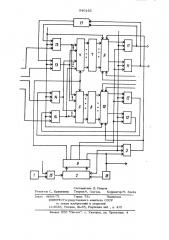

На . чертеже приведена блок-схема уст ройства.

Устройство содержит генератор 1, счетчик 2, триггер 3, регистры 4 и 5, дешифраторы 6-8, памяти 9 и 10, триггеры 11 первой группы, триггеры 12 второй группы, коммутаторы 13 первой группы, коммутаторы 14 второй группы, элемент И 15, элемент 16 задержки, объект 1 7 контроля.

Устройство работает следующим образ ом.

Коммутаторы 13 и 14 в зависимости от значения сигнала на входе устройства коммутируют тот или иной вход, а памяти 9 и 10 в зависимости от значения этот о сигнала работают в режиме записи информации или считывания.

Перед началом работы устройства в памяти 9 и 10 необходимо записать информацию об алгоритме работы, т. е. настроить устройство для проверки конкретной аппаратуры. При этом сигнал ло гического нуля,с соответствующего входа устройства запрещает прохождение импульсов от генератора 1 через элемент

И 15 нп счетчик 2 и приводит триггеры

163 4

11 и 12 и счетчик 2 в исходное состояние. Затем на входах устройства устанавливаются сигналы логической единицы.

При атом импульсы с генератора 1 через элемент И 15 поступают на вход счетчика 2, откуда в параллельном коде на дешифратор 6 подается число отсчитанных импульсов, в результате на входы региг ров 4 и 5 поступает импульс, по которому в них записываются адреса, которые дешифрируются дешифраторами 7 и 8, и в памяти 9 и 10 выбираются ячейки, в которые необходимо записать информацию. Счетчик 2 продолжает считать и дешифратор 6 устанавливает триггер ."; в единичное значение и разрешается з;.,— пись в памяти 9 и 10. Затем дешифратор 6 устанавливает триггер 3 в исходное состояние, чем снимается, сигнал .обращения с памяти 9 и 10, и сигнализирует о необходимости выставить новую информацию для записи и новый адрес и через алемент 16 происходит сброс счетчика 2 в исходное состояние. Далее процесс мно гократно повторяется.

После записи информации подается сигнал логической единицы, разрешающий считывание информации, а коммутаторы l 3 и 15 коммутируют соответствующие входы устройства и триггеров 12. Затем когда значения сигналов на выходах o6båKта 17 заранее предсказуемы, каждое очередное воздействие, выдаваемое на него, зависит от соотношения сигналов на перствует норме, „то из памяти 9 считывае ся очередное воздействие на объект а из памяти 10 считывается воздействие для

МО163 6 в д ое состояние. Если же ки, причем выход генератора и второй перехода в другое состояние. д устройства через элемент И соедиреакция объекта 1

17 соответствует не вход устро м входом счетчика, третья норме (имеется неисправность. ), pa

) то - иены.с вторым вх ст ойства соединена с а него сохра- группа входов устро ства сое нее выданное воздействие на н авности в 3 первыми входами ко коммутаторов первой няется до устРанения неисправности выходы KOTophlx с.оединены с нем, а из памяти т 10 нет воздействия группы, выхо руппами входов первого и вто- ое состояние, Дости- первыми грут

° для перехода в друг тств шему рого регистров, вторые группы входов гае тся это благодаря соответствуюшему рого регист

О. нал уя оторых соединены с выхода ми коммутаЖ РУЯ п охождение выданного воздействия, мож 10 торов р р

P е с вности в рых соединены с четверто гр но определить место неисправности в дов устро ства, т и третий вход которого соеобъекте 17. о оли овать динен с вторыми входами К <»ро>

Изобретение позволяе контролирова ть радиоаппаратуру по любому алгоритму, пе вой и второй памяти, вторые групопределяемому фор инфо мацией, записанной 15 дами первой и второ входов которых соответственно через в блоки ОЗУ, на рим р, и е из ЭВЯ. Устрой- цы входов и третий дешифраторы соединены ее 2 вн ренних второй и тре ство имеет не более уттм соответственно первого и состояний и прео разуе еоб аз т входных сиг- с выходами со го регистров входы которых соединалов -s К выходных сигнал в пр о ичем ены с пе вым выходом первого дешифраTOpB - ч-й -:" --,-. - " или механических перекоммут апий. вто сое нен с вторыми входами первой и и памят asixogsi кото нх техник -экономическая соединен с вто гаэмого устройства . второ в одами триггеров соответсостоит в повышении коэффициента исп га споль-И с первыми х оващм на 30 60%. ственно первой и второ гр ой г yrm вторые зования оборудования на 3

В оды которых соединены с третьим высоставит 15- ходом первого дешифратора, четвертый ая э ктивность от внед-. Вхо к рения изобретения составит 15о на одно иэделие. выхо к д оторого соединен с третьим вхо20 тыс. Руб. в год на

30 дом три1 ге риггера выходом устройства и через элемент задержки с третьим входом счетчика, выходы триггеров первой груп

Устройство д"я контроля л ических ства, выходы триггеров второй группы соератор счетчик динэны с третьими входами соответствуют. узлов, содержашее

35 ш„х „ммутаторов „,ро rpyrrnH, на с первого дешифратора, второй дешифратор группа входов устройства соедине две памяти, первую г реть,ми,ход,ми ко„,муаторов первой т триггер, элемент, пе Руппы первый вход ст и

Г ов пе вой и ства соедпнен с пеРвыМи входамя триг с третьими вход ми триггеров перво и гера и счетчика, первая и вторая группа входов устройства соединены с первыми г ами входов соответственно первой Источники информации, ж 595736, л, G06F 11l26 1976 шифратор, вторая группа коммутаторов,,две группы триггеров, элемент зад рже - (прототип) .

9401 63

Составитель Д. Павлов

Редактор C. Крупенина Техред М. Гергель Корректор М. Коста

Заказ 4669171 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб, д. 4/5 филиал ЛПП "Патент", г, Ужгород, ул. Проектная, 4