Устройство для приема телесигналов

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистических республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

< 940199 (6) ) Донолннтельное к авт. свид-ву (22) Заявлено 26.12,80 (2I) 3224651/18-24 с присоединением заявки № (23) Приоритет

Опубликовано 30 06 82 Бюллетень №24

Дата опубликования описания 03.07.82 (Sl ) M Кл.

608 С 19128

3Ьаударстаенамй каматет

СССР аа делам. иэааретеинй н атарытвй (53) УДК621,398 (088.8) И. И. Кузнецов, В. А. Зимин, В. В. Петкевич и Н. А. Заболотских (72) Авторы изобретения (71) Заявитель

Пермский политехнический институт (54) УСТРОЙСТВО ДЛЯ ПРИЕМА ТЕЛЕСИГНАЛОВ

Изобретение относится к автоматике, телемеханике и связи.

Наиболее близким к предлагаемому устройству по технической сущности является блок воспроизведения состояния ббъектов телесигнализации, который пред- 5 назначен для приема и запоминания параллельного позиционного кода состояния объектов, выдачи из памяти сигналов для управления элементами воспроизведения

iO информации и для сигнализации::несоответствия вновь принятого и хранимого кодов flj .

Положительной стороной такого устройстра является получение сигнала несоответствия ТС, а также возможность проверки элементов блока воспроизведения.

К недостаткам следует отнести невозможность передачи большого объема информации 4,20

Пм1ь изобретения - повышение информативности устройства.

Для достижения указанной цели в устройство, содержащее блок квитирующих

2 ключей, блок сумматоров, элемент ИЛИ, формирователь сигналов управления, информационные выходы которого подключе= ны соответственно к входам блуа памяти, первые выходы которого соединены соответственно с первым входом блока сумматоров, к вторым входам которых подключены соответственно выходы rtep=вой группы элементов ИЛИ, адресные вы-= ходы форьырователя сигналов управления подключены соответственно к выходам второй группы элементов ИЛИ, выход элемента ИЛИ подключен к первому входу элемента И, к второму входу которого, подключен первый вход устройства, введены формирователь адреса, первый коммутатор сигналов и второй коммутатор сигналов, выходы блока квитирунхцих ключей соединены соответственно с пер= выми входами первого коммутатора сигналов, к вторым входам которого подклю чены вторые выходы блока памяти, к третьим входам третьи выходы блока йамяти, первые выходы первого комму94019 татор:- сигналов соедине:.:.. с первыми входами первой группы эл. ментов ИЛИ, вторые выходы — с вторы Аи входами элементов ИЛИ первой группы, выходы блс .ка ó.. маторов подключены к первым входам вт .:рого коммутатора сигналов, вторые выходы блока сумматоров соединены с вторыми входами второго коммутатора с г: алов, третьи входы которого соеди— цепь-. = вторыми входами блока памяти и 1о и- -вымя выходами элементов ИЛИ второй .группы, четвертые входы - с третьими входами блока памяти и вторыми выходами элементов ИЛИ второй группы, выход;-. в; ..- : о коммутатора сигналов соединены -,,-ответственно с выходами устройства и входами элемента ИЛИ, выход элемента И подключен к первому входу фор,ирователя адреса, выходы которого соединены соответственно с вторыми входами элементов ИЛИ второй группы, второй вход устройства подключен к второму входу формирователя адреса.

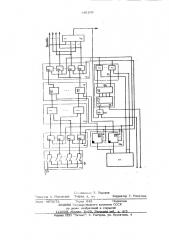

На чертеже представлена структурная электрическая схема предлагаемого устрс:Йства.

Устройство для приема телесигналов содержит блок 1 квитирующих ключей, пе..1лый коммутатор 2 сигналов, первую

-r.",.,: !ó 3 элементов MEIN, блок суммато30 ро. :. +, .; рой коммутатор 5 сигналов, еле .,ен ",Ф 6, формирователь 7 ситналов управления, блок 8 памяти, элемент

И 9, формирователь 10 адреса, вторую группу элементов ИЛИ 11.

Устройство работает следующим об35 разом.

Все количество объектов телесигнализации разбито на IA групп по М объектов в группе. Информация о состоянии объек о тов;.ранится в ячейках блока 8 памяти и отображается положением квитирующих .= .,"эо, ей 1

При . .-. "да.;е тактирующих импульсов на пз ..-".-яй вход устройства через элемент

ИЛИ ., на первый вход формирователя

10 адреса на выходах его последовательно:.бра.= уются сигналы. которые соответст.вуют адресам опрашиваемых групп. Сигналы через группу 3 элементов MEIN поступают на вторые и третьи входы ячеек блока 8 памяти и коммутаторов и з.

С появленИЬм сигнала на первом выходе формирователя 10 опрашиваются через > схем И коммутатора 2 первые N квитирующих ключей первой группы. Инфо..:;.ация о положении этих ключей с выхо.. .Ов элемента И коммутатора 2 пере9 4 дается через первые элементы первой группы 3 элементов ИЛИ на первые входы блока сумматоров. На вторые входы сумматоров 4 поступает информация о тех же Й объектах, которая хранится в блоке памяти.

При совпадении информации по обоим входам блока сумматоров на выходе его и выходах второго коммутатора 5 сигналов не будет. Следовательно, в этом случае сигнала несоответствия с элемента ИЛИ 6 также не последует.

Так как обычно выходы устройства подключаются к сигнальным лампам квитирующих ключей, то в рассмотренном случае ни одна сигнальная лампа не загорится.

Таким образом, последовательно опрашиваются все М групп по М объектов в каждой группе;

В случае отличия информации, хранящейся в блоке памяти, и информации, снимаемой с квитируюших ключей, какой-либо сумматор блока сумматоров в пределах опрашиваемой группы вырабатывает сигнал, который через коммутатор 5 и эле» мент ИЛИ 6 появится как сигнал несоотве тс твия.

Появление сигнала несоответствия свидетельствует о том, что положение квитируюшего ключа и положение объекта находятся в несоответствии. По сигналу несоответствия запирается элемент

11 и тактовые импульсы не проходят на вход формирователя адреса.

Для возобновления работы формирователя следует привести в соответствие положение либо квитируюшего ключа, либо объекта.

Чтобы записать в блок памяти новую информацию, подается сигнал установки нуля по второму входу устройства. Формирователь адреса становится при этом в исходное положение.

Новая информация с информационных выходов формирователя сигналов обмена заносится в блок памяти по адресу, выставленному на одном из адресных выходов формирователя 7, который передается через соответствующий элемент ИЛИ

11 на один из входов блока памяти.

После занесения новой информации работы. устройства возобновляется — запускается формирователь адреса и начинается последовательный опрос квитирующих ключей и блока памяти.

В приведенной на чертеже схеме устройства формирователь адреса выполнен в виде счетчика и дешифратора состояний.

5 940

Коммутаторы 2 и 5 выполнены из Щ групп по М двухвходовых элементов И в каждой группе.

Введение новых функциональных элементов и связей упрощает все устройство в целом, делает его структуру более гибкой и регулярной.

Формула изобретения fO

Устройство для приема телесигналов, содержащее блок квитирующих ключей, блок сумматоров, элемент ИЛИ, формирователь сигналов управления, информацион- 15 ные выходы которого подключены соотг ветственно к входам блока памяти, первые выходы которого соединены соответственно с первым входом блока сумматоров, к вторым входам которых подключены 2р соответственно выходы первой группы элементов ИЛИ, адресные выходы формирователя сигналов управления, подключены соответственно к выходам второй груп пы элементов ИЛИ, выход элемента ИЛИ 2s подключен к первому входу элемента И, к второму входу которого подключен первый вход устройства, о т л и ч а ющ е е с я тем, что, с целью увеличения информативности устройства, в него вве- щ дены формирователь адреса, первый коммутатор сигналов и второй коммутатор сигналов, выходы блока квитирующих ключей соединены соответственно с первыми

199 6 входами первого коммутатора сигналов, к вторым входам которого подключены вторые выходы блока памяти, к третьим входам - третьи выходы блока памяти, первые выходы первого коммутатора, сигналов соединены с первыми входами первой группы элементов ИЛИ, вторые выходы - с вторыми входами элементов

ИЛИ первой группы, выходы блока сумматоров подключены к первым входам второго коммутатора сигналов, вторые выходы блока сумматоров соединены с вторыми входами второго коммутатора сигналов, третьи входы которого соединены с вторыми входами блока памяти и первыми выходами элементов ИЛИ второй группы, четвертые входы - с тре» тъими входами блока памяти и вторыми выходаьи элементов ИЛИ второй группы, выходы второго коммутатора сигналов соединены соответственно с выходами устройства и входами элемент ИЛИ, выход элемента И подключен к первому входу формирователя адреса, выходы которого соединены соответственно с вторыми входами элементов ИЛИ второй группы, второй вход устройства подключен к второму входу формирователя адреса.

Источники информации, принятые во внимание при экспертизе

1. Пшеничников А. М., Портнов М. А.

Телемеханические системы на интеграль= ных микросхемах. N., "Энергия, 1977, с. 193 - 196.

Сс тавите.i к- I, Барская ." едал тор А. Маковская Текред А, A R Корректор Г. Решетник

Заказ 4672/72 Тираж 642 Подлисное

БНИИПИ Государ= венного комитета СССР по делам изобретений и открытий сва. Р са а6

Филиал ППП Патент", г. Ужгород, ул. Проектная, 4