Запоминающее устройство

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (>940235

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскими

Социалистических

Республик (61) Дополнительное к авт. свид-ву— (22) Заявлено 29.12.80 (21) 3224694/18-24 с присоединением заявки №вЂ” (23) Приоритет— (51) М. Кл.з б 11 С 11 00

Гасударственный квмнтвт, Опубликовано 30.06.82. Бюллетень № 24

Дата опубликования описания 30.06.82 (53) УДК 681.327 (088.8) по делам нзвбрвтеннй н вткрмтий (72) Авторы изобретения

Г. Б. Энтин и Г. Н. Острась (71) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРО1"1СТВО

Изобре гение относится к запоминающим устройствам и может быть использовано в вычислительных системах, содержащих запоминающие устройства с произвольной выборкой чисел.

Известно запоминающее устройство, которое содержит источник разрядных токов, накопитель с разрядными шинами, согласующие резисторь и трансформатор с двумя первичными обмотками и вторичной обмоткой, соединенной с усилителем считывания (1) .

Недостаток известного устройства низкая надежность.

Наиболее близким к предлагаемому является запомИнающее устройство, содержащее накопитель на ферритовых сердечниках, дешифратор слов, соединенный с формирователями выбора слов, выходы которых соединены с числовыми обмотками накопителя, разрядный считывающий дешифратор, соединенный со входом формирователей считывания, блок управления, источник кодов (блок приема кодов), соединенный со входами формирователей записи, выходы которых соединены с выходами формирователей считывания и с началами пары разрядных обмоток накопителя, концы которых через первую пару диодов соединены с общей шиной, а через вторую пару диодов — с началом и концом первичной обмотки трансформатора, вторичная обмотка которого подсоединена к балансному (двухполярному) усилителю считывания, причем блок управления соединен с формирователями выбора слов, 10 формирователями записи и формирователями считывания, а средняя точка первичной обмотки трансформатора соединена с общей шиной (2}.

Недостатком данного устройства является низкая надежность за счет того, 15 что при считывании выделение разнополярных сигналов происходит на фоне разнополярных помех.

Цель изобретения — повышение надежности устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, адресный дешифратор, формирователи сигналов выбора чисел, регистр числа, формирователь сигналов записи, 940235

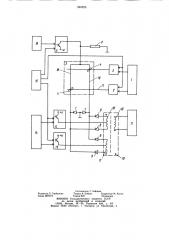

На чертеже изображена функциональная схема устройства.

Устройство содержит адресный дешифратор 1, формирователи 2 сигналов выбора чисел, накопитель 3, выполненный на ферритовых сердечниках 4, формирователь 5 сигналов записи, ограничительный элемент, группы разделительных элементов, согласующий узел, усилитель считывания, основной формирователь сигналов считывания, разрядный дешифратор и блок управления, первый, второй и третий выходы которого подключены к одним из входов формирователя сигналов записи, формирователей сигналов выбора чисел и основного формирователя сигналов считывания соответственно, выходы адресного дешифратора соединены с другими входами формирователей сигналов выбора чисел, выходы которых подключены. ко входам числовых обмоток накопителя, выходы регистра числа соединены с другим входом формирователя сигналов записи, выход которого подключен к началам разрядных обмоток накопителя, концы которых через разделительные элементы первой группы соединены с шиной нулевого потенциала, входы усилителя считывания подключены к первому и второму выводам согласующего узла, третий и четвертый выводы которого соединены через разделительные элементы второй группы с концами разрядных обмоток накопителя, пятый вывод согласующего узла подключен к выходу основного формирователя сигналов считывания, другой вход которого соединен с одними из выходов разрядного дешифратора, введены дополнительный формирователь сигналов считывания, третья группа разделительных элементов и ограничительный элемент, один вывод которого подключен к выходу формирователя сигналов записи, а другой вывод

К шине нулевого потенциала, причем шестой и седьмой выводы согласующего узла соединены через разделительные элементы третьей группы с концами разрядных обмоток накопителя, а восьмой вывод согласующего узла подключен к выходу дополнительного формирователя сигналов считывания, входы которого соединены соответственно с одним из входов основного формирователя сигналов считывания и с другими выходами разрядного дешифратора.

При этом согласующий узел выполнен в виде трансформатора, содержащего основную и дополнительную первичные обмотки и вторичную обмотку, причем полярность включения дополнительной первичной обмотки противоположна полярности включения основной первичной обмотки, выводы обмоток и средние точки первичных обмоток трансформатора являются выводами узла.

Зо

55 например резистор 6, первая 7, вторая 8 и третья 9 группы разделительных элементов, например диодов, согласующий узел, например трансформатор 10, усилитель 11 считывания, основной 12 и дополнительный 13 формирователи сигналов считывания, разрядный дешифратор 14, блок 15 управления и регистр 16 числа. На чертеже обозначены числовые 17 и разрядные 18 и 19 обмотки накопител1, основная 20 и дополнительная 21 первичные обмотки и вторичная обмотка 22 трансформатора.

Устройство работает следующим образом.

В исходном состоянии блок 15 управления не выдает управляющих сигналов. Дешифратор 1 подготавливает адрес выбираемого слова, регистр 16 подготавливает код числа для записи в накопитель 3, дешифратор 14 подготавливает адрес считываемой разрядной обмотки 18 и 19 накопителя 3.

При записи информации блок 15 выдает управляющие сигналы на формирователи 2 и формирователь 5. Формирователи 2 формируют ток выбора в одну из числовых обмоток 17 накопителя 3 по адресу, сформированному дешифратором l. Форми. рователь 5 формирует ток записи кода числа, который протекает через разрядные шины 18 и 19 накопителя 3 и далее через диоды 7 на шину нулевого потенциала. Часть этого тока записи протекает также через резистор 6.

При считывании информации блок 15 выдает управляющие сигналы на формирователи 2 ° 12 и 13. Формирователи 2 формируют ток выбора в одну из числовых обмоток 17 накопителя 3. Если число считывается с разрядной шины 19, то по сигналу с дешифратора 14, запускается формирователь 12 и выдает разрядный ток считывания, который поступает в средний вывод обмотки 20 трансформатора 10, далее из этой обмотки через диоды 8 — в разрядные шины 18 и 19 накопителя 3 и через резистор 6 — на шину нулевого потенциала, При этом считанный сигнал положительной полярности с сердечника 4, расположенного на разрядной шине 19 накопителя 3, поступает через открытые диоды 8 на начало обмотки 20 трансформатора 10 и далее усиливается усилителем 11.

Помехи отрицательной полярности при этом также проходят через диоды 8 и трансформатор 10 на вход усилителя 11, но не проходят через усилитель 11, который в силу своей однополярности способен пропускать только сигналы положительной полярности.

Если число считывается с шины 18, то запускается формирователь 13 и выдает разрядный ток считывания, который поступает в средний вывод обмотки 21 трансформатора 10, далее через диоды 9 — в

940235 разрядные шины 18 и 19 и через резистор 6— на шину нулевого потенциала. При этом считанный сигнал положительной полярности с сердечника 4, расположенного на шине

18, поступает через открытые диоды 9 на начало обмотки 21 трансформатора 10 и далее усиливается усилителем 11, а помехи отрицательной полярности, как это было описано ранее, не проходят через усилитель 11.

Таким образом, на усилителе 11 при считывании происходит выделение однополярных положительных сигналов, a спектр отрицательных сигналов и помех не воспринимается, что обеспечивает повышение помехоустойчивости.

Технико-экономическое преимущество предлагаемого устройства заключается в его более высокой по сравнению . с прототипом надежности.

Формула изобретения

1. Запоминающее устройство, содержащее накопитель, адресный дешифратор, формирователи сигналов выбора чисел, регистр числа, формирователь сигналов записи, группы разделительных элементов, согласующий узел, усилитель считывания, основной формирователь сигналов считывания, разрядный дешифратор и блок управления, первый, второй и третий выходы которого подключены к одним из входов формирователя сигналов записи, формирователей сигналов выбора чисел и основного формирователя сигналов считывания соответственно, выходы адресного дешифратора соединены с другими входами формирователей сигналов выбора чисел, выходы которых подключены ко входам числовых обмоток накопителя, выходы регистра числа соединены с другим входом формирователя сигналов записи, выход которого подключен к началам разрядных обмоток накопителя, концы "которых через разделительные элементы первой группы соединены с ши40

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 253145, кл. G 11 С 11/00, 1969.

2„Патент США № 3673580, кл. 340/174, опублик. 1970 (прототип). ной нулевого потенциала, входы усилителя считывания подключены к первому и второму выводам согласующего узла, третий и четвертый выводы которого соединены через разделительные элементы второй группы с концами разрядных обмоток накопителя, пятый вывод согласующЕго узла подключен к выходу основного формирователя сигналов считывания, другой вход которого соединен с одними из выходов разрядного де p шифратора, отличающееся тем, что, с целью повышения надежности устройства, оно содержит дополнительный формирователь сигналов считывания, третью группу разделительных элементов и ограничительный элемент, один вывод которого подклюI5 чен к выходу формирователя сигналов записи, а другой вывод — к шине нулевого потенциала, причем шестой и седьмой выводы согласующего узла соединены через разделительные элементы третьей группы с

20 концами разрядных обмоток накопителя, а восьмой вывод согласующего узла подключен к выходу дополнительного формирователя сигналов считывания, входы которого соединены соответственно с одним из входов основного формирователя сигналов

25 считывания и с другими выходами разрядного дешифратора.

2. Устройство по п. 1, отличающееся тем, - что согласующий узел выполнен в виде трансформатора, содержащего основную и дополнительную первичные обмотки и

З0 вторичную обмотку, причем полярность включения дополнительной первичной обмотки противоположна полярности включения основной первичной обмотки, выводы обмоток я средние точки первичных обмоток трансформатора являются выводами узла.

2/

Составитель Т. Зайцева

Редактор Л. Горбунова Техред А. Бойкас Корректор М. Коста

Заказ 4676/74 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113036, Москва, Ж вЂ” 36, Раушская наб., д. 4/6

Филиал ППП <Патент>, r. Ужгород, ул. Проектная, 4