Аналого-цифровой преобразователь с автоматической коррекцией

Иллюстрации

Показать всеРеферат

К). В. Малахов, А. А. Квасов и Н. В. Л йФачев

/»

=. (72) Авторы изобретения (71) Заявитель (54) АНАЛОГОЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

С АВТОМАТИЧЕСКОЙ, K0PPEKUHEA

Изобретение относится к вычислитель.. ной технике и может быть применено в прецизионных устройствах контроля цифроаналоговых преобразователей устройств ввода-вывода I1BM.

Известны аналого-цифровые 1треобраэователи с автоматической коррекцией.

Указанные устройства основаны на компенсации сдвига нулевого уровня в цифровой, аналого- ой или чисто аналоговой форме (1

Недостатками известных устройств яиипотся сложность схемкой реализации, необходимость обратного преобразования полученного кода в напряжение„ значительное время преобразования.

Наиболее близким к предлагаемому является аналого-цифровой преобразователь с автоматической корреюлей, содержа1пий преобразователь код-напряже- 20 ние, компаратор, источник опорного напряжения, блок управления, первь1я выход кол орого соединен с цифровым входом . f I .

В известном устройстве недостаток обусловлен сдвигом нуля к ограниченной величиной коэффициента ослабленной син фаэной составлякапей, устраня егся посред-. ством проведения двух преобразований, при которых преобразуемое наптвпкение-. подается поочередно на первый и второй:

Ф входы компаратора, а точное значение кода вычисляется как среднее арифмети ческое кодов, полученных ttptt двух преобразованиях.

Однако данный преобразователь тре бует значительного времени преобраэо вания из- за необходимости проведения двух циклов преобразования, кроме того, ннзка надежность срабатывания огдепь ных элементов устройства.

Бель изобретения — повышение быстродействия и увеличение надежносш преобразователя.

Поставленная цель достигается тем, тго в аналого-цифровой преобразователь с автоматической коррекцией, cottepactttttttN

l0

20

Зо

35, "On- 4 "ОП - Я.>

45

55

3 94 преобразователь код-напряжение, компаратор, источник опорного напряжения, блок управления, первый выход которого соединен с цифровым входом преобразователя код-напряжение, введены дополнительны и идентичный основному преобразователь код-напряжение, входной коммутатор, процессор и запоминающее устройство, при этом выходы источника опорного напряжения. и шина преобразующего сигнала через входной коммутатор подключены соответственно к аналоговым б входам Основно1 о и дополнительного пр &» образователей код-напряжение, цифровой вход последнего соединен с вторым выходом блока управления, третий выход которого соединен с управляющим входом входного коммутатора, а выход - с первым выходом процессора, причем выходы преобразователей код-напряжение подключены соответственно к входам компаратора, выход которого подключен к первому входу процессора, вторые вход и выход которого соединены с входом и выходом запоминающего устройства.

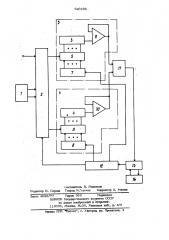

На чертеже изображена блок-схема предлагаемого преобразователя.

Устройство содержит источник 1 опорного напряжения, входной коммутатор 2, два идентичных преобразователя

3 и 4 код-напряжение, содержапйх сост« ветственно декодирующие сетки Р, -2 К

3 и 4, коммутаторы 5 и 6 разрядов, управляющие регистры 7 и 8, буферные операционные усялители 9 и 10, компаратор 11, блок 12 управления, процессор 13 и запоминающее устройство 14.

Преобразователь работает следуюшим образом.

Устройство перед началом преобразования входного напряжения производит самокалибровку, при которой запоминает значения собственной абсолютной погрешности в ряде точек в диапазоне входных напряжений v в дальнейшем, при преобразовании входных напряжений учитывает собственную погрешность, алгебраически складывая ее с полученным кодом, В режиме самокалибровки входной коммутатор 2, управляемый по сигналам блока 12 управления, подает опорное напряжение положительной или отрицательной полярности от источника 1 опорного напряжения на вход коммутатора 5 разрядов первого преобразователя 3 код-напряжение и на вход коммутатора.

6 разрядов второго преобразователя 4 код-напряжение. Коммутатор 5 разрядов, 02М 4 управляемый регистром 7 по сигналам блока 12 управления, получающего информацию иэ процессора 13, подключает все входы декодирующей сетки 3 к шине источника опорного напряжения вследствие чего с выхода буферного операционного усилителя 9 на первый вход компаратора 11 подается величина опорного напряжения, смещенная на вепичину сдвига нулевого уровня операционного усютителя

9 и компаратора 11, приведенного к первому входу компаратора .11.

Коммутатор 6 разрядов, управляемый регистром 8 по сигналам с блока 12 управления, подключает все входы декодирующей сетки 4 к шине источника опор ного напряжения, в результате чего с выхода буферного операционного усилителя 10 на второй вход компаратора ll подается величина опорного напряжения, смещенная на величину сдвига нулевого уровня операционного усилителя 10. С выхода компаратора 11 сигнал подается на вход процессора 13.

По сигналу компаратора процессор

13 определяет, на каком из входов компаратора 11 напряжение больше. Коммутатор разрядов (5 или 6) преобразователя код-напряжение той ветви, где напряжение на входе компаратора 11 наибольшее, по сигналам блока 12 управления, получающего информацию or процессора 13, в соответствии с алгоритмом поразрядного уравновешивания, отключает часть разрядов соответствующей декодирующей сетки (3 или 4); в результате чего напряжения на входах компаратора 1 1 уравновешиваются где Цп - опорное напряжение;

К - цифровой код в одном из управляюпжх регистров; — сдвиг нулевого уровня, приведенный к первому входу компара гора 11;

Ь вЂ” сдвиг нулевого уровня, приведенный ко второму входу компаратора 11.

Значение цифрового кода определяется как (Оп — Ь4 + Ь2 „, + Ь1 7- Ь 2. (оп 0ï

Процессор 13 вычисляет значение абсолютной погрешности устройства по формуле Ь1 т Ья

А=К - - ю

U0n где 0 - входное напряжение; — цифровой код в управляющем

ИХ регистре. .Значение цифрового кода определяется из формулы (4) как

ВХ 1+ +9. ВХ ОП ОТ1 ÎÎ

Точное значение цифрового кода вы35 числяется в процессоре 13 с учетом значений b, храняшихся в запоминак щем устройстве 14 и соответствующих, ближайших к полученному (В.) значениям кодов, по формуле

К1= + /Ь ( ВЪ

{ оп где k - точное значение цифрового кода равное в результате подста 4 новки (5) в (6) К = их - ..

Таким образом, полученное точйое значение кода свободно от погрешности, 1

kl = и

5 9402 где Ь - абсолютная погрешность устройства, и подает его в запоминающее устройство 14. Запоминающее устройство 14 хранит значение Ь

Ступенчато изменяя значения кодов в регистрах 7 и 8 от максимального до минимального и каждый раз производя уравновешивание напряжений на входах компаратора ll, вычисление и запоминание величины Ь, устройство полу- 10 чает ряд значений собственной абсолютной погрешности в диапазоне возможных входных напряжений. На этом заканчивается режим самокалибровки.

В режиме измерения входной коммутатор 2 подает входное напряжение на вход одного из преобразователей коднапряжение, а на вход второго преобразователя соответственно подает опорное напряжение от источника l опорного 20 напряжения. В результате выполнения алгоритма поразрядного уравновешивани ( устанавливается равенство напряжений на входах компаратора 11

M 6 создаваемой сдиигом нулевого уровня компонентов предпагаемого устройства, обусловленного в том числе и ограниченной величиной коэффициента ослабпения синфазной составляющей.

Формула изобретения

Аналого-цифровой преобразователь с автоматической коррекцией, содержащий преобразователь код-напряжение, компаратор, источник опорного напряжения, блок управления, первый выход ко горого соединен с цифровым входом преобраз< вателя код-напряжение, о т л и ч а юшийся тем, что, с целью повышения быстродействия и увеличения надежности преобразователя, в него введены дополнительный идентичный основному преобразователь код-напряжение, входной коммутатор, процессор и запоминающее устройство, при этом выходы источника опорного напряжения и шина преобразутьшего сигнала через входной коммутатор подключены соответственно к аналоговым входам основного и допслнительного преобразователей код-напряжение, цифровой вход последнего соединен с вторым выходом блока управления, третий выход которого соединен с управляюшим входом входного коммутатора, а входс первым выходом процессора, причем выходы преобразователей код-напряж нне подключены соответственно к входам компаратора, выход которого подключен к первому входу процессора, вторые вход и выход которого соединены с входом и выходом запоминающего устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент Франции % 2196559, кл. Н 03 К 13/02, 1977.

2. Авторское свидетельство СССР

М 379979, кл. Н 03 К 13/17, 1971 (прототип) .. с.оставнтель В. Махнанов

Редактор Ю. Середа Техред М.Гергель Корректор A. Ференц

Заказ 4686/77 Тираж 959 Подписное

ВНИИПИ Государственного комитета СССР о делам изобретений и открой, 113035, Москва, Ж35, Раушская наб., д. 4/5

Филиал ППП 4 Патент, г. Ужгород, уп. Проектная, 4