Делитель частоты

Иллюстрации

Показать всеРеферат

3 9403 входы которого соединены с входными шинами, первый выход подключен к первому входу третьего регистра, а второй выход соединен с первым входом триггера, второй вход которого соединен с вторыми входами регистров и шиной сигнала управления, а выход тригге- ра соединен с первыми входами управления первого и второго коммутаторов, вторые входы управления которых сое- 1а динены с выходом первого сумматора, вход которого соединен с выходом первого коммутатора, причем информационный вход второго коммутатора соединен с информационной входной шиной.

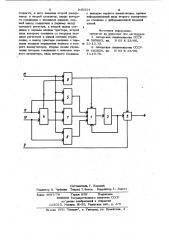

На чертеже показана .структурная схема предлагаемого делителя.

Делитель частоты содержит коммутаторы 1 и 2, сумматоры 3 и 4, регистры

5 — 7 и триггер 8. На информационную входную шину 9 подается делимый сигнал, на входные шины 10 и 11 — кодовый сигнал установки коэффициента деления, а на шину 12 — сигнал управления.

Коэффициент деления частоты задается соотношением двух чисел Р и 6, которые поступают по шинам 10 и 11.

Данные числа могут иметь как целочисленное, так и рациональное значение.

Перед началом процесса деления частоты или перед изменением коэффициента деления на сумматоре 4 производится операция вычитания P — Q = Я, целью которой является определение разности, а также определение наибольшего из чисел Р или g по знаку числа R . .После

35 окончания выполнения данной операции по сигналу, поступакщему по шине 12, полученный результат К записывается в регистр 7, знак числа Р, в триггер 8, 40 числа P и Ясоответственно s регистры

5 и 6, После этого процесс деления частоты производят на новый коэффициент деления по каждому импульсу входной частоты. При этом сумматор 3 выполня45 ет следующие операции (при Р ЪЦ):

Р12.-q; (Pn.-g)-Ч =Р12--2Q,...

СPi - и-1)93 ц =Р1 2.-4Ц =М, Возникающая при таком алгоритме процесса деления ошибка не превышает единицы или одного младшего размера.

Деление числа Р на два в устройстве производится с целью увеличения точности процесса, так как в этом случае ошиб- 55 ка не превышает 1/2 или половины младнн го разряда, Для проведения да1пп m операций числа Р/2 и @через коммута14 4 тор 1 подаются на вход сумматора 3, причем операция деления на два числа, заданного в двоичном коде, производится путем сдвига в сторону младших разрядов, что производится при передаче числа Р через коммутатор 1. После выполнения каждой операции вычитания оценивается знак полученного результата Х,1 . Если Х,;) 0, то прсдолжается, операция вычитания .числа Ц . Если Х.;<О

I то импульс ВХОднОй частОты с шины 9 пропускает через коммутатор 2, и на сумматоре 3 выполняется действие (Р/2 — .1 9 )t R.

Далее процесс продолжается аналогичным образом и после прохождения количества импульсов входной частоты, численно равного И на сумматоре 4 выполняется действие Р-(И-V) @+1 = 1" где hl — количество импульсов на выходе делителя;

И вЂ” количество импульсов на входе делителя; — число, полученное на выходе

ОСт сумматора.

Преобразуем данное выражение

Р «(ос.т- 1Ф ю

И вЂ” ж, И.Я

Р

U-- — =—

Ц м

Таким образом, соотношение количества импульсов на входе и количества импульсов на выходе делителя частоты равно соотношению двух заданных чисел 1 и 6, определяющих коэффициент деления частоты.

В случае, если Pc Q, операция деления частоты производится аналогичным образом, По сигналу, поступающему с триггера 8, запоминается знак числа К, в данном случае — R через коммутатор 1 на сумматор 3 подаюгся слагаемые для проведения необходимых операций.

Формула изобретения

Делитель частоты, содержащий три регистра, выходы которых соединены с информационными входами первого коммутатора, а первые входы двух из которых соединены со входными шинами, первый сумматор и триггер, о т л и ч а ю— шийся тем, что, с целью увеличения

5 940314 6 точности, в него введены второй комму- с выходом первого коммутатора, причем татор и второй сумматор, входы которо- информационный вход второго коммутатого соединены с входными шинами, пер- ра соединен с информационной входной вый выход подключен к первому входу шиной. третьего peT HGTpB B второй выход сое» динен с первым входом триггера, второй Источники информации, вход которого соединен со вторыми вхо- принятые во внимание при экспертизе дами регистров и шиной сигнала управ- 1. Авторское свидетельство СССР ления, а выход триггера соединен с-пер- М 595863, кл. Н 03 К 23/00, выми входами управления первого и вто- to 23.12.75. рого коммутаторов, вторые входы управ- 2. Авторское свидетельство СССР лещи которых соединены с выходом пеР- N 683026, кл. Н 03 К 23/00, вого сумматора, вход которого соединен 14.10.76.

Составитель Г. Королев

Редактор H. Чубелко Техред Т.фанта. Корректор А. Дзятко

Заказ 4687/78 Тираж 959 - Подписное

ВНИИПИ Государственного коьитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4