Устройство для измерения частоты низкочастотных гармонических сигналов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К ASTOPCKOMY СВИДИтЮЛЬСтВЮ

Союз Советск их

Социалистических

Республик

* 2 (6I ) Дополнительное к авт. свнд-ву— (53)М. Кл. (22)Заявлено 30.04.80 (21) 2917829/18-21

G 01 R 23/00 с присоединением заявки М

9кударствснный комитат

СССР (23) Приоритет— (53) УД,К 621.317 (088.8) но делам изабратеи и и аткрыти»

Опублнкорано 07. 07.82. Бюллетень М 25

Дата опубликования описания 1 0 .07 .82

О.С. Маркевич, Т.А. Маркевич -и. С.П. Скляр с

I (72) Авторы изобретения (71) Заявитель (54 ) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ НИЗКОЧАСТОТНЫХ

ГАРМОНИЧЕСКИХ СИГНАЛОВ

Изобретение относится к электроизмерительной технике и предназначено для измерения частоты низкочас" тотных гармонических сигналов.

Известно устройство для измерения частоты, содержащее два интегратора, квадраторы, блоки деления и извлечения корня (1).

Недостатком устройства является относительно низкое быстродействие.

Известно устройство для измерения частоты, содержащее блоки двойного дифференцирования., деления и извлечения корня $2 3.

В известном устройстве операция двойного дифференцирования производится с запаздыванием, что приводит к несинхронности напряжений на входах блока деления и снижению динамической точности измерения частоты.

Цель изобретения - повышение динамической точности измерения частоты.

Поставленная цель достигается тем, что в устройство для измерения частоты низкочастотных гармонических сигналов, содержащее блок двой"

5 ногс дифференцирования и последовательно соединенные блок деления и блок извлечения корня, введены два блока определения модуля, а блок двойного дифференцирования выполнен в виде последовательно соединенных сумматора и двух интеграторов

У а также инверторы, причем первый вход сумматора является входом устройства, выход первого интегратора через инвертор соединен со вторым входом сумматора выход BTopol интегратора соединен с третьим вхо" дом сумматора и через первый блок определения модуля с первым входом

2о блока деления, второй вход которого через второй блок определения модуля соединен с выходом сумматора.

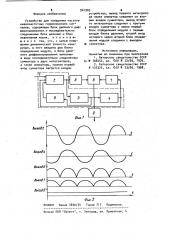

На фиг. 1 приведена структурная схема устройства, на фиг.2 - эпюры напряжений, действующих на выходах блоков.

Устрбйство содержит блок 1 двойного дифференцирования включающий сумматор 2, интеграторы 3 и ", инвертор 5, блоки 6 и 7 определения модуля, блок 8 деления„ блок

9 извлечения корня.

Устройство работает следующим образом.

Анализируемый гармонический сигнал поступает на вход блока 1 двойного дифференцирования, состоящего из сумматора 2, интеграторов 3 и 4 и инвертора 5. Передаточная функция от входа (вход сумматора 2) до выхода (выход интегратора М) запишется в виде щ р) " (1)

" »1 гО где К - коэффициент пропорциональности, определяемый масштабным коэффициентом блока 8, деления и выбранной постоянной величиной Т .

Блок 9 преобразует выходной сигнал устройства деления по зависимости

1905 4 на 0 (И ..Поскольку устройства давления, оперирующие с напряжениями одного знака заметно проще устройств, на входы которых подают5 ся знакойеременные напряжения, перед операцией деления 0 (4) íà U (4) введены операции определения модуля

/U<(+P (и !U< (4) / выполняемые блоками 6 и 7. Результат деления при

1В этом не изменяется .по величине.

Выход блока 8 деления (Ор)таким образом воспроизводит в определенном масштабе величину

I Ua(t) i. а !

04(4) ((5) (6}

,=1 9- ®=1< @

В качестве двойного дифференци.рующего звена применено динамическое звено второго порядка, обладающее сглаживающими свойствами. Возникающее при этом противоречие между необходимой степенью сглаживания и требованием синхронности сигналов на входах устройства деления преодолено путем использования элементов звена второго порядка в обеих цепяхделимого и делителя. Благодаря такому включению автоматически обеспечивается требуемая синхронность при любых заданных уровнях сглаживания и при любых частотах входного сиг" нала.

Таким образом, достигается существенное повышение точности измерения частоты по сравнению с известным в реальных условиях использования устройства. Степень сглаживания, а следовательно, и быстродействие устройства могут

Дыть выбраны в соответствии с ка" честеом входного сигнала простым изменением коэффициентов усиления интеграторов. Это является также положительным свойством предлагаемой схемы: она может быть легко перенастроена в соответствии.с требуемым показателем динамической точности (быстродействие"точность). (2) где параметр Т< зависит от коэффициентов усиления блоков 2, 3 и 4. Таким образом, связь между выходом интегратора 4 и выходом сумматора 2 соответствует двойному дифференцированию. Бсли на выходе интегратора

4 установились вынужденные колебания U (t) с частотой, равной частоте входного сигнала и амплитудой, определяемой амплитудой выходного сигнала А и коэффициентом передачи блока (2) на частоте и)(1(>) 45

04 + = Aî "4 " <

50 то на выходе сумматора 2 напряжение будет меняться .по закону (4)

Ug(1= Tg+o1 <(®) " "

55 т.е. строго в противофазе и будет отличаться по амплитуде в То (Ю раз.

В этом легко убедиться, поделив U (È

1 где параметры звена (и Т могут быть г5. выбраны в желаемом диапазоне путемнас ройки коэффициентов усиления блоков 2,3 и 4 по известным зависимос" тям.

Передаточная функция от входа 5я сумматора 2 до входа интегратора

3 запишется в виде

ТоР х(Р> - .1+2 - + Т

941905 . 6 устройства, выход первого интеграто. ра через инвертор соединен со вто-. рым входом сумматора, выход второго интегратора соединен с третьим входом сумматора и через первый блок определения модуля с первым входом блока деления, второй вход которого через второй блок определения модуля соединен с выходом

1В сумматора.

5 формула изобретения

ВНИИПИ Заказ 4830/34 Тираж 717 Подписное.

Филиал llflll "Патент", г. Ужгород, ул. Проектная, 4

Устройство для измерения частоты низкочастотных гармонических сигналов, содержащее блок двойного дифференцирования. и последовательно соединенные блок деления и блок извлечения корня, о т л и ч а ющ е е с я тем, что, с целью повышения.динамической точности измерения, в него введены два блока определения модуля, а блок двойного дифференцирования выполнен в виде последовательно соединенных сумматора и двух интеграторов, а также инверторы, причем первь1й вход сумматора является входом

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

1s 1й 708252 кл. G01 Й 23/00, 1976.

2. Авторское свидетельство СССР

М 435325, кл. 6 01 R 23/00, 1968.