Устройство для извлечения квадратного корня

Иллюстрации

Показать всеРеферат

О П И С А Н И Е (ii>942005

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советски к

Соцнапмстнческнк

Республнк (61) Дополнительное к авт, саид-ву(22)Заявлено 04.08.80 (2!) 2967605/18-24 с прнсоедннением заявки йе— (ы)М. К .

С 06 F 7/552

3Ъеуирстаанный камктет.

СССР ав делам кзабретений н открыткй (23) П риорнтет—

Опублнковано 07.07.82.- Бюллетень М 25 (53) УДК 68l.325 (088.8) Дата опубликования опнсання 07.07.82 (72} Авторы изобретения

Н.В. Черкасский, А.А. Мельник и В.В. Че кйсстсая — -= (1 ф „. »-, t

° ЮВ УР- ::,: 1Я3

4 с в 4» (7! ) Заявитель (54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО

КОРНЯ

Изобретение относится к вычисли- тельной технике и может быть использовано в арифметических устройствах специализированных цифровых вычисли" тельных машин для извлечения корня квадратного из большого массива многоразрядных чисел.

Известно- устройство, построенное на конвейерном принципе и выполненное из однотипных блоков, каждый из кото- 1О рых содержит два регистра, схему формирования и + 1 старших разрядов, два триггера и элемент И El).

Это устройство предназначено для одновременного выполнения арифметических операций над множеством чисел, но не предназначено для выполнения извлечения квадратного корня из одного массива многоразрядных чисел.

Наиболее близким к предлагаемому 2о является ус ройство, содержащее и однотипных решающих блоков, каждый из которых содержит регистр- остатка, сумматор-вычитатель, первые входы

2 которого подключены к первой группе выходов регистра остатка, регистр результата, причем вторая rpynna выходов регистра остатка предыдущего блока соединена с первой группой входов регистра остатков последующего блока, выходы регистра результата предыдущего блока соединены с соответствующими входами регистра результата последующего блока t2 >.

Известное устройство обладает недостаточно высоким быстродейст вием и производительностью при обработке массива многоразрядных чисел. Быстродействие его определяется скоростью одного такта обработки, которое равно

T = 21с,„„+ 2t + tт + 2t, где t „„ — время суммирования на сумматоре;

t©„ - время анализа знака сумматора на схеме;

3 94200

- время срабатывания триггеТа ра переполнения;

- время прохождения инфор14 мации через элементы И, Выполнение операции извлечения квадратного корня в два полутакта замедляет процесс вычислений и усложняет схему.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство для извлечения квадратного корня, содержащее м однотипных решающих блоков, каждый из которых содержит регистр остатка, первая группа выходов которого подключена к первой группе входов сумматора- вычитателя, вторая группа выходов регистра остатка подключена к соответствующим входам первой группы регистра остатка (i + 1)-ro (где i = 1,n) блока, регистр промежуточного результата, входы двух старших разрядов которого подключены соответственно к входам логической единицы и нуля устройства, выходы регистра промежуточного результата i -го блока, кроме первого, соединены с соответствующими входами регистра

30 промежуточного результата (i + 1)-го блока со сдвигом на один разряд влево и-ый решающий блок содержит также регистр конечного результата, входы которого соединены с соответствующими выходами регистра промежуточного результата, дополнительно содержит в каждом решающем блоке, кроме п-го, (i + 1) (где i - номер решающего блока элементов И-ИЛИ, причем выходы регистра промежуточного результата

40 соединены со второй группой входов сумматора-вычитателя > знаковые разряды которого соединены с управляющими входами элементов И-ИЛИ, инверсный выход знакового разряда сумматора-вычитателя, кроме п-го, соединен с информационным входом регистра промежуточного результата (i + 1) -го блока, инверсный выход сумматора- вычитателя i п-го блока 50 подключен к старшему разряду регистра конечного результата, выходы сумматора-вычислителя соединены с первой группой информационных входов элементов И-ИЛИ, вторая группа инфор- 55 мационных входов которых соединена с первой группой выходов регистра остатка (n - 1)-го блока, выходы

5 элементов И-ИЛИ подключены к входам второй группы регистра остатка (n + 1)-го блока.

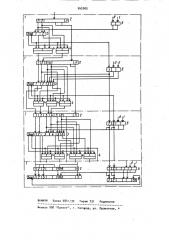

На чертеже представлена функциональная схема устройства. Устройство содержит и однотипных решающих блоков 1, каждый из которых включает регистр 2 остатка, сумматор-вычитатель 3, элементы И-ИЛИ 4, регистр 5 промежуточного результата, регистр 6 конечного результата.

В устройстве производится извле- чение квадратного корня из и-разрядных чисел за и тактов.

В первом такте в регистр 2 первого решающего блока 1 записывается первое подкоренное выражение. Иэ двух старших разрядов регистра 2 вычитается число 01 реГистра 5 в сумматоре 3.

Если частичный остаток сумматора 3 положителен (знак суммы равен нулю), разряд результата равен единице и информация с выходов сумматора 3 проходит через первую группу информационных входов элементов И-ИЛИ 4.

Если остаток сумматора 3 отрицателен, разряд результата равен нулю и на вторую группу информационных входов элементов И-ИЛИ 4 поступает значение подкоренного выражения, т.е. происходит восстановление остатка.

Во втором такте производится запись значений двух разрядов в регистр

2 через элемент И-ИЛИ 4 первого блока 1 и запись значений остальных разрядов регистра 2 первого блока в регистр 2 второго блока, а также запись первого значения результата в регистр 5 из знакового разряда сумматора 3. Значение 1-го разряда регистра 2 второго блока поступает непосредственно в 1-й разряд сумматора

3, а иэ. содержимого 2 — 4-ых разрядов регистра 2 вычитается число а101 регистра 5, где а - первое значение результата вычислений, результат вычитания поступает на элемент

И-ИЛИ 4. Одновременно в первом решающем блоке 1 в регистр 2 поступает второе подкоренное выражение, из двух первых разрядов которого вычитается .число 01 регистра 5, а результат вычитания поступает на элемент

И"ИЛИ 4.

В третьем такте в регистр 2 третьего решающего блока записываются следующие значения: в 1-й разряд— из сумматора 3 второго блока, во

2 - 4-ые разряды — из элементов (teat%+ tMAH)

Формула изобретения

5 9420

И-ИЛИ 4, в остальные разряды — из регистра 2 второго блока. В третий разряд регистра 5 записывается второе значение результата а из знакового разряда сумматора 3.второго 5 блока, в четвертый разряд - первое значение результата а из третьего разряда регистра 5 второго блока.

Значения двух первых разрядов регистра 2 третьего блока переписываются 16 непосредственно s сумматор 3, а из

3 - 6-ых разрядов регистра 2 вычитается число а1а<01 регистра 5. Одновременно во второй блок переписываются результаты вычислений пер- 15 вого блока над вторым числом, из которого на сумматоре 3 вычитаетсл число в 01. В первый блок записыва. ется третье подкоренное выражение, из двух первых разрядов которого вы- 20 читается число 01.

Результат извлечения корня из первого п-разрядного числа образуется за и тактов,,а результат вычислений

1последующих чисел будет появляться 25 на выходе регистра 6 через каждый такт. Быстродействие определяется длительностью одного такта вычислений в одном решающем блоке, которая равна где - время суммирования на сумматоре 5; й„- время задержки информации элементом И-ИЛИ 4.

При построении устройства на микросхемах 155 серии для 16-разрядных мм 0 "с или = 20 ис, т = 100 ис.

Предлагаемое устройство позволяет по сравнению с известным увеличить быстродействие вычислений. Оно особенно эффективно при обработке больших массивов многоразрядных чисел.

Устройство для извлечения квадрат ного корня, содержащее и однотипных решающих блоков, каждый из которых содержит регистр остатка, первая группа выходов которого подключена

05 6 к первой группе входов сумматоравычитателя, вторая группа выходов регистра остатка подключена к соответствующим входам первой группы регистра остатка (i + 1)-го (где

1,п) блока, регистр промежуточного результата, входы двух старших разрядов которого подключены соответственно к входам, логической единицы и нуля устройства, выходы регистра промежуточного результата 1-ro блока, кроме первого, соединены с соответствующими входами регистра промежуточного результата (1 + 1) - го блока со сдвигом на один разряд влево, и-й решающий блок содержит также регистр конечного результата, входы которого соединены с соответствующими выходами регистра промежуточного результата, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно дополнительно содержит в каждом решающем блоке, кроме и -го, (i + 1) (где 1 - номер решающего блока) элемейтов И-ИЛИ, причем выходы регистра промежуточного результата соединены с второй группой входов сумматора-вычитателя, знаковые разряды которого соединены с управляющими входами элементов И-ИЛИ, инверсный выход знакового разряда сумматоравычитателя, кроме и -го, соединен с информационным входом регистра промежуточного результата (1 + 1)-ro блока, инверсный выход сумматора-вычитателя и -го блока подключен к старшему разряду регистра конечного результата, выходы сумматора-вычитателя соединены с первой группой ин-. формационных входов элементов И-ИЛИ, вторая группа информационных входов которых соединена с первой группой выходов регистра остатка (1 - 1)-го блока, выходы элементов И-ИЛИ подключены к входам второй группы регистра остатка (1 + 1)-го блока.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

N 479111, кл. G 06 F 7/552, 1973.

2. Авторское свидетельство СССР

И 716038, кл.0 06 F 7/552, 1976 (прототип).