Цифровой генератор логарифмической функции

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик.

<„1942006 (61) Дополнительное к авт. свид-ву

И11М. Кл. (22) Заявлено 2%0880 (2! ) 2979336/18-24 с присоединением заявки ¹

G 06 F 7/556 (23) Приоритет

Государственный комитет

СССР по делам изобретений и открытий

Опубликовано 07.0782. Бюллетень №25 (53) УДК 681. 3 (088. 8) Дата опубликования описания 070782 (72) Автор изобретения

A.A. Мельник львовский ордена Ленина политехнический ййститут. (71) Заявитель (54) ЦИФРОВОЙ ГЕНЕРАТОР ЛОГАРИФМИЧЕСКОЙ ФУНКЦИИ

Изобретение относится к вычислительной технике и может быть использовано как цифровой генератор значений логарифмической функции.

Известно цифровое логарифмирующее устройстно, .содержащее входной регистр, блок вычисления характеристики, сдвигающий регистр, блок выделе-. ния остатка, результирующий регистр, блок деления, дешифраторы, блок умножения, блок априорной информации, сумматор (1) °

Недостатком устройства является низкое быстродействие и большие затраты оборудования. . Наиболее близким по технической сущности к предлагаемому является цифровое устройство для логарифмирования двоичных чисел, содержащее регистры старших и младших разрядов аргумента, три блока постоянной памяти, блок управления, ксммутатор, сумматор, выходной регистр, триггер, сдвигатель, блок управления сднигателем (2).

Однако известное устройство имеет сложную структуру из-за наличия трех блоков памяти, сдвигателя и сложного устройстна управления сдвигателем.

Цель изобретения — упрощение устройства.

Поставленная цель достигается тем, что цифровой генератор логарифмической функции, содержащий регистры старших и младших разрядов аргумента, выходной регистр, первый и второй блоки памяти, сумматор, триггер и первую группу элементов

2И-ИЛИ„ выходы которых соединены с первой группой входов сумматора, выход знака которого соединен с входом триггера, выходы сумматора соединены с входами второго блока памяти и выходного регистра, содержит промежуточный регистр, три группы элементов 2И-ИЛИ и блок синхронизации, причем выходы регистра старших разрядов аргумента соединены с первыми информационными входами элементов 2И-ИЛИ нторой группы, вторые информационные и первые и вторые управляющие входы которых соединены соответственно с выходами регистра

25 младших разрядов аргумента, перви@ и вторым выходами блока синхронизации, вьтхОды элементов 2И-ИЛИ,второй группы соединены с входами первого блока памяти, выходы которого-сое30 динены с входами промежуточного

942006 регистра и первыми информационными входами элементов 2И-ИЛИ третьей группы, выходы которых соединены с второй группой входов сумматора, прямые и инверсные выходы разрядов промежуточного регистра соединены соответственно с первыми и вторыми информационными входами элементов

2И-ИЛИ первой группы, первые и вторые управляющие входы которых соединены соответственно с третьим и четвертым выходами блока синхрониза;ции, пятый и шестой выходы которого соединены соответственно с первыми и вторыми управляющими входами элементов 2И-ИЛИ третьей группы, вторые информационные входы которых соединены С выходами элементов 2И-ИЛИ четвертой группы, первые и вторые управляющие входы которых соединены соответственно с инверсным и пряьым выходами триггера, выходы второго блока памяти соединены с первыми информационными входами элементов

2И-ИЛИ с первого по (n-l)-й, где n— разрядность аргумента четвертой группы, и с вторыми информационными входами элементов 2И-ИЛИ с второго по и-й четвертой группы, седьмой и восьмой выходы блока синхронизации соединены соответственно с входами

i ðèåìà кода промежуточного регистра и сумматора.

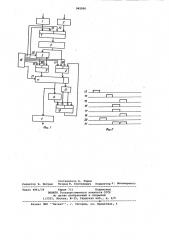

На фиг.l представлена блок-схема генератора; на фиг.2 — вариант временной диаграммы работы блока синхронизации. цифровой генератор логарифмирующей функции содержит регистры 1 и 2 старших и младших разрядов аргумента, регистр 3 промежуточный, выходной регистр 4, блоки 5 и 6 памяти, группы 7-10 элементов 2И-ИЛИ, сумматор 11 и триггер 12, управляющие входы 13-18 групп элементов 2И-ИЛИ, блок 19 синхронизации, входы 20 и 21 приема кода промежуточного регистра и сумматора.

Блок 19 синхронизации может быть реализован с помощью генератора импульсов и элементов задержки (фиг.2)

Устройство производит вычисление двоичного логарифма от нормализованного аргумента х(сх C 1) на основе соотношений

Zog x = Jog<(xl + х2)

= Log xi + Ход (1 + — ) х2. хй. х1

hogg = — = Zoggx2 1?oggx1 где xl - число, образованное n/2 старшими разрядами аргумента; х2 — число, образованное n/2 младшими разрядами аргумента; п — число разрядов аргумента.

Устройство работает следующим об- разом.

На первом этапе работы устройства значение xl из регистра 1 старших разрядов аргумента поступает через группу 7 элементов 2И-ИЛИ по сигналу, поступающему по управляющему входу 13 на блок 5 памяти, в котором хранится таблица логарифмов числа

xl Число же х2 приводится к диапа10 зону изменения xl и тем самым для вычисления его логарифма используется та же таблица, Это вытекает из следующего соотношения:

Й.

2og

= Рос(Х" 2 +„Jog@ 2 = hogg х 2, где х 2 = х2 ° 2 .

Из блока 5 снимается значение

Log xi и поступает на промежуточный регистР 3. Значение регистра 2 младших разрядов аргумента поступает на блок 5 памяти через группу 7 элементов 2И-ИЛИ по сигналу, поступающему по управляющему входу 14, и из блока

25 5 снимается значение 2W2x(2 По сигналам, поступающим по управляющим входам 16 и 17, инверсное содержимое регистра 3 (-Jog xi ) и значение с выходов блока 5, равное ьв.нтиссе

2og0x 2, проходят через группы 8 и 9 элементов 2И-ИЛИ на сумматор 11. На выходе сумматора 11 формируется,„ согласно формуле, значение Xagg †„„, мантисса которого передается на вход блока 6 памяти, где хранится таблица промежуточных преобразователей. Этот блок осуществляет табличное преобра-. зование значения мантиссы 2оЧ,1 — в х1

Х1 соотнетстнующее нннченне н,т(Eel

Фх1 1

40 х / где q — - такое целое число, что .П

2 1 2 — < 2 + 1х1

Число q равно значению — ", т. е. Равно сдвигу числа х2 относительно числа

xl плюс знак сумматора, значение которого при сложении мантисс (- Jog xl) и logy х2 запоминается на триггере 12 промежуточного результата. Значение с выхода блока б памяти проходит через группу 10 элементов 2И-ИЛИ или со сдвигом на

n/2 разрядов, если содержимое триггера 12 равно нулю, или со сдвигом и на «2 + 1 Разрядов, если содержимое триггера 12 равно единице. Таким образом, на выходе группы 10 элементов 2И-ИЛИ из значения

+х2

2og (1 + 2 — ) получаем зн аче н ие

xl х2

Ход,1(1 + †), что справедливо ввиду

-ФИ) выполнения с точностью до 2 пркближенногс равенства

3?og < (1+ — ) «» 2 Zog (1+2 — )х2 -Ч Фх2

942006

Цеги приема кода промежуточного регистра 3 и сумматора 11 могут управляться дополнительными управляющими разрядами регистров 1 и 3 и блоков памяти.

На втором этапе работы устройства по сигналам 15 и 18 через группы 8 и 9 элементов 2И-ИЛИ на сумматор 1 поступает содержимое регистра 3, равное 2oggxI и значение с выхода группы 10 элементов 2И-ИЛИ. В резуль- 0 тате сложения на сумматоре образуется по исходной формуле искомое значение Zog x, которое передается на выходной регистр 4 и из него на выход устройства. 15

Как видно, предлагаемое устройство намного проще известного поскольку содержит два блока постоянной памяти вместо трех и не содержит сложных и требующих больших аппара- 20 турных затрат сдвигателя и устройства .управления сдвигателем, а по эффективности выполнения операции логарифмирования оно не уступает известному устройству. 25

Формула изобретения

Цифровой генератор логарифмической функции, содержащий регистры старших и младших разрядов аргумента, выходной регистр, первый и второй блоки памяти, сумматор, триггер и первую группу элементов 2И-ИЛИ, выходы которых соединены с первой группой входов сумматора, выход знака которого соединен с входом триггера, выходы сумматора соединены с входами второго блока памяти и выходного регистра, о т л и ч а ю40 шийся тем, что, с целью упрощения, он содержит промежуточный регистр, три группы элементов 2И-ИЛИ и блок синхронизации, причем выходы регистра старших разрядов аргумента 45 соединены с первыми информационными входами элементов 2И-ИЛИ второй группы, вторые информационные и первые и вторые управляющие входы которых соединены соответственно с выходами регистра младших разрядов аргумента, первым и вторым выходами блока синхронизации, выходы элементов 2И-ИЛИ второй группы соединены с входами первого блока памяти, выходы которого соединены с входами промежуточного регистра и первыми информационными входами элементов

2И-ИЛИ третьей группы, выходы которых соединены с второй группой входов сумматора, прямые и инверсные выходы разрядов промежуточного регистра соединены соответственно с первыми и вторыми. информационными входами элементов 2И-ИЛИ первой группы, первые и вторые управлякщие входы которых соединены соответственно с третьим и четвертым выхода-! ми блока синхронизации, пятый и шестой выходы которого соединены соответственно с первыми и вторыми управляющими входами элементов 2И-ИЛИ третьей группы, вторые информационные входы которых соединены с выходами элементов 2И-ИЛИ четвертой группы, первые и вторые управляющие входы которых соединены соответственно с инверсным и прямым выходами триггера, выходы второго блока памяти соединены с первыми информационными входами элементов 2И-ИЛИ с первого по (n-1)-й, где и-разрядность аргумента четвертой группы, и с вторыми информационными входами элементов 2И-ИЛИ с второго по и-й четвертой группы, седьмой и восьмой выходы блока синхронизации соединены соответственно с входами приема кода промежуточного регистра и сумматора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 624233, кл. G 06 F 15/20, 1976.

2. Авторское свидетельство СССР

Р 593212, кл. G 06 F 5/38, 1978 (прототип) .

942006 д

Ф

17

ar

Й

2l Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5 филиал ППП, Патент, г. Ужгород, ул. ПроЕктная, 4

Заказ 4841/39

Составитель А. Зорин

Редактор В. Петраш Техред Ж. Кастелевич Корректор У. Пономаренко