Устройство переменного приоритета

Иллюстрации

Показать всеРеферат

ОП ИСАИ И Е

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()))942021

Союз Советсиик

Соцнмнстическна.

Республик (61) Дополнительное к авт. свид-ву (22) Заявлено 290676 (21) 2375809/18-24 с присоединением заявки J4 (51)М. Кл.

G 06Р 9/46

1Ьаударатвааый камнтет

СССР аю делам изобретений н открытий (53) 3glK 681.325 (088.8 ) (23) Приоритет

Опубликовано 070782. Бюллетень М 25

Дата опубликования описания . 070782 )

В.П.Школин, В.И.Тужилин и С.Ф.Михайлов (72) Авторы изобретения (71) Заявитель (5 4 ) УСТРОЙСТВО ПЕРЕМЕННОГО ПРИОРИТЕТА

Изобретение относится к вычислительной технике в частности, к приоритетным устройствам и может быть использовано в системах обмена данными между многими абонентами и ЦВМ.

Известное устройство переменного приоритета, содержащее подключенные к абонентам формирователи выбора, подключенные ко входам схемы фиксации динамического приоритета, формирователи записи, а также триггерный регистр блокировки с подключенными к его выходам первыми входами схем совпадения, вторые входы которых присоединены к выходам формирователей выбора, а выходы подключены ко входам формирователей записи, позволяет .обеспечить подключение абонентов в

ЭВМ в соответствии с фиксированными или динамическими приоритетами 31), що

Однако известное устройство не обеспечивает смены приоритетов в процессе работы программным способом или с пульта оператора, и не исклю2 чает ложные или аварийные режимы работы, которые могут возникать при переключении коммутационных элементов . приоритетных схем, что существенно уменьшает эффективность использова" ния приоритетного устройства в циф ровых вычислительных комплексах.

Наиболее близким к изобретению по технической сущности и достигаемому положительному результату является устройство переменного приоритета, содержащее блок хранения кодов приоритетов, выходы которого соединены с кодовыми входами коммутатора, регистр запросов, разрядные выходы которого соединены с соответствующими управляющими входами коммутатора, причем первые и вторые разрядные вхо-, ды регистра запросов соединены соответственно с запросными. входами устройства и с разрешающими выходами коммутатора, сигнальный выход регистра запросов и кодовый вход блока хранения кодов приоритетов и опрос1

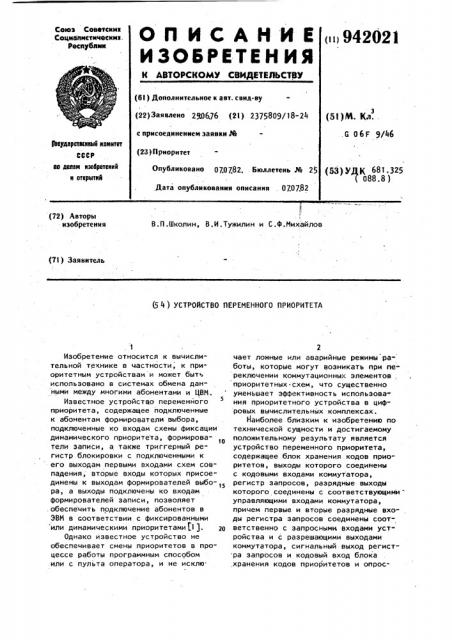

4 блок 3 фиксации ошибки со входом 4 регистр 5 запросов, блок б хранения кодов приоритетов, блок 7 дешифрации кодов абонентов, элемент ИЛИ - И 8, запросные коды 9, входы 10-13,блок

14 управления, управляющие кодовые входы 15 коммутатора, разрешающие выходы 1б коммутатора, опросный вход

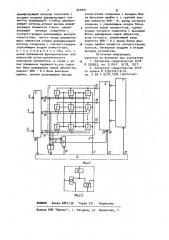

17 коммутатора, сигнальный выход 18 регистра запросов, кодовый и управляющий входы 19 и 20 блока хранения кодов приоритетов. . Каждый дешифрирующий элемент матрицы {фиг.2 ) содержит дешифратор 21 и элементы И 22 и 23.

Блок хранения кодов приоритетов ,может быть выполнен в виде набора регистров-счетчиков, кодовые входы которых соединены с кодовым входом блока, суммирующие входы соединены .с управляющим входом блока, запускающие входы — с выходами блока дешифрации кодов абонентов, а выходы - с кодовыми входами коммутатора.

Блок дешифрации кодов абонентов ,может быть выполнен в виде группы дешифраторов,число которых равно .числу абонентов,входы дешифраторов соединены со входом блока, а выходы — с выходами блока. 94202 ный вход коммутатора соединены соответственно с первым выходом устройства, с первым и вторым управляющими входами устройства, а коммутатор выполнен в виде дешифрирующей матрицы, в которой первые входы дешифрирующих элементов строки соединены с соответствующими кодовыми входами коммутатора, опросный вход коммутаторасо вторыми входами дешифрирующих эле- ««« ментов последнего столбца дешифрирую" щей матрицы, первые выходы дешифрирующих элементов столбца дешифрирующей матрицы соединены со вторыми входами дешифрирующих элементов предыдущего столбца дешифрирующей матрицы, вторые выходы дешифрирующих элементов строки дешифрирующей матрицы соединй ны с соответствующим разрешающим выходом коммутатора третьи входы де-:

zo шифрирующих элементов строки дешиф" рирующей матрицы соединены с соответствующим управляющим входом коммутатора(2«.

Известное устройство не позволяет работать в режиме динамического изменения приоритетов, а также обладает незначительной надежностью, поскольку не имеет блока сигнализирующего о возникающих ошибках. зо

Цель изобретения — расширение функциональных возможностей устройства путем обеспечения динамического изменения приоритета и повышение надежности.

Поставленная цель достигается тем, что устройство содержит блок дешифрации кодов абонентов, элементы

ИЛИ - И и блок фиксации ошйбки, причем разрешающие выходы коммутатора соединены со входами блока фиксации ошибки и с группой входов элемента ИЛИ - И, выход которого соединен с управляющим входом блока хранения кодов приоритетов, группа входов которого соединена с выходами блока дешифрации кодов абонентов, вход которого, управляющий вход элемента ИЛИ - И и выход блока фиксации ошибки являются соответственно тре". тьим, четвертым входами и вторым выхо- @ дом устройства.

На фиг. 1 представлена структурная схема устройства;. на фиг, 2 - схема дешифрирующего элемента матрицы.

Устройство переменного приоритета (фиг. 1) содержит коммутатор 1, выполненный в виде дешифрирующей матрицы с дешифрирующими элементами 2, Устройство может работать в режиме сменных и динамических приоритетов.

При сменных приоритетах для каждой задачи или группы задач абоненты имеют одну расстановку приоритетов, при переходе к решению другой задачи или группы задач приоритеты абонентов изменяются.

При динамических приоритетах осуществляется изменение кодов приоритетов для всех абонентов после каждого сеанса обмена с абонентами. Например, абонент со старшим приоритетом, получив разрешение на обмен, для организации следующего обмена становится последним в очередь, или после каждого сеанса обмена приоритеты всех абонентов изменяются на единицу по

"кругу".

Устройство работает следующим образом.

Перед началом обмена абонентов с

ЦВИ в режиме сменных приоритетов производится запись кодов приоритетов, поступающих с,блока 14 управления на вход 12 устройства для каждого абонента в соответствующие им регистрысчетчики блока 7, для чего из блока

942021

Формула изобретения

14 управления поступают на вход 13 устройства коды абонентов, разрешая тем самым последовательную запись в блок 7 кодов приоритетов, поступающих на вход 12. 5

Работа устройства начинается с выдачи регистром 5 на выход 18 сигнала наличия запросов одного или нескольких абонентов., В ответ блок 14 управления выдает на вход 17 коммутатора 1 сигнал, поступающий на первый вход элементов И

23 фиг.2) крайнего правого (последнего ) столбца матрицы.

При наличии на втором входе эле- 15 мента И 23 разрешающего уровня с вы-. хода дешифратора 21, на выход 16 коммутатора 1, а, следовательно, и на вход регистра 5 запросов поступает сигнал. 20

При наличии запросов от абонента с высшим приоритетом ему выдается сигнал, разрешающий обмен, дальнейшее распространение сигнала опроса по дешифрирующим элементам 2 коммутато- 25 ра 1 прекращается, и абонент снимает свой запрос.

Если же запрос отсутствует, на соответствующий вход 15 коммутатора 1 подается сигнал, срабатывает эле- зо мент И 22 и распространение сигнала опроса по элементам 2 коммутатора продолжается.

По завершении обмена блок 14 управления вырабатывает новый сигнал опроса, если имеется сигнал на выходе 18 регистра 5 запросов. Подобная операция повторяется до пропадания сигнала на выходе 18.

При необходимости изменить коды приоритетов, операция записи кодов приоритетов повторяется программным способом или с пульта оператора.

Режим работы устройства с динами 1 ческими приоритетами аналогичен из" вестному режиму с той разницей,что при прохождении сигнала опроса через коммутатор 1 он поступает также на элемент ИЛИ вЂ” И 8. При наличии управляющего сигнала динамической смены приоритетов на входе 10, сигнал с выхода элемента ИЛИ вЂ” И 8 поступает на вход 20 блока 6 и коды приоритетов увеличиваются на единицу, а код самого, младшего приоритета

55 становится кодом старшего приоритета. Таким образом, уменьшается время ожидания на обслуживание абонентов с низшими приоритетами.

Блок 3 осуществляет непрерывный аппаратный контроль устройства по модулю два, при этом s случае выхода из строя дешифрирующих элементов

2 коммутатора 1 или ошибке при записи кодов приоритетов одновременно присутствуют сигналы на нескольких входах блока 3, при этом блок 3 фиксирует наличие ошибки и передает этот сигнал с выхода 4 в блок 14 управления.

Предлагаемое устройство по сравнению с известным имеет следующие преимущества: при незначительных дополнительных затратах позволяет работать не только со сменными приоритетами, но и с динамическими не вводя дополнительных перенастроек устройства и дополнительных перекоммутаций; введение блока 3 позволяет осуществлять контроль работы устройства в процессе эксплуатации, что является очень важным вопросом при организации обмена абонентов с ЭВИ, так как при ошибочной выдаче разрешения обмена нескольким абонентам может привести к серьезным сбоям или отказам системы.

Устройство переменного приоритета, дэдержащее блок хранения кодов пр оритетов, выходы которого соединены с кодовыми входами коммутатора, регистр запросов, разрядные выходы которого соединены с соответствующими управляющими входами коммутатора, причем первые и вторые разрядные входы регистра запросов соединены соответственно с запросными входами устройства и с разрешающими входами коммутатора, сигнальный выход регистра запросов, кодовый вход блока хранения кодов приоритетов и опросный вход коммутатора соединены соответственно с первым выходом устройства, с,первым и вторым управляющими входами устройства, а коммутатор выполнен в виде дешифрирующей матрицы, в которой первые входы дешифрирующих элементов строки соединены с соответствующими кодовыми входами коммутатора, опросный вход коммутатора соединен с вторыми входами дешифрирующих элементов последнего столбца де шифрирующей матрицы, первые выходы дешифрирующих элементов столбца

942021 8 коммутатора соединены с входами блока фиксации ошибки и с группой входов элемента ИЛИ - И, выход которого соединен с управляющим входом блока хранения кодов приоритетов, группа входов которого соединена с выходами блока дешифрации кодов абонентов, вход которого, управляющий вход элемента ИЛИ - И и выход блока фик1р сации ошибки являются соответственно, третьим, четвертым входами и вторым выходом устройства, Источники информации, принятые во внимание при экспертизе

1, Авторское свидетельство СССР

N 359653, кл. G 06F 9/18, 1971.

2. Авторское свидетельство СССР по заявке N 23ЯЗЗО/18-24. кл. G 06 F 9/18,1976 (пРототип). дешифрирующей матрицы соединены с вторыми входами дешифрирующих элементов предыдущего столбца дешифри" рующей матрицы, вторые выходы дешифрирующих элементов строки дешифрирующей матрицы соединены с соответствующим разрешающим выходом коммутатора, третьи входы дешифрирующих элементов строки дешифрирующей матрицы соединены с соответствующим управляющим входом коммутатора, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем динамического изменения приоритета, а также с целью повышения надежности оно содер1 жит блок дешифрации кодов абонентов,. элемент ИЛИ вЂ” И и блок фиксации ошибки, причем разрешающие выходы

©иг.f

Фиг.2

8НИИПИ Заказ 4841/39 Тираж 731 Подписное

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4