Устройство для вычисления обратной функции

Иллюстрации

Показать всеРеферат

Союз Советскик

Социалистичесиик

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (iii 942035 (61) Дополнительное к авт. свил-ву(22) За весно 19. 12. 80 (21) 3220523/18-24 с присоединением заявки РЙ— (23) Приоритет— (5! )М. Кл.

0 06 F 15/328

9кудерстеапвй комитет

СССР во аелаи вэобретениМ и открытий

Опубликовано 07. 07. 82. Бюллетень Юв 25

Дата опубликования описания р7,р7 82 (53) УДК681. 322 (088.8) И.И. Ледовской, В,Ф. Арсени, А.В. Скакун, В.С. Абрамович и P.À. Романенко" (72) Авторы изобретения

Таганрогский радиотехнический институт,, им. В.Д Калмыкова (7l) Заявитель (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОЙ

ФУНКЦИИ го

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройстB.

Известны вычислительные устройст5 ва для воспроизведения обратных функций (1) и (. 2).

Недостатками известных устройств являются низкая скорость вычислений и значительные аппаратурные затраты.

Наиболее близким по технической сущности к предлагаемому устройству является устройство, содержащее три цифровых интегратора, один из которых (третий) является следящим, причем первые входы первого и второго интеграторов соединены со входом устройства, выходы первого и второго интеграторов соединены соответственно с первым и вторым входами третьего интегратора, выход которого соединен со вторыми входами первого и второго интеграторов (3g.

1

При вычислении Функци т = — для х значений х, приближающихся к нулю, погрешность вычислений в указанном устройстве резко возрастает.

Целью изобретения является повышение точности вычислений для значений х, близких к нулю.

С этой целью в устройство для вычисления обратной фучкции, содержащее первый, второй и третий интеграторы, причем вход устройства соединен с первыми входами первого и второго интеграторов, а выход третьего интегратора подключен ко второму входу второго интегратора, введены четвертый интегратор, первый, второй и третий сумматоры, регистр сдвига, регистр коррекции и коммутатор, при этом первый и второй входы первого сумматора соединены с выходами соответственно первого и второго интегратора, а выход первого сумматора присоединен к первому входу третьего. ральных функций интеграторов 1;2 и

4 и в регистр 8 заносятся соответ- . ственно величины oL,с(о - х, у х . Вычисление функции у = начйнается s устройстве с момента подачи. на вход устройства приращений

dy. Приращения d поступают на первые входы интеграторов 1 и 2 и сумматора

6. Проходя через сумматор 6 и накап10 ливаясь в регистре 8, приращения d „ образуют текущее значение переменной х, которое поступает на вход коммутатора 10. В этом коммутаторе в зависимости от значений х производится — !5 формирование корректируЮщего множителя сС, значение. которого записывается в регистр 9. Значение с вырабатывается близким или равным х, но кратное 2, так, чтобы х > о . . 20 Например, если х = 0,126, то сс =

= 0,125 = 2 . Из регистра 9 значение aL. параллельным кодом передается на второй вход интегратора 4, а последовательным кодом - на вход сумматора 7, где из него вычитается значение х, поступающее из сумматора

6. Образованная в сумматоре 7 разность сС- х поступает на второй вход интегратора 1.. С выходов интег30

35 ао

50

3 94 интегратора, выход которого соединен с первым входом четвертого интегратора, а выход четвертого интегратора подключен ко второму входу третьего интегратора, первый и второй входы второго сумматора соединены соответственно со входом устройства и первым выходом регистра сдвига, а выход второго сумматора подключен ко входу регистра сдвига и первому входу третьего сумматора, вход коммутатора соединен со вторым выходом регистра сдвига, а выход - со входом регистра коррекции, параллельный и

:последовательный выходы которого под ключены соответственно ко второму входу четвертого интегратора и второму входу третьего сумматора, выход которого соединен со вторым входом первого интегратора, причем, выход третьего интегратора является выходом устройства.

3а счет введения новых блоков и связей в предлагаемом устройстве значительно повышается устойчивость и точность вычислений для значений х, приближающихся к нулю.

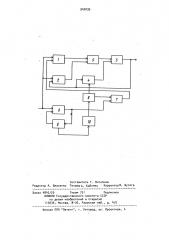

На чертеже приведена функциональная схема устройства.

Устройство содержит первый, второй, третий и четвертый интеграторы, 1 - 4 (интегратор 3 - следящий), первый, второй и третий сумматоры

5 -. 7, регистр 8 сдвига, регистр 9 коррекции и коммутатор 10. Первые входы интеграторов 1 и 2 соединены со входом устройства, а выходысо входами сумматора 5, выход которого соединен с первым входом интегратора 3, выход интегратора 3 соединен с выходом устройства, вторым входом интегратора 2 и первым входом интегратора 4. Первый вход сумматора 6 соединен со входом устройства, второй вход - с первым выходом регистра 8, а выход - с первым входом сумматора 7 и входом регистра

8. Второй выход регистра 8 соединен со входом коммутатора 10, выход которого соединен со входом регистра

9, первый выход которого соединен со вторым входом интегратора 4, а второй выход - со вторым входом сумматора 7. Выход сумматора 7 соединен со вторым входом интегратора 1.

Работа устройства заключается в следующем, Перед началом вычислений на входы начальных значений подынтег2035 4 ратора 1 и 2 на входы сумматора 5 поступает приращение dx, умноженное соответственно на величины ос - х и у.

Полученная сумма { о(- x)dx.б у. dx c выхода сумматора 5 поступает на первый вход следящего интегратора 3 . С выхода следящего интегратора снимается приращение dy, поступающее на второй вход интегратора 2 и на первый вход интегратора 4. С выхода интегратора 4 приращение dy, умноженное на величину с(., поступает на второй вход следящего интегратора 3.

Предлагаемое устройство реализует дифференциальное уравнение

dy = — g(4- x)dx - ydx) (1)

Ф. при заданных начальных условиях, решением которого является функция

1 у = . Дифференциальному уравнению (1) соответствует разностное уравнение у =(2 — - — ) у + (-1+ — ).у, (2) xj h3 х (б4 0 по которому ведутся вычисления в устройстве. Разностная схема (2) должна быт ь устой чи вой, т . е ° иметь решение, сводящееся к решению дифференциального уравнения (1) при

hw 0. Устойчивость схемы (2) опреде ляется следующим образом. Представим (2) в виде 5

R .y° .р, jц где

Y„. = У„У„ „

jfR Ц (2 -Д- - — / 4» / 14--(" / (3) Если о „ х1 и h О, то из 1,3) по- 20 лучаем P R> )(" С, где С = ехр(« ) к л

14 =, х„-б«а, Ь).

Таким образом, из ограниченности оператора Rg следует устойчивость и сходимост ь (2) . За счет выбора параметра о достигается ограниченность оператора Rg для всех х е Pa,Ь), в то вреМя как в известном устрой- 3Е стве С = 1 и ограниченность оператора имеет место не для всех значений х„g «а, Ъ).Иетодическая погрее-. ность равна (4) Следовательно, введение параметра незначительно увеличивает объем оборудования, но позволяет вести вычис- 10 ления на всем интервале изменения переменной при заданной точности, так как вычислительная схема становится устойчивой и методическая погрешность Ey 0.

Предлагаемое устройство предназначено для использования в навигационных вычислителях, системах цифрово,го управления станками, в работах, микрокалькуляторах и другой радиоэлектронной аппаратуре.

R = 2 - †. — — -1 + — )

x h х1

О(1- cl d„ ) В евклидовом пространстве имеем

942035 6 формула изобретения

Устройство для вычисления обрат-. ной функции, содержащее первый, второй и третий интеграторы, причем вход устройства соединен с первыми входами первого и второго интеграторов, а выход третьего интегратора .подключен ко второму вхбду второго интегратора, о т л и ч а ю щ е еtO с,я тем, что, с целью повышения точности вычислений, оно содержит, четвертый интегратор, первый, второй и третий сумматоры, регистр сдвига, регистр коррекции и коммутатор, при

15 этом первый и второй входы первого сумматора соединены с выходами соответственно первого и второго интег- ратора, а выход первого сумматора присоединен к первому входу третьего интегратора, выход которого соединен с первым входом четвертого интегратора, а выход четвертоГо интегратора подключен ко второму входу третьего интегратора, первый и второй входы второго сумматора соединены соответственно со входом устройства и первым выходом регистра сдвига, а выход второго сумматора подключен ко входу регистра сдвига и первому входу третьего сумматора, вход коммутатора соединен со вторым выходом регистра сдвига, а выходсо входом регистра коррекции, параллельный и последовательный выходы

35 которого подключены соответственно ко второму входу четвертого интегратора и второму входу третьего сумматора, выход которого соединен со вторым входом первого интегратора, причем выход третьего интегратора является выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Патент США и 3648038, кл. G 06 F 7/39, 1971.

2. Авторское свидетельство СССР 546881, кл. G 06 F 7/38, !977.

3. Неслуховский К.С. Цифровые дифференциальные анализаторы. M., "Иашиностроение", 1968, с. 95, рис. 31.

Составитель Г. Виталиев.

Редактор А. Власенко Техред д. Бабинец Корректор В. Бутяга

Заказ 4842/20 Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4