Устройство для обучения

Иллюстрации

Показать всеРеферат

Г. Я. Соголов, И. Г. Буренков, В. А. М н и С; Г. Марченко

N 4

- ., 1) (72) Авторы изобретения (7!) Заявитель (54) УСТРОЙСТВО ДЛЯ ОБУЧЕНИЯ

Изобретение относится к обпасти автоматики и вычислительной техники, в частности к обучающим устройствам, и может быть использовано при изучении запоминающих устройств вычислитель5 ной техники.

Известно устройство, содержащее блок памяти, состоящий иэ элементов памяти, адресный и числовой блоки и позволяющее изменять состояние элементов памяти и производить индикацию этих состояний(1) .

Известно также устройство, содержа щее бпок памяти, состоящий из элементов паьяти, адресный и числовой бпокн, и позволяющее исследовать физические процессы в блоке памяти при записи и считывании информации (2) .

Наиболее бпиэким к предпагаемому является устройство, содержащее бпок памяти, состоящий из элементов памяти 20 с двумя адресными входами, разрядным входом и выходом каждый, адресный блок, числовой блок и бпок программного управления, первый выход которого

2 соединен со входом адресного бпока, второй выход- со вторым входом числового блока 3 .

Недостатком этого устройства является применение в бпоке памяти неперестраиваемых элементов памятя, тесно связанных между собой, а также наличие жестких связей между бпоками памяти и адоесным и числовым блоками, что позволяет моделировать структуру запоминающего устройства только одного типа на элементах памяти одной физической природы и исключает возможность изменения конфигуращ и блока памяти

{количества ячеек памяти и их разрядность), нри этом синтез бпока памяти невозможен.

Цель изооретения - расширение аи дакти ческик возможностей устройства, а также по

-вышение эффективности обучения за счет придания устройству способности изменения структуры.

Указанная цель достигается тем, что в устройство, содержащее блок памяти, 942119 формирователь управлякших импульсов, первый выход которого соединен с входом формирователя адресов, а второй выход — с первым входом формирователя кодов числа, введены последовательно S включенные блок изменения структуры изучаемого объекта и коммутатор, распределитель кодов и блок элементов

И-ИЛИ, выход которого соединен с вторым входом формирователя кодов числа, пер- >е вый вход - с выходом блока памяти, а второй вход - с вторым входом блока изменения структуры изучаемого объекта, третий выход которого подключен к первому входу блока памяти, а вход - к И третьему выходу формирователя управлякяцих импульсов, первый вход распредслителя кодов соединен с выходом формирователя кодов числа, второй вход — с четвертым выходом блока изменения 20 структуры изучаемого объекта, а выход— с вторым входом блока памяти, третий вход которого через коммутатор подключен к выходу формирователя адресов.

Причем блок изменения структуры 25 изучаемого объекта содержит последовательно включенные формирователь кода структуры и распределитель импульсов, выходы и вход которого являются соот ветственно выходами и входом блока. За

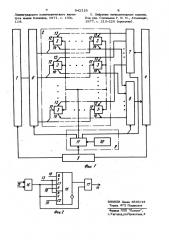

На фиг. 1 показана структурная схема предлагаемого устройства; Hs фиг. 2принципиальная схема запоминающего элемента блока памяти.

Устройство содержит формирователь 1 адресов, блок 2 памяти, состоящий из запоминающих элементов З,формирователь

4 кодов числа, формирователь 5 управляющих импульсов, коммутатор 6, распределитель 7 кодов, блок 8 элементов ИИЛИ, блок 9 изменения структуры изучаемого объекта, состоящий, например, из формирователя 10 кода структуры и распределителя 11 импульсов. Адресные, разрядные входы и разрядные выходы каж- дого элемента 3 подключены к шинам 1214 соответственно. Формирователь 5 пред; назначен для управления формированием и выдачей адресов и чисел, формирования последовательности сигналов управления блоками устройства, зависящей от структуры моделируемого запоминаюшего устройства.

Элемент 3 вып олнен 1(фиг. 2) на основе известного триггера 15 со сложной входной логикой, имекщего два 6-, SS связанных по И, один R, — âõîäû, синхронизируемые по С1, .()-вход, синхронизируемый по С2, и содержит первый двухвходовой элемент И 16, входы которого подключены к шине 12 и являются адресными входами элемента 3, а выход соединен с (- и Cl-входами триггера.

15, второй двухвходовой элемент И 17, первый вход которого соединен с выходами триггера 15, второй вход - с выходом первого элемента И, выход подключен к шине 14 элемента 3. Шина 13 разрядного элемента подключена к )- и первому 5 --входам триггера 15. Второй

5-, К- и С2-входы триггера 15 образуют управляющий вход элемента 3 и подключены к шинам 18-20 соответственно, соединенным со вторым выходом блока 9.

При синтезе блока памяти запоминающего устройства типа Зф адресные шины

Х блока 2 формируются путем коммутации между собой одного из адресных входов

12 нескольких элементов 3, а адресные шины У вЂ” путем коммутации между собой других входов 12. Образованные шины

X и У подключаются коммутатором 6 к формирователю 1. При синтезе блока памяти запоминаккцего устройства типа

23 формируются адресные шины только по одной иэ координат.

Разрядные входные и выходные шины блока 2 памяти формируются путем коммутации шин 13 и 14 соответственно требуемых элементов 3, Распределитель 7 и блок 8 в соответствии с заданным типом структуры ббеспечивают требуемые подключения разрядных входов и выходов каждого элемента 3 к выходу и первому входу формирователя 4 соответственно.К оммутатор 6, распределитель 7 и блок 8 управляются сигналами распределителя 11, который, в свою очередь, управляется формирователем 10.

При этом конфигурация (количество ячеек памяти и их разрядность) синтеэируемого блока памяти ограничивается соотношением и м-и, где Ю- количество ячеек памяти, Q - разрядность ячеек памяти;

hl — общее количество элементов 3.

При заданном Ч величина N ограничена количеством выходов адресного блока и зависит от структуры синтеэируемого запоминакщего устройства, а величина ограничена количеством вторых входов числового блока.

Предлагаемая схема элементов 3 позволяет моделировать блоки памяти запо1. Устройство дпя обучения, содержащее бпок памяти, формирователь управляющих импульсов, первый выход aemporo соединен с входом формирователя адресов, а второй выход — c первым входом формирователя кодов числа, о т л и ч аю щ е е с я тем, что, с целью расширения дидактичесиих воэможностей устройства, оно содержит последовательно включенные блок изменения структуры изучаемого объекта и коммутатор, распределитель кодов и блок элементов И-ИЛИ, выход которого соединен с вторым входом формирователя кодов числа, первый входс выходом блока памяти, а второй входс вторым выходом блока изменения структуры изучаемого объекта, третий выход которого подключен к первому входу блока памяти, а вход — к третьему выходу формирователя управляющих импульсов, первый вход распределителя кодов соединен с выходом формирователя кодов числа, второй вход — с четвертым выходом блока изменения структуры изучаемого обьекта, à выход — с вторым входом блока памяти, третий вход которого через коммутатор подключен к выходу фор мирователя адресов.

2. Устройство по п.1, о т л и ч а ющ е е с я тем, что блок изменения структуры изучаемого объекта содержит последовательно включенные формирователь ко да структуры и распределитель импульсов, выход и вход которого являются соответственно выходами и входом блока.

Источники информации, принятые во внимание при экспертизе

1. Патент Великобритании

% 1341843, кл. 609 В 5/00, опублик. 1973.

2. Строганов P. П. Вычислительные, устройства дискретного действия. Иэд.

5 9421 минакацих устройств, собранные на элементах с разрушением информации при считывании, например, ферритовых сердечниках с прямоугольной петлей гистерезиса, и элементах, информация которых при считывании не разрушается, например, на тонких магнитных пленках. Для этого изменение режима работы элементов накопителя производится блоком иаиенения структуры изучаемого объекта. <о

В режиме Считывание с разрушением" после записи информации из некоторой ячейки блока памяти в числовой блок триггеры этой ячейки обнуляются по шине 19. В этом режиме запись М (восстановление) информации в ячейку памяти производится по шине 13 элементов 3 с использованием их g -входов, дпя чего управлякаций сигнал распределителя 11 подается по шине 18 щ на вторые 6-входы всех триггеров 15.

Использование 5-входа для записи информации в этом режиме определяется необходимостью моделирования этих запоминающих элементов, принципы работы которых позволяют производить в них зались только кода единицы.

В режиме "Считывание без разрушения управляющий сигнал распределителя 11 подается не по шине 18, а по ши- sy не 20, обеспечивая запись новой информации без стирания старой путем использования при этом g входа триггера 15.

Устройство состоит иэ лицевой панеап и электрической схемы. На лицевой

Л панели изображена структурная схема устройства и размещены все гнезда, органы управления устройством и элементы индикации.

Устройство работает следующим образом.

В comâåòñòânn с вариантом задания обучаемый устанавливает на датчиках формирователя 10 условные номера типа структуры, способа функционирования запоминающих элементов и варианта конфигурации блока памяти. В соответствии с этими номерами распределитель 11 выдает определенные комбинации сигналов на коммутатор 6, распределитель 7 и блок 8, которые обеспечивают заданные коммутации входов и выходов запоминающих рлементов 3.

В формирователе 5 обучаемый формирует требуемую последовательность сигналов и, изменяя адреса и числа, произвэSS дит запись информации s блок 2 памяти и последующее ее считывание. Контроль правильности действий обучаемого произ19 6 водится путем сравнения записываемой и считанной информации.

Предлагаемое устройство с расширенными функциональными возможностями позволяет моделировать структуры эапоминакщих устройств типов 29 и 35, выполненных as запоминакщих с разрушением информации при считывании и беэ .ее разрушения, синтеэировамь блок памяти

;для этих структур различной конфигура ции, что, увеличивая количество вариантов заданий, способствует индивидуализации обучения и повышению его эффективности.

Формула изобретения

Э. Цифровые вычислительные машины. од ред. Соловьева Г. И. М., Атомиэдат, 9,77, с. 213-220 (прототип).

Pup f

ВНИИПИ Заказ 4849/44

Тираж 472 Подписное

Филиал ППП Патент", г, Ужгород,ул.Проектная,4

7 942110

Ленинградского политехнического института имени Калинина, 1971, с. 105 П

118, 1