Запоминающее устройство

Иллюстрации

Показать всеРеферат

Союз Советсиик

Социалистмчесиик

Республик

О П И С А Н И Е ()942141

ИЗОБРЕТЕНИЯ

Х АВТОРСХОМУ СВИДЕТЕЛЬСТВУ (61) Дополнительное к авт. свид-ву ¹ 826418 (5l)M. Кл. (22) Заявлено 22.07.80 (21) 2966795/18-24 с присоединением заявки М.G 11 С 11/00

9кудэрстюапвй квмктет

СССР ао аман взв4ретеивк в вткрыткв (23) П риорнтет

Опубликовано 07.07.82. Бюллетень М 25

{53) УДК 681.827..6 (088.8) Дата опубликования описания 07.07.82

H. А. Прокашев, А. Н. Соповьев,,Б. А. Страбыкин, З. И. Шибанов и А. Ю, Пестов (72) Авторы изобретения

Кировский политехнический институт

I (1l ) Заявитель (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к вычиспитепьной технике и может быть использовано дпя построения устройств хранения цифровой информации.

По основному авт. св. ¹ 826418 из-. .вестно запоминающее устройство, содержашее матрицу yl.и блоков памяти, где

N — разрядность спова, адресные вхо- . ды которых соединены с выходами стар 1О ших разрядов регистра адреса, входы выбора бпоков памяти s -й, где g ñòðoки матрицы подкпючены к 4 -му выходу дешифратора, входы которого соединены с выходами мпадших разрядов регистра адреса, информационные входы бпоков па- мяти g -го, где <йстопбца матрицы подключены к j -му выходу входного регистра, а информационные выходы — к

) --ой группе входов основного блока эпе-йо ментов ИЛИ, выходы которого соединены со входами выходного регистра, вхо ные коммутаторы, коммутаторы выбора блоков памяти, выходной коммутатор и

2 дополнитепьный блок элементов ИЛИ, входы выбора блоков памяти -ой строки матрицы подкпючены к одноименным выходам 1 -го коммутатора выбора, первые входы которого подключены к . -му, а вторые — к одноименным выходам дешифратора, информационные входы блоков па мяти j-го стопбца матрицы соединены с одноименными выходами у-го входного коммутатора, первые входы которого подкпючены к. j -му а вторые - к одноименным выходам входного регистра, ин1 формационные выходы блоков памяти 4 -oN строки матрицы подключены к 1-ой группе входов допопнительного блока элементов ИЛИ, выходы основного блока эпементов ИЛИ соединены с первыми, а выходы дополнитепьного - со вторыми входами выходного коммутатора, выходы которого соединены со входами выходного регистра, управляюшие входы всех коммутаторов поаключаны к дополни тельному разряцу регистра aapeca

И з 9421

Недостатком устройства является невозможность ассоциативного считывания и записи информации по совпадению незамаскированных разрядов слов с заданным признаком. 5

Бель изобретения — расширение обпасти применения путем ассошативного считывания и записи информации по совпадению незамаскированных разрядов слов с заданным признаком, IQ

Поставленная цепь достигается тем, что в запоминаюшее устройство дополнительно введены регистры маски и признака, коммутаторы маски и признака, итоговый регистр сдвига, блок элемен- 15 тов ИСКЛЮЧАЮЩЕЕ ИЛИ через коммутатор 10 признака поступает сигнал выкпючены к выходам блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы — к входам итогового регистра сдвига, входы 20 первого элемента ИЛИ подключены к выходам старших разрядов адресного регистра, а выход первого элемента. ИЛИ является соответствуюшим управляющим выходом устройства, выходы итогового 25 регистра сдвига подключены к входам второго элемента ИЛИ, выход которого является соответствуюшим улравпяюшим выходом устройства, одни входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подкпюче- 50 ны к выходам выходного коммутатора, а другие входы — к выходу коммутатора призи Ка, одни входы. которого подключены к выходам младших разрядов адресного регистра, другие входы - к выходам 55 регистра признака, одни входы коммутатора маски подключены к выходам младших разрядов регистра адреса, а другие входы - к выходам регистра маски, выход коммутатора маски является соответ-д ствуюшим управпяюшим выходом устройства.

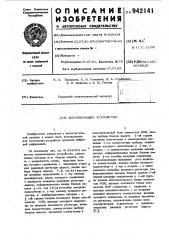

На чертеже приведена блок-схема за номи наюшего устройства.

Запоминаюшее устройство содержит регистр-счетчик 1 младших разрядов регистра адреса, регистр-счетчик 2 старших разрядов регистра адреса, дополнительный разряд регистра 3 адреса, дешифратор 4, первый элемент ИЛИ 5, коммутаторы 6 выбора, регистр 7 признака, ре-, гистр 8 маски, входной регистр 9, коммутатор 10 признака, коммутатор 1 1 маски, входные коммутаторы 12, матрицу блоков 13 памяти, блок 14 элементов

ИСКЛЮЧАЮ1ЦГЕ ИЛИ, основной блок 15 элементов ИЛИ, дополнительный блок 16 элементов 11ЛИ, блок 17 элементов И, 41 4 итоговый регистр 18 сдвига, выходной коммутатор 19, выходной регистр 20 и второй элемент ИЛИ 21.

Коммутатор 10 признака и коммутатор 11 маски — коммутаторы с 1 информационными входами и одним выходом, Блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 1, содержит Vl двухвходовых элементов ИС>

КЛ10ЧАЮЩЕЕ ИЛИ. Первый 5 и второй

21 элементы ИЛИ представляют собой

Vl-входовые элементы ИЛИ, а блок 11 элементов И содержит И двухвходовых элементов И.

Предлагаемое устройство может работать в девяти режимах: хранения инфорI мации, счйтывания И -разрядных чисел, записи р -разрядных чисел, считывания данных,представпяюших группу одноименных разрядов р чисел, записи данных, представляюших собой группу одноименных разрядов И чисел, ассоциативного считывания И-разрядных чисел по совпадению незамаскированных разрядов чисел с заданным признаком, ассоциативной записи 11-разрядных чисел, ассоциативного считывания данных, представляюших соI

:бой группу одноименных разрядов И чисел, по совпадению незамаскированных разрядов данных с заданным признаком, ассоциативной записи данных, представпяюших собой группу одноименных разрядов чисел.

В режиме хранения информации считывание и запись информации не производится, В режиме считывания и -разрядных чисел устройство работает спедуюшим образом.

В регистр адреса (регистр-счетчики

1 младших и старших разрядов) заносится адрес числа, одновременно допопнитепьный разряд регистра 3 адреса устанавливается в состояние "0". Регистр 7 признака, регистр 8 маски, коммутаторы

10 признака и 11 маски, блок 14 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 17 схем И, первый 5 и второй 21 элемент

ИЛИ и итоговый. регистр 18 сдвига при этом в работе устройства не участвуют.

На управляюшие входы коммутаторов

6 выбора, входных коммутаторов 12 и выходного коммутатора 19 поступает сигнал логического нуля. При этом через дешифратор 4 и коммутаторы 6 выбора на входы выбора блоков памяти

° -ой строки матрицы блоков 13 (номер строки задается мпадшими разрядами регистра-счетчика 1 адреса) поступает

В режиме ассоциативного считывания

П-разрядных чисеп по совпадению незамаскированных разрядов чисел с заданным признаком регистры-счетчики 1 младших и 2 старших разрядов адреса устанавливаются в нулевое состояние (нулевое состояние регистра-счетчика 2 старших разрядов адреса задает первый массив из И, р -разрядных чисеп), од новременно дополнительный разряд регистра 3 адреса устанавливается в состояние 1 . В регистр 7 признака заносится признак числа (И-разрядный двоичный код), в регистр 8 маски - маска (И-разрядный двоичный код, шгфра О, в котором маскирует одноименный разряд признака, искпючая его из рассмотрения), в итоговый регкскр 18 сдвига устанавливается в состояние 11...1.

5 9421 сигнал логической единицы, íà входы выбора остальных бпоков 13 памяти матри.цы поступает сигнап погического нупя.

Адресные сигналы старших разрядов регистра-начетчика 2 адреса поступают на адресные входы всех блоков 13 памяти.

Таким образом, оказывается выбранной одна ячейка блоков памяти -ой строки таблицы.

Производится считывание: сигналы 1О считываемого числа с информационных выходов блоков 13 памяти 1 -ой строки через основной блок 15 схем ИЛИ и выходной коммутатор 19 поступают на входы выходного регистра 20 и соответст- ts вуюшие вторые входы бпока 14 эпементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Число из выбранной ячейки памяти записывается в выходной регистр 20.

Запись и -разрядного числа происхо- 20 дит спедуюшим образом. Во входной регистр 9 заносится записываемое чиспо.

Также как в режиме записи и-разрядных чисел во входной регистр 9 заносится адрес числа и производится выбор ячей 35, ки памяти, в которую необходимо записать число.

Производится запись: сигналы записываемого числа с выходов входного регистра 9 через первые входы входных 30 коммутаторов 12 поступают на информационные входы всех бпоков памяти и устанавливают запоминаюшие эпементы выбранной ячейки в необходимые состояния.

В режиме считывания данных, представпяюших собой группу одноименных разрядов чисеп в регистр адреса (ре» .гистры-счетчики 1 младших и 2 старших разрядов) заносится адрес данных (числа), одновременно дополнительный разряд. регистра 3 адреса устанавпивается в состояние "1 . Регистр 7 признака, регистр

8 маски, коммутаторы 10 признака.и 1

11 маски, первый и второй эпементы ИЛИ 5 и 21, блок 17 схем И и итоговый регистр 18 сдвига при этом в работе уст ройства не участвуют, На управпяюшие входы коммутаторов

6 выбора, входных коммутаторов 12 и выходного коммутатора 19 поступает сигнал логической единицы. При этом через дешифратор 4 и коммутаторы 6 выбора на входы выбора блоков памяти ) -ro столбца матрицы блоков 13 (номер столб, ца задается мпадшими разрядами регистрасчетчика 1 адреса) поступает сигнап погической единицы, на входы выбора остальных блоков 13 памяти матрицы по41 6 ступает сигнал логического нуля. Адресные сигналы старших разрядов регистрасчетчика 2 адреса поступают на адресные входы всех блоков 13 памяти. Таким образом, оказывается выбранным набор запоминающих эпементов, соответствуюших группе j -х разрядов и чисеп в бпоках памяти j -го стопбца матрицы.

Производится считывание: сигналы считываемой. группы разрядов с информационных входов блоков памяти j --го столбца матрицы блоков 13 через допопнитепьный блок 16 эпементов ИЛИ и выходной коммутатор 19 поступает на входы выходного регистра 20 и соответствуюшие вторые входы блока 14 эпементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Группа одноименных разрядов и чисеп иэ выбранного набора запоминаюших эпементов записывается в вы-ходной регистр 20, В режиме запись данных, представляюших собой группу одноименных разря.дов и чисеп, во входной регистр 9 заносится записываемая группа разрядов данного числа. Так же, как и в пп. 4.1 и 4.2 как и в режиме считывания данных, представпяюших собой группу одноименных разрядов 8 чисеп, заносится адрес числа (данных) и производится выбор запоминаюших эпементов, в которые необходимо записать группу одноименных разрядов 8 чисел. Производится запись: сигналы записываемых разрядов с выходов входного регистра 9 через вторые входы входных коммутаторов 12 поступают на информационные входы всех бпоков 13 памяти. и устанавпивают запоминаюшие эпементы выбранного набора в необходимые состояния.

7 9421

Производится опрос-определение адресов чисел заданного массива, незамаскированные разряды которых совпадают с заданным признаком. Для этого на управпяюшие входы коммутатора 10 признака и коммутатора 11 маски поступают адресные сигналы младших разрядов регистра-счетчика 1 адреса. При этом на первые входы блока 14 элементов

ИСКЛЮЧАЮЩЕЕ ИЛИ через коммутатор >0

10 признака поступает сигнап выбранного разряда регистра 7 признака, а на выходе коммутатора 11 маски появляется сигнал выбранного разряда регистра маски. Ф5

Если на выходе коммутатора 11 маски устанавливается сигнал "1" (разряд регистра маски не равен "0 ), то также как и в режиме считывания данных, представляющих собой группы одноименных разрядов И чисел, производится выбор запоминаюших эпементов и считывание группы разрядов д чисел из блоков памяти j-ãî столбца матрицы. При этом на вторых входах блока 14 эпементов

ИСКЛЮЧАЮЩЕЕ ИЛИ появляются сигналы, соответствующие группе одноименных разрядов И чисел. В случае несов паденйя каких-либо разрядов считанной группы с разрядом признака, соответствующие им разряды итогового регистра

18 сдвига через блок 17 элементов И устанавливаются в нулевое состояние.

Если на выходе коммутатора 11 маски устанавливается сигнал "0", то выбор, считывание и изменение содержимого итогового регистра 18 сдвига не вьшопняются

Если иа выходе второго элемента

ИЛИ 21 единичный сигнап (хотя бы один . разряд итогового регистра 18.сдвига сохранил единичное состояние), то содер: жимое регистра-счетчика 1 младших разрядов адреса увеличивается на единицу, 45 в противном случае осушествпяется переход к определению номера следующего анализируемого массива ) И -разрядных чисе и.

41 8

Дпя осуществления этого режима дополнительный разряд регистра 3 адреса устанавливается в состояние "О». Если младший разряд итогового регистра 18 сдвига в единичном состоянии, то также как и в режиме считывания д-разрядных чисел производится выбор, считывание и занесение считанного чиспа (незамаскированные разряды которого совпадают с заданным признаком) в выходной регистр 20. В противном случае содержимое регистра-счетчика 1 младших разрядов адреса увеличивается на единицу и содержимое итогового регистра 18 сдвига сдвигается на один разряд в сторону младших разрядов. Еспи на выходе второго эпемента ИЛИ 21 единичный сигнал, то осуществляется анализ младшего разряда итогового регистра сдвига вышеука занным образом, в противном случае выполняется следующий пункт. Определение номера следующего анализируемого массива p — разрядных чисел. ,Бпя осушествнения этого режима регистр-счетчик м падших разрядов 1 адреса устанавпивается в нупевое состояние, содержимое регистра-счетчика 2 старших разрядов адреса увеличивается на единицу, а итоговый регистр 18 сдвига устанавливается в состояние 11...1. Еспи на выходе первого элемента ИЛИ 5 единичный сигнал (содержимое регистра-счетчика 2 старших разрядов адреса не равно нулю), то осуществляется переход к опросу-определению адресов чисел заданного массива, в противном случае процесс ассоциативного считывания И -разрядных чисел по совпадению незамаскированных разрядов чисел с заданным признаком заканчивается.

В режиме ассоциативной записи разрядных чисел начальные установки и опрос-определение адресов чисеп заданного массива в режиме ассоциативной записи 4-разрядных чисел осуществляется аналогично режиму ассоциативного считывания И-разрядных чисел по совпадению с незамаскированными разрядами чисел с заданным признаком.

Если на первом выходе дешифратора

4 нупевой сигнал. (содержимое регистрасчетчика мпадших разрядов1 адреса не равно нулю) то осуществляется переход к опросу-определению адресов чисеп данного массива, описанного выше, в противном случае выполняется считывание чисеп, незамаскированные разряды которых совпадают с заданным признаком.

5о

Осуществляется запись чисел по адресам, в которых хранятся числа, незамаскированные разряды которых совпадают с заданным признаком. Для этого дополнительный разряд регистра 3 адреса устанавливается в состояние О». Если младший разряд итогового регистра 18 сдвига в единичном состоянии, то так же, как и в режиме записи И-разрядного

9 942141 10 чиспа производится запись q-разрядно- числу, в случае несовпадения каких-пибо

I го числа в противном случае содержн- раэрядов считанного чиспа с разрядом

Э мое регистра-счетчика 1 мпадших разря- признака, соответствуюшие им разряды дов адреса увепичивается д в пичивается на единицу и итогового регистра 18 сдвига через бло содержимое итогового регистра 18 сдви- > 17 схем И устанавпиваются в нупевое га сдвигается на один разряд в сторону состояние. Еспи на выходе коммутатора

11 маски устанавпивается сигнап 0, Е в х де второго эпемента то выбор, считывание и изменение содерЕспи на выходе второго эпем

ИЛИ 21 единичный сигнап, то осушест- жимого итогового регистра 18 сдвига впяется анапнз мпадшего разряда итого- 10 не выпопняются. вого регистра 18 сдвига, в противном Если на выходе второ вто и схемы ИЛИ случае выполняется опредепение номера 21 единичный сигнал (хотя бы один разспедуюшего анапизируемого массива и, ряд итогового регистра 18 сдвига сохраняет единичное состояние), то содержи.Еспн на выходе первой схемы ИЛИ 5 lg мое Регистра-счетчика 2 старших разряединичный сигнап, то осушествпяется пе- дов адреса увеличивается на единицу иРеход к опросу-определению адресов чи- выполняется спедуюший пункт, иначе « сеп заданного массива, в противном спу- переход к опредепению номера спедуюшечае процесс ассоциативной записи И -раз- го анапизируемого массива данных, предрядных чисеп по совпадению нез а ад, нию незамаски - g0 ставпяюших собой группу одноименных. рованных разрядов чисеп . з и .с заданным при- разрядов И чисел, описываемое ниже. знаком заканчивается. Еспи на выходе схемы ИЛИ 5 единичный

В режиме ассоциативного считывания .сигнал (содержимое регистра- четчика 2 данных, представпяюших собой группу од- старших разрядов адреса не равно нупю, HoMMBHHblx разрядов и чисеп по совпа- 25 то осушествпяется переход к опросу-Опдени р незамаскированных разрядов дан- редепению адресов данных, в противном ных с заданным признаком регистры-счет- случае выполняется считывание данных,. чики 1 мпадших и 2 старших разрядов. представпяюших группу одноименных разадреса устанавпи пиваются в нулевое состо- рядов yl чисел, незамаскированные „азяние, допопни"" и разряд регистра Э 30 ряды которых соадают с дан м прим ю адРеса УстанавпиваетсЯ в состоЯние 0 . Знаком. Дпя осушествп ения этого допопР гие начальные установки анапогичны нитепьный разряд регистра 3 адреса усругие нач

1 Еспи ассоциативного считывания И-раэрежиму

Рядных чисеп ПроизвОдитсЯ ОпрОс-опре „й гист 18 зз сдвига в единичном состоянии, то так рбой rpyany дноименных разрядов И как и в режиме считывания дан, ре чисел, незамаскированные разряды кото- . ставпяюших собой группу одноименных вибо рых совпадают. с заданным признаком. Разрядов И чисел, производится р, На Управпяюшие входы коммутатора 10 считывание и запись считанных данных признака и коммутатора 11 маски посту- 40 в выходной регистр 20, в противном сауесные сигнапы младших разря- чае содержимое регистра-счетчи ка 2 пают адрес е дов регистра-счетчика 2 адреса. При старшйх разрядов адреса увепичивается этом на первые входы бпока 14 эпемен- на единицу и содержимое итогового реroB ИСКЛЮЧАЮШЕЕ ИЛИ через коммута- гистра 18 сдвига сдвигается íà один тоР 1 0 пРиэнака поступает сигнал вы- разряд в бРанного РазРЯда РегистРа 7 призиака, а пи на выходе второй схемы ИЛИ 21 едина выходе коммутатора 11 маски появпя- ничный сигнал, то осушествпяется переется сигнал я сигнал выбранного разряда Рег тр ход к считыванию данных, в противном случае выполняется опредепение. номера

50 спедуюшего анализируемого массива данЕсли на выходе коммутатоРа 11 мас- ных, представпяюших собой группу одно- . ки устан " ется сигнап 1 так име х р,эр,дов И же, как в режиме считывания 8- разрядных чисеп, производится выбор запоминаДпя осушествпения этого Регистр счетюших элементов и считывание чисиа, заэтом на вторых входах блока 14 эпементов ИСКЛЮЧАЮЩЕЕ ИЛИ появляются мое регистра-сче мое гистра-счетчика .1 мпадших Разрядов адреса увеличивается на 1, а итогосигналы, соответствуюшие считанному

11 942141

12 вый регистр 18 сдвига устанавпивается .в состояние 11...1.

Если. на первом выходе дешифратора

4 нупевой сигнап (содержимое регистрасчетчика 1 младших разрядов адресе не равно нулю), то осуществляется переход на опрос-определение адресов данных, в противном случае процесс ассоциативного считывания группы данных, представляющих собой группу одноименных разрядов чисел, по совпадению незамаскированных разрядов данных с заданным признаком заканчивается.

B режиме ассоциативной записи данных, представляющих собой группу одно- именных разрядов и. чисеп, начапьные установки и проведение опроса-определения адресов данных аналогично предыдущему режиму.

Запись данных, представляющих собой ро группу одноименных разрядов 11 чисеп, по адресам, в которых хранятся данные незамаскированные разряды которых совпадают с заданным признаком, производится спедуюшим образом.,д,ополнитепь- 25 ный разряд регистра 3 адреса устанавпивается в состояние 1", Еспи младший разряд итогового регистра 18 сдвига в единичном состоянии, то так же, как и в режиме записи подобных данных, произво- 30 дится запись данных, в противном случае происходит увеличение на единицу регистра-счетчика 2 старших разрядов адреса и сдвига на один разряд в сторону младших разрядов итогового регистра 18 сдвига.

Если на выходе второй схемы ИЛИ

21 единичный сигнап, то осушествпяется переход к анапизу младшего разряда итогового регистра 18 сдвига, в противном спучае выполняется опредепепие номера следующего анализируемого массива данных, представляющих собой группу одноименных разрядов И чисеп. Для этого производятся начапьные установки ана- <5 логичные как и при определении номера следующего анализируемого массива данных, представляющих собой группу одноименных разрядов р чисел.

Еспи на первом выходе дешифратора

4 нулевой сигнал (содержимое регистрасчетчика 1 мпащцих разрядов адреса, не равно нулю), то осушествпяется пункт опрос-определения адресов данных, в про- . тивном случае процесс ассоциативной за51 писи данных, представляющих собой группу одноименных разрядов И чисел заканчиваетсяя, Таким образом, в предпагаемом устройстве наряду с хранением информации, считыванием и записью И- разрядных чисел, считыванием и записью данных, представляющих собой одноименные разряды и чи« сел, возможно также выпопнение ассоциативного считывания и записи р разрядных чисел и ассоциативного считывания и записи данных, представпяюших собой группу одноименных разрядов и чисел, что расширяет обпасть применения запоминающего устройства.

Формупа изобретения

Запоминающее устройство по авт, св.

% 826418, о т и и ч а ю ш е е с я тем, что, с целью расширения области его применения за счет ассоциативного считывания и записи информации по совпадению незамаскированных разрядов слов с заданным признаком, оно содержит регистры маски и признака, коммутаторы маски и признака, итоговый регистр сдвига, бпок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы ИЛИ и блок элементов И, входы которого подкшочены к выходам блока эпементов ИСКЛЮЧАЮЩЕЕ ИЛИ, а выходы— к входам итогового регистра сдвига, входы первого эпемента ИЛИ подключены к выходам старших разрядов адресного регистра, а выход первого элемента ИЛИ является соответствующим управпяюшим выходом устройства, выходы итогового регистра сдвига подкпючены к входам второго элемента ИЛИ, выход которого является соответствующим управляющим выходом устройства, одни входы блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ подключены к выходам выходного коммутатора, а другие входы к выходу коммутатора признака, одни входы которого подключены к выходам мпадших разрядов адресного регистра, другие входы - к выходам регистра признака, одни входы коммутатора маски подключены к выходам мпадших разрядов регистра адреса, а другие входы -.к выходам регистра маски, выход коммутатора маски, явпяется соответствующим управляющим выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетепьство СССР

N 826418, кл. G 11 С 11/00, 1979

942141

Составитель С, Шустенко

Редактор С. Юско Техред А.Бабинед Корректор А. Ферена

Заказ 4851/45 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4