Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапистичесиии

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Опубликовано 07.07.82. Бюллетень № 25

Дата опубликования описания 09.07.82 (51)М. Кл.

G 11 С 29/ОО

ГавударставнныИ квинтет

CCCP но делам изобретений и открытий (53) УДК 681.З2, (088. 8) (72) Авторы изобретения

Г. П. Крупников, И. А. Марков, Б. В. Орлов, М;-Н-. Бероев, и В. B. Суворов I 4 ! ! :(7!) Заявитель (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

Изобретение относится к запоминающим устройствам.

Известны устройства для контроля блоков памяти, содержащие схему формирования растра, формирователи управляющих сигналов, схему соавненич 1).

Однако устройство не обеспечивает автоматизированного .выявления взаимного влияния ячеек памяти.

Наиболее близким техническим решением к предлагаемому является устройство для контроля блоков памяти, содержащее генератор кодов адреса, соединенный с блоком управления, формирователем координатной сетки и телевизионным приемником, блок управления соединен с компаратором, выход которого через смеситель соединен с телевизионным приемником, причем второй вход смесителя подключен к выходу генератора координатной сетки 12).

Недостаток устройства состоит в низкой эффективности контроля, обусловленной недостаточной надежностью выявления одиночных сбоев.

Цель изобретения — повышение достоверности контроля за счет надежного выявления одиночных сбоев, 5

Поставленная пель достигается тем, что в устройство для контроля блоков памяти, содержащее генератор кодов адреса, первый выход которого подключен к входу блока управления и входу формирователя сигналов координатной сетки и является первым вь ходом устройства, а второй выход соединен с одним из входов телевизионного приемника, компаратор, первый вход которого под-. ключен к первому выходу блока управления, а второй вход является входом устройства, второй выход блока управления является вторым выходом устройства, вь?ю ход формирователя сигналов координатной сетки соединен с одним из входов смесителя сигналов, выход которого подключен к другому входу телевизионного приемника, введен блок. памяти, управляющий вход

А421 которого соединен с третьим выходом блока управления, адресный вход — с ,:первым выходом генератора кодов адреса, информационный вход — с выходом компаратора, а выход соединен с другим входом смесителя сигналов.

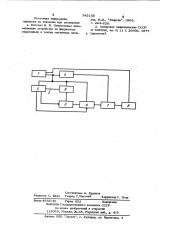

На чертеже изображена функциональная схема усгройства для контроля блоков памяти.

Устройство содержит генератор 1 ко- 10 дов адреса, блок 2 управления, имеющий выход 3, формирователь 4 сигналов координатной сетки, компаратор 5, блок 6 памяти, смеситель 7 сигналов и телевизионный приемник 8. 15

Ко входу и выходам устройства подключается контролируемый блок 9 памяти.

Устройство работает следующим образом.

Для простоты объяснения работу устройства рассмотрим на примере контроля блока памяти емкостью 256 бит, организованчых в 64 х4 бита, т.е. 64 четырехразрядных слова. Генератор 1 последовательно формирует коды, соответствующие адресам ячеек контролируемого блока 9. При этом формирователь

4 вырабатывает сигнал, который через смеситель 7 поступает на вход приемника 8, работающего в построчном режиме, и формирует на экране прямоугольную сетку размером 16х 16, каждый прямоугольник которой соответствует одной ячейке блока 9 (или 4-разрядному слову). Размер ячейки может меняться по желанию оператора. На первых к стро- ках (где к — размер ячейки по вертикали) адрес У остается неизменным, а адрес

Х циклически меняется от 1 до 16, причем после каждого цикла счета адресов

Х (т.е. перебора всех 16) генератор 1

40 вырабатывает строчный синхроимпульс; который подается на вход приемника 8.

После сканирования к строк адрес У увеличивается на единицу и т.д. После сканирования всех строк, соответствующих координатной сетке, генератор 1 вырабатывает кадровый синхроимпульс, который подается на вход приемника 8, и процесс повторяется. Г1ри этом в зависимости от выбранного режима может производиться не только последовательное считывание информации из блока 9 и отображение ее на экране (при котором, например, логическому "0" соответствует минимальная яркость, а 1 максимальная), но и кснтроль блока 9.

В режиме контроля блок 2 при адресации к очеоедной ячейке производит запись

88 4 необходимой информации. Считанная из ячейки информация в компараторе 5 сравнивается с информацией, поданной из блока 2. Результат сравнения записывается в блок 6 памяти, причем адрес блока 6 памяти соответствует адресу контролируемой ячейки блока 9, причем при совпадении (т.е. ячейка функционипует нормально) записывается, например, логическая "1", а при несовпадении — логический "О". Возможна также запись результатов сравнения кодом, например, сбой по "0" — код "00, сбой по единине — 10, ячейка функционирует нормально — "1 1 ".

Записанная в блоке 6 памяти информация поступает через смеситель 7 сигналов на телевизионный приемник 8, на экране которого подсвечивается прямоугольник координатной сетки, соответствующий ячейке, в которой наблюдается сбой.

Введение дополнительно блока 6 памяти позволяет надежно выявить одиночные сбои, что существенно повышает достоверность контроля.

Фор мула изобретения

Устройство для контроля блоков памяти, содержащее генератор кодов адреса, первый выход которого подключен к входу блока управления и входу формирователя сигналов координатной сетки и является первым выходом .устройства, а второй выход соединен с одним из входов телевизионного приемника, компаратор, первый вход которого подключен к первому выходу блока управления, а второй вход является входом устройства, второй выход блока управления является вторым выходом устройства, выход формирователя сигналов координйтной сетки соединен с одним из входов смесителя сигналов, выход которого подключен к другому входу телевизионного приемника, о т л и ч а ю щ е ес я тем, что, с целью повышения достоверности контроля, оно содержит блок памяти, управляющий вход которого соединен с третьим выходом блока управления, адресный вход — с первым выходом генератора кодов адреса, информационный вход — с выходом компаратора, а выход соединен с другим входом смесителя сигналов.

Источники информации, принятые во внимание при экспертизе

1. Китович В. В. Оперативные запоминающие устройства на ферритовых сердечниках и тонких магнитных плен942188 d ках. М 41., Энергия, 1965, с 223-228

2. Авторское свидетельство СССР

Ж 698056, кл. G 11 С 29/00, 1977

5 (пРототип)., Составитель И. удаков

Редактор С. Юско Техред Т.Маточк Корректор Г. Огар

Заказ 4853/46 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР па делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4