Запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

Союз Советских

Социалистических

Республик

Оп ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

I»>942163 (6l ) Дополнительное к авт. свил-ву l4 762038 (5! )М. Кл.

G 11 С 29/00 (22) Заявлено 24. 11.80 (2}) 3226568/18-24 с присоединением заявки,% (23) Приоритет

9жударст«е«и6 нам«твт

СССР ао да«вм. «звбрвтвн«й н аткрыт«й

Опубликовано 07.07,82. Бюллетень № 25

Дата опубликования описания 09.07.82 (53) УДК 681.327 (088.8) В. B. Слюсарь, В. С. Сташко и Н. М. Токарев (72) Авторы изобретения

-(7!) Заявитель

I (54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО С АВТОНОМНЫМ

КОНТ РОЛЕ М

Изобретение относится к запоминающим устройствам.

По основному авт. св. М 762038 известно устройство, содержащее накопители, регистр адреса, первый и второй дещифраторы, блок коррекции информации, 5 первую и вторую группы элементов ИЛИ, коммутатор, регистр информации, блок управления, регистр состояний накопителей, регистр ошибок и элементы И, причем входы накопителей подключены соответственно к первому выходу блока коррекции информации и входам регистра адреса и коммутатора, входы коммутатора соединены соответственно с выходом первого дешифратора и первым выходом блока коррекции информации, одни из входов которого подключены к выходам элементов ИЛИ первой группы, входы которых соединены с выходами накопителей; >выходы регистра информации подключены к другим входам блока коррекции информации, управляющие входы регистра адреса, накопителей, коммута2 тора, блоке коррекции информации и регистра информации соединены с одними из выходов блока управления, одни из входов которого подключены к управляющим выходам коммутатора и блока коррекции информации, первый и второй выходы которого подключены к информационным входам регистра состояний накопителей и регистра ошибок, выходы которого соединены с первыми входами элементов И, третий выход блока коррекции информации и выходы элементов И подключены к входам элементов NlH второй группы, выходы которых соединены с входами регистра информации, вход второго дешифратора подключен к адресному входу устройства, а выход — к другому входу блока управления, управляющие входы регистра состояний накопителей и регистра ошибок и вторые входы элементов И соединены с другими выходами блока управления (1).

Однако в известном устройстве не фиксируется адрес, при обращении по котопомехоустойчивым кодом (например, кодом Хэмминга), декодирование считываемого информационного слова из накопителей

6, исправление сбоев в информационном слове с последующей выдачей в регистр

22 информации и формирование сигналов ошибок B информационном слове, а также сбоев узлов самого блока 13 коррекции информации. Регистр 14 ошибок осуществляет хранение сигналов ошибок и сбоев.

Регистр 25 адреса осуществляет хранение адреса, по которому производится обращение к ЗУ.

Устройство работает следующим образом.

Адрес ячейки, к которой необходимо обратиться, записывается в регистр 2 адреса и регистр 25 адреса. Единичный сигнал, возникающий на соответствующем выходе дешифратора 5, поступает в коммутатор 11. Последний задает один из двух режимов работы в зависимости от отсутствия или наличия отказов в ячейках накопителя 6. При отсутствии отказов в ячейках накопителя 6 коммутатор

11 по сигналу от дешифратора 5 подключает соответствующий накопитель 6, разрешая запись информации в этот накопитель (режим записи) или чтение информации (режим чтения), а также разрешая прохождение управляющих сигналов от блока 19 управления. Информация в накопитель 6 записывается с регистра 21 информации через блок 13.

При считывании содержимое накопителя 6 через элементы ИЛИ 10 поступает в блок 13, определяющий наличие сбоев или отказов в ячейке подключенного накопителя 6, Через элементы ИЛИ 16 информационное слово поступает в регистр

22 информации.

При обнаружении сбоя в считываемом слове информации блок 13 формирует сигнал ошибки, поступающий в блок 19 управления, который информирует процессор (не показан) о наличии ошибки. Кроме того, блок 19 осуществпяет запись ошибки в регистр 14 и запрещает изменение кода в регистре 25 при обращении к ЗУ как данного процессора, так и других устройств. Таким образом, в регистре 25 фиксируется адрес ячейки ЗУ, при обращении к которой в режиме чтения блок 13 зафиксировал ошибку в считываемом слове инфор мации.

При наличии сигнала ошибки, поступившего от ЗУ, процессор последовательно формирует на адресных шинах 1 коды

Э 942163 рому произошел сбой или отказ функциональных частей запоминающего устройства (ЗУ), в частности накопителей, что снижает надежность как самого устройства, так и в целом вычислительной 5 системы, в которую данное устройство входит.

Цель изобретения — повышение надежности устройства .

Поставленная цель достигается тем, l0 что в запоминающее устройство с автономным контролем введены дополнительные регистр адреса и элементы И, причем одни из входов дополнительного регистра адреса соединены с входами вто- 15 рого дешифратора, а выходы — c одними из входов дополнительных элементов И, выходы которых подключены к одним из входов элементов ИЛИ второй группы, другие входы дополнительного регистра щ адреса и элементов И являются управ-. ляющими входами устройства.

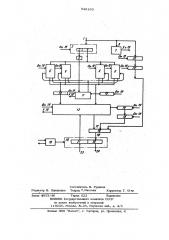

На чертеже представлена структурная схема запоминающего устройства с автономным контролем. 25

Устройство содержит адресные шины

1, соединенные с входом регистра 2 адреса, в состав которого входит регистр 3 номера накопителя и регистр 4 номера ячейки, первый дешифратор 5, накопители 6, второй дешифратор 7, имеющий вход 8 и выход 9, первую группу элементов ИЛИ 10, коммутатор 11, регистр 12 состояний накопителей, блок

13 коррекции информации, регистр 14 ошибок, элементы И 15, вторую группу элементов ИЛИ 16 с входами 17 и выходами 18, блок19 управления, регистр

20 информации, в состав которого входят регистры информации 21 и 22 соответственно для входящего и исходящего направлений, имеющий вход 23 и выход

24, дополнительный регистр 25 адреса, дополнительные элементы И 26. !

Дешифратор 7 при поступлении на его 45 входы кодов псевдоадреса (или адреса несуществующих ячеек накопителя 6) фор- мирует на своих выходах 9 управляющие сигналы, Коммутатор ll осуществляет подключение управляющих сигналов, поступающих из блока 19 управления к соответствующим накопителям 6. Регистр

12 состояний накопителей предназначен для выдачи визуальной информации о накопителе, в котором произошел отказ или 55 сбой. Блок 13 коррекции осуществляет кодирование слова информации, поступающего с выхода регистра 21 информации, 942 псевдоадреса, по которым формируются сигналы управления на выходе дешифратора 7. По данным сигналам, поступающим в блок 19 управления, управляющие сигналы обращения к накопителям 6 не формируются. По первому коду псевдоадреса блок 19 управления подключает элементы И 15 и через элементы ИЛИ 16 сигнал из регистра 14 и при наличии в нем информации о сбое или отказе нако- 10 пителей блок 19 управления подключает выход регистра 25 через элементы И 26 и элементы ИЛИ 16 к входам регистра

22 информации.

Анализируя адрес ячейки ЗУ, по кото- 15 рой произошел сбой или отказ, процессор определяет отказавший накопитель. Информацию об отказавшем накопителе выдает процессор, устанавливая соответствующий триггер в регистре 12 состояний 20 накопителей в единичное состояние. Запись. в регистре 12 осуществляется по управляющему сигналу управления, формирующемуся на выходе дешифратора 7.

Введение регистра 25 позволяет 25 упростить аппаратно-программные средства процессора, так как не требуется дополнительного введения в его состав программно-доступного регистра адреса, необходимого для хранения кода 30 адреса ячейки ЗУ, к которой проводилось обращение, что особенно важно при построении мультипроцессорных вычислительных систем. Кроме того, введение данного регистра позволяет также процессору 33 провести диагностику адресно-информаi63 б ционного тракта системы, а также части оборудования ЗУ. Действительно при обращении к ячейке ЗУ в этом регистре фиксируется данный адрес. Считывая и сравнивая его с адресом, хранимым на внутренних программно-доступных регистрах процессора, можно определить отказ оборудования, обеспечивающего работоспособность этого тракта с точностью до элемента или группы элементов, относящихся к одному разряду адреса.

Формула изобретения

Запоминающее устройство с автономным контролем по авт. св. М 762038, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности устройства, устройство содержит дополнительные регистр адреса и элементы И, причем одни из входов дополнительного регистра адреса соединены с входами второго дешифратора, а выходы — с одними из входов дополнительных элементов И, выходы которых подключены к одним из входов элементов ИЛИ второй группы, другие входы дополнительного регистра адреса и элементов И являются управляющими входами устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 762038, кл. 9 11 С 29/00, 1978 (прототип).

942163

Составитель В. Рудаков

Техред Т.Маточка .Корректор Г. Огар

Репектор В. Пилипенко филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

Заказ 4853/46 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5