Одноразрядный двоичный сумматор

Иллюстрации

Показать всеРеферат

ОП MCAHHE

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскими

Соцнапнстнческнк

Республик

G 06 F 7/50

Гееударстаапвй камнтет

СССР во делам нэебретекий н открытнй (53) УДК 681. .325.5 (088. 8) Опубликовано 15.07.82. Бюллетень №26

Дата опубликования описания 17.07.82 (72) Авторы изобретения

Ю. А. Кулагин, С. И. Назаров (7I ) Заявитель

I (54) ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР

Изобретение относится к вычислитель ной технике и может быть использовано в арифметических устройствах универсальных и специализированных вычислительных машин.

Известен одноразрядный двоичный

5 сумматор на двадцати четырех МДПтранзисторах, содержащий узел выработки переноса и узел выработки суммы $1J.

Недостатком данного сумматора является сложность конструкции.

Известен также одноразрядный двоичный сумматор, содержащий сумматоры по модулю два, элементы НЕ, узел переноса и узел выработки суммы, причем все ужы сумматора построены на МДПтранзисторах (21 .

Недостатком известного сумматора является большой объем оборудования.

Цель изобретения - сокращение объе- 2о ма оборудования.

Поставленная цель достигается тем, чго в одноразрядном двоичном сумматоре, содержащем два сумматора по модулю два и узел переноса, причем пер вый и второй входы первого сумматора по модулю два подключены к первому и второму входам pa соответственно, первый и второй входы второго сумматора по модулю два подключены к третьему входу сумматора и к выходу первого сумматора по модутпо два соответственно, выход второго сумматора по модулю два соединен с выходом суммы сумматора, узел переноса содер йат четыре МДП-транжстора, затворы первого и второго из которых соединены с выходом первого сумматора по модулю два, затворы третьего и четвертого

МДП |ранжсторов узла переноса соеди-нены между собой, истоки первого и третьего МДП-транжсторов узла переноса соединены со вторым входом сумматора, истоки второго и четвертого

МДПгранжсторов узла переноса соединены с третьим входом сумматора, стоки всех МДПгранжсторов узла переноса объединены н подктпочены к выходу

1О

35!

3 (14 и 1" л1оса суюматора, каждый сумматор цо модулю два "..îäåðæèò четыре МДПтранзистора и два элемента НЕ, входы которъ х соединены с первым и вторым входами сумматора по модулю два, вход первого элемента НЕ соединен с ист<>ками первого и второго МДПгранзисторов сумматора по модулю два, выход первого элемента НЕ соединен с истоками третьего и четвертого МДП- гранжсторов сумматора по модулю два, вход второго элемента HE соединен с затворами первого и третьего, выход второго элемента HE - с затворами второго и четвертого МДП-транзисторов сумматора по модулю два, стоки всех МДП-транзисторов которого объединены и подключены к выходу сумматора по модулю два, выход второго элемента HE второго сумматора по модулю два соединен с затвором третьего МДП-транзистора узла переноса.

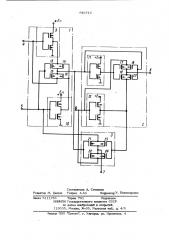

На чертеже представлена принципиальная схема одноразрядного двоичного сумматора.

Сумматор содержит сумматоры 1 и

2 по модулю два и узел 3 переноса.

Входы 4 и 5 сумматора 1 по модулю два явпяются первым и вторым входами сумматора, вход 6 сумматора 2 по мсдулю два является третьим входом сумматора, выход 7 узла 3 является выходом переноса сумматора, а выход 8 сумматора 2 по.модулю два является выходом суммы сумматора. Сумматоры по модулю два состоят из двух элементов НЕ 9 и 10 (11 и 12) и четырех

МДП-транзисторов 13, 14, 15 и, 16 (17, 18, 19 и 20). Узел переноса состоит из четырех МДП-транжсторов

21, 22, 23 и 24.

Сумматор работает следующим образом.

Если на входе 5 щжсутствует сигнал уровня логического нуля, то открыты транзисторы 15 и 16 и Hà вход элемента 11 и затворы транжсторов 18, 20, 21 и 22 поступает сигнал со входа 4.

В зависимости от уровня сигнала на этом входе на выход 7 поступает сигнал со входов 5 нли 6, на выход 8 — сиг нал со входа 6 ипи его инверсное значение. Если на шине 5 присутствует сигнал уровня логической единицы, то открыты транзисторы 13 и 14 и инверсное значение со входа 4- управляет работой всей схемы.

Данный одноразрядный двоичный сумматор имеет существенно меньцшй объем

3712 4 оборудования, выражакипийся в уменьшении числа компонент и связей между ними.

Формула изобретения

Одноразрядный двоичный сумматор, содержащий два сумматора по модулю два и узел переноса, причем первый и второй входы первого сумматора по модулю два подключены к первому и второму входам сумматора соответственно, первый и второй входы второго сумматора по модулю два подключены к третьему входу сумматора и к выходу первого сумматора по модулю два соответственно, выход второго сумматора по модулю два соединен с выходом суммы сумматора, узел переноса содержит четыре МДП-транжстора, затворы первого и второго из которых соединены с выходом первого сумматора по модулю два, затворы третьего и четвертого МДП-транзисторов узла переноса соединены между собой, истоки первого и третьего МДП-транжсторов узла переноса соединены со вторым входом сумматора, истоки второго и четвертого МДП-транзисторов узла переноса соединены с третьим входом сумматора, стоки всех МДП-транжсторов.узла переноса объединены и подшючены к выходу переноса сумматора, отличающийся тем, что, с цепью сокращения объема оборудования, каждый сумматор по модулю два содержит четыре МДП-транзистора и два элемента НЕ, входы которых соединены с первым и вторым входами сумматора по модулю два, вход первого элемента HE соединен с истоками первого и второго

МДП-транжсторов сумматора по модулю два, выход первого элемента НЕ соединен с истоками третьего и четвертого

МДП-транзисторов сумматора по модулю два, вход второго элемента НЕ соединен с затворами первого и третьего, а выход второго элемента HE - с затворами второго и четвертого МДПтранзисторов сумматора по модулю два, стоки всех МДП-транзисторов которого объединены и подключены к выходу сумматора по модулю два, выход втррого элемента НЕ второго сумматора по модулю два соединен с затвором третьего

МПП гранзистора узла переноса.

Источники информа1ц1и, принятые во внимание при экспертизе

1,RCA С05(М05 1nteg1ated С1гса ь, 550-20ЪC,)975, Databook 5eг1еа, с. 55, фиг. 5.10.

2. Патент СЩА l4 3767906, кл. 235-175, 1973 (прототип).

943712

Составитель А. Степанов

Редактор М.,Пылын Техред А.Ач Корректор У. Пономаренко

Заказ 5111/56 Тираж 731 Подписное

ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская на6., д. 4/5

Филиал ППП Патент, r. Ужгород, ул. Проектная, 4