Устройство для деления

Иллюстрации

Показать всеРеферат

) (72) Авторы нзобретення

Н. И. Глотов, Г. B. Гайдученко и Е. П. Пан

Таганрогский радиотехнический институт им. В. Д. Калмыкова (7!) Заявнтель (54) УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ

Изобретение относится к вычнслительяой технике и .может быть использовано в цифровых вычислительных машинах для деления двоичных чистая.

Известно устройство для деления чисел в двоичном коде без восстановления остатка, содержащее сумматор, логические схемы И, ИЛИ, схему сочетания жаков." Это устройство обладает сравнитеп но небольшим быстродействием, так как для определения П -цифр частного выполняется } -одинаковых циклов. Каждый цикл состоит нз двух тактов (1$.

Известно также устройство, содержаmee сумматор, счетчик, регистры, элементы задержки и элементы И f2j

Это устройство обладает небольшим быстродействием, так как для получения каждого разряда частного требуется

qua такт, а следовательно, для получения fl разрядов частного - и тактов.

Известно устройство для деления, ссь держащее матричный сумматор, элемен ты И, ИЛИ, триггеры, причем первые входы сумматоров первого ряда матрицы соединены с шинами разрядов делимого в прямом коде, а ко вторым входам сумматоров всех рядов матрицы лодкпючены шины разрядов делителя в дополни5 тельном коде, первые входы и выходы сумматоров предыдушего ряда матрицы через соответствующие две группы эле. ментов И и группу элементов ИЛИ под,о юп зчены ко входам сумматоров всех последующих рядов матрицы со сдвигом на один разряд влево, причем управлякицие входы каждой из групп элементов И подсоединены к шинам разрядов частного

15 и ко входу ттиптера, соответствующего данному ряду сумматоров 13 (.

Недостатком этого устройства является некоторая избыточность аппаратуры, связанная, в частности, с наличием в схеме устройства тр п геров Шмидта, чго также нескапько снижает быстродействие устройства.

Наиболее близким к изобретению является устройство для деления матричного

3713 4

3 94 типа, содержашее в каждой ячейке одноразрядный сумматор, он вход которого подключен через элемент ИЛИ к выходам двух элементов И, выход одноразрядного сумматора { -ой строки и { -го столбца матрицы подключен к одному из входов одноразрядного сумматора ({ +

+1)-й строки н (j -1)-го столбца матрицы, кроме того, в каждой ячейке содержится два сумматора по модулю два, первые входы которых в каждой строке матрицы подключены.к первой шине управления, вторые входы первого сумма- тора по модулю два в каждой строке матрипы подключены ко второй шине управления я к одному из входов первого элемента И, вторые входы вторых сумматоров по модуюпо два в каждом столбце матрицы подключены к одному из входов второго элемента И и к входу устройства, выходы сумматоров rro модуmo два подключены к друтнм входам соответствуюпих элементов И (4 .

Недостатком этого устройства является некоторая избыточность оборудования, связанная с его дублированием в каждой ячейке.

Цель изобретении - сокращение количества оборудования.

Указанная цель достигается тем, что в уст)эойство для деления, содержащее (П -1) двоичных сумматоров (П вЂ” число разрядов операндов), элементы И, ИЛИ и НЕРАВНОЗНАЧНОСТИ, прячем первый вход { -го разряда (s 1, .... П ) первого сумматора подключен к шине соответствующего разряда делимого устройства, первый вход каждого разряда

cyama pa (j - г, ..., rl-1) подключен к выходу предыдущего разряда (д -1)-го сумматора, второй вход каждого разряда k -го сумматора (k =

= 1, ..., П -1) подключен к выходу соответствующего элемента ИЛИ k -ой группы, входы которого подключены к выходам соответствующих элементов И

k -й и 2k -й групп, первый вход каждого элемента И k -й группы соединен с шиной соответствующего разряда делителя устройства, выход первого элемента

НЕРАВНОЗНАЧНОСТИ соединен с вторым входом старшего элейента И первой группы, выход старшего разряда k -го сумматора соединен с первым входом (k + l)-го элемента НЕРАВНОЗНАЧНОСТИ, выход которого соединен с первым входом старшего элемента И (4+1)группы, введены элементы РАВНСЗНАЧ15

55 й

НОСТИ, причем входы первых элементов

НЕРАВНОЗНАЧНОСТИ и РАВНОЗНАЧНОСТИ подключены к шинам знаковых разрядов делимого и делителя устройства, выход первого элемента НЕРАВНОЗНАЧНОСТИ соединен с вторыми входами младших элементов И первой группы, первые входы элементов И 2 k -й груи пы соединены с шннами соответствуюших разрядов дополнительного кода делителя, вторые входы элементов И. 2 < -й группы соединены с выходом k -го эле» мента РАВНОЗНАЧНОСТИ, входы 0 -го элемента РАВНОЗНАЧНОСТИ (0 = 2, ..., П ) соеднйены с выходом старшего разряда (-1)-го сумматора и шиной знакового разряда делителя устройств, второй вход 0 -го элемента НЕРАВНОЗНАЧНОСТИ соединен с шиной знакового разряда делителя устройства.

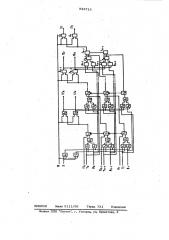

На чертеже представлена схема устройства.

Устройство содержит П -1 сумматоров 1{t 1 »»»»» 1л { П элементов ИЛИ 2{, 2, ... 2{1 {, 2(П -1) групп элементов И 3{, 3>, ...

Зй { » 4{ 1 4 » °,, 4»1 { элементь1

НЕРАВНСВНАЧНОСТИ 5{, 5, ..., 5 1 {, 5л, элементы РАВНОЗНАЧНОСТИ

6{» 6(y " 6 п{» 6{ {» шины 74, 7{1 <, 711 делителя (прямого кода); шины 8, ..., 8{1, 81 дополнительного кода делителя; шины 9 и 10 знаковых разрядов делимого и делителя; щины 11{, ..., 1111{, 11п делимого шины значений 12{, 12, ..., 12 1, 13{, 13, ..., 13 q прямого и инверсного частного.

Устройство работает следующим образом»

Операция деления начинается с анализа знака делимого и делителя, которые подаются по шинам 9 и 10 на элементы НЕРАВНОЗНАЧНОСТИ 5, и РАВНОЗНАЧНОСТИ 6. Если знаки одинаковые, то срабатывает элемент РАВНОЗНАЧНОСТИ 6 { a групйа элементов

И 4{, и на вход сумматора 1{ подается делитель в дополнительном коде, который поступает по шинам 8. Если же знаки делимого и делителя не совпадают, то срабатывает элемент НЕРАВНСВНАЧНОСТИ 5.{ и срабатывает группа элементов И 3{, и на вход сумматора 1{ подается делитель в прямом коде по шинам 7, На другие входы всех разрядов сумматоров 1 {» 1Я1 ° »»» 1 11-{ по» дается:код делимого по шинам 11. Знак

5 943713 остатка с выхода старшего разряда

» сумматора 10 подается на элементы Н

HEPABHO3HAЧНОСТИ 42 и РАВНО- д

ЗНАЧНОСТИ 5», на другие входы котоpbIx пОДается GHBK Делителя с шины 10 ° 5

Происходит сравнение знаков остатка и делителя, если знаки совпадают в зна- к ковый разряд частного по шинам 12 и

13 записывается единица, еспи знаки не совпадают - нуль, одновременно сра- 10 ц батвпзает схема РАВНОЗНАЧНОСТИ 5» ипи НЕРАВНОЗНАЧНОСТИ 42 соответ- 3 ственно, которые разрешают подачу на м вторые входы сумматоров 10 g второго 3 столбца матрицы прямого ипи дополни- 15 тельного кода депитепя. Последующие

BB

I6IttIpbI час ГнОГО пслуча1отся BHBIIQPR IHûì 3 образом.

Преимушество предпоженного устрой- - пе ства по сравнению с известным заипо- го пы чается в некотором уменьшении оборудования за счет исключения его дубпиро- вт вания в Жаждой ячейке, I

Формула изобретения

Устройство дпя деления, содержащее (t1 -1) двоичных сумматоров { П вЂ” число разрядов операндов), элементы И, ИЛИ и НЕРАВНОЗНАЧНОСТИ, причем первый

ВхОд «го разряда (4 = 1, ... °, fl ) первого сумматора подключен к шине соответствующего разряда делимого устройства, первый вход каждого рЬзряда

j -го сумматора () = 2, ..., l1 -1) подипочен к выходу предыдущего разряда (-1)-го "умматора, второй вход каждого разряда k. -го сумматора (k =

= 1» "., 0 -1) подключен к выходу соответствукнцего элемента ИЛИ k -ой группы» входы которого подключены к выходам соответствующих эпементов И

)С -й и 2 k,-й групп, первый вход каждого элемента И k-й группы соединен с шиной соответствующего разряда делителя устройства, выход первого элемента НЕРАВ

ОЗНАЧНОСТИ соединен с вторым вхоом старшего элемента И первой груп11Ы, 1ход старшего разряда k -го сумматора соединен с первым входом (k+1)-го емента НЕРАВНОЗНАЧНОСТИ, выход оторого соединен с первым входом аршего элемента И (к+1)-й группы> т л и ч а ю щ е е с я тем, что, с елью сокрашения количества оборудования, оно содержит элементы РАВНОНАЧНОСТИ, причем входы первых элеентов HEPABHCGHA×ÍÎCTÈ И РАВНО-.

НАЧНОСТИ подключены к шинам знаковых разрядов делимого и делителя устройст, выход первого элемента НЕРАВНОНАЧНОСТИ соединен с вторыми входамн младших элементов И первой группы, рвые входы элементов И 2 k -й групсоединены с шинами соответствующих разрядов дополнительного кода делителя, орые Входы элементов И 2 k -й групсоединены с выходом k -го элемента

РАВНОЗНАЧНОСТИ, входы 3 -го элемен25 та РАВНОЗНАЧНОСТИ (0 2, ...,.й ) соединены с выходом старшего разряда

{ 6 -1)-го сумматора и шиной знакового разряда делителя устройства. второй вход

3 -го элемента НЕРАВНОЗНАЧНОСТИ зо соединен с.шиной знакового разряда деJ1ETeII$I устройства

Исто чники инфсрмапии, принятые во внимание при экспертизе

1. Папернов А. A. Логические основы .UBT. М., "Советское радио, 1972, с. 225-236, 2. Самофалов К. Г. и др. Электронные ЦВМ. Киев, "ВН1ца школа"," 1976, с. 325-330.

3. Авторское свидетельство СССР

% 360663, и1. Q 06 Р 7/52, 1970.

4. Авторское свидетельство СССР

М 543937, кл. Ñò 06 Р 7/38, 1975 (прототип) . !

943713 ъ

У Ъ

Ф ф ф е е» фд»

° и - t аЬ

ВНИИПИ Закаэ 5111/56 Тираж 731 Поцписное

Филиал ППП "Патент", r. Ужгороц, ул Проектная, 4