Устройство для анализа последовательных кодов

Иллюстрации

Показать всеРеферат

Союз Советскик

Социапнстическии

Республик

О П И С А Н И Е, 943731

ИЗОБРЕТЕН Ия

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (6l ) Дополнительное к авт. свид-ву (22) Заявлено 06. 06. 80 (21) 2936289/18-24 (5 I ) M Кл.

G 06 F 9/46 с присоединением заявки РЙ

Гоеударстаеииый комитет

СССР (23) Приоритет по делам иэабретеиий и открьпий

Опубликовано 15.07.82. Бюллетень №26

Дата опубликования описания 18. 07 . 82 (53) УДК .325(088.8) (72) Автор изобретения

В. В. Аристов

Институт электродинамики АН Украинской ССР (71) Заявитель (54) УСТРОЙСТВО ДЛЯ АНАЛИЗА ПОСЛЕДОВАТЕЛЬНЫХ

КОДОВ

Изобретение относится к автоматике и вычислительной технике и может быть использовано в специализированных вычислительных и управляющих устройствах и системах различного на5 значения.

Известно устройство для анализа кодов прерываний, содержащее элементы И, ИЛИ,триггерные регистры (11.

Недостатком такого устройства являются сложность оборудования для организации анализа последовательных кодов.

Наиболее близким по технической сущности к изобретению является устройство, содержащее элементы И, ИЛИ, счетчик, триггеры, распределитель импульсов Г21.

Устройство имеет следующие недостатки: сложность оборудования и го ограниченная область применения из-за невозможности анализа последовательных кодов с произвольным представлением входных двоичных данных.

Цель изобретения — расширение области применения устройства.

Поставленная цель достигается тем, что в устройство для анализа последовательных кодов, содержащее счетчик и первый триггер, введены блок памяти, счетный триггер, второй, третий и четвертый триггеры, три элемента И, элемент НЕ и элемент задержки, причем кодовый вход устройства соединен с первым входом адреса записи блока памяти, с единичным входом первого триггера, с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И, тактовый вход устройства соединен с входом счетчика, с тактовым входом блока памяти и со вторыми входами первого и второго элемента И, информационный выход счетчика соединен с информационным входом блока памяти, выход переполнения счетчика соединен с входом счетного триггера, с единичным входом второго триггера и че943731

5 ! о

20

55 рез элемент задержки с единичными входами третьего и четвертого триггеров, нулевые входы которых соединены соответственно с выходами первого и второго элементов И, выходы третьего и четвертого триггеров соединены соответственно с первым, вторым входами третьего элемента И, выход которого соединен с нулевым входом второго триггера, выход которого является сигнальным выходом устройства, единичный выход счетного триггера соединен со вторым входом адреса записи блока памяти, нулевой выход счетного триггера соединен с первым входом адреса считывания блока памяти, выход первого триггера соединен со вторым входом адреса считывания блока памяти, выход которого является информационным выходом устройства.

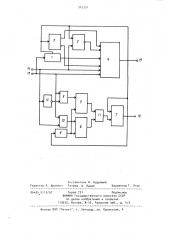

На чертеже приведена структурная схема устройства.

Устройство содержит счетчик 1, триггер 2, счетный триггер 3, блок 4 памяти, триггеры 5, 6, 7, элемент 8 задержки, элементы И 9, 10, 11, элемент НЕ 12, тактовый вход 13 устройства, информационный вход 14 устройства, информационный выход 15 устройства, сигнальный выход 16 устройс гва.

Последовательность работы предлагаемого устройства состоит в задании анализируемого последовательного ко. да в порядке, начиная с младших разрядов, на информационном входе устройства и тактирующей серии на тактовом входе. На выходе устройства после числа тактов, равного емкости счетчика 1 (и числу разрядов (каналов) анализируемого числа), появляется код номера старшего разряда, имеющего единичное состояние, если последний разряд анализируемого кода (знаковый) был нулевым, или код старщего разряда, имеющего нулевое состояние, если последний анализируемый разряд был единичным.

Работу устройства рассмотрим на примере выделения старшего значащего разряда двоичного числа, представленного в дополнительном коде младшими разрядами вперед для двух вариантов знаков: а) А=0.000101100010 — положитель— — и иое число; б) А=1.110100010011 - отрицательное число.

Адреса разрядов, которые необходимо определить в обоих вариантах, подчеркнуты, причем поскольку знаковый разряд поступает последним, то до его поступления отсутствует признак, какие уровни — единичные или нулевые - необходимо анализировать.

Блок памяти 4 выполнен на регистровом ЗУ типа 155РП и содержит первый и второй входы адреса записи, первый и второй входы адреса считывания стробирующий вход записи, стробирующий вход считывания (на чертеже не показан), информационный вход и выход, причем возможно раздельное управление адресами записи и считывания одновременно, Анализируемое число А, поступая на вход 14, управляет первым входом адреса записи блока памяти 4. На второй вход адреса записи подается сигнал с триггера 3, состояние которого меняется лишь при поступлении сигнала с последовательного выхода счетчика 1 после анализа последнего (знакового) разряда. Следовательно, при анализе кода состояние триггера 3 не меняется и соответствует, например, единичному. В этом случае на второй вход адреса записи блока памяти 4 поступает уровень

"0", поэтому нулевые разряды анализируемого числа А формируют адрес записи 00, а единичные — 01. На ин35 формационный вход блока памяти 4 с параллельного выхода счетчика 1 поступает код номера разряда, поэтому по стробирующему входу записи блока памяти 4 в ячейку с адресом 00 запи4Р сываются последовательно адреса разрядов, имеющие уровни "0", а в ячейку 01 - уровни "1".

С приходом последнего разряда, знакового, счетчик 1 формирует импульс, по заднему фронту изменяющий состояние триггера 3 и разрешая занесение знакового разряда в триггер 2. Поскольку первый вход адреса считывания блока 4 соединен с инверсным выходом триггера 2, для положительного числа устанавливается адрес считывания 01, а для отрицательного - 00, и на выходе блока 4 имеется код номера подчеркнутого разряда соответственно для варианта а и 6. Этот код сохраняется на выходе блока .4 в течение всего цикла анализа очередного числа А, для которого, так как триг943731 6 гер 3 изменил состояние, адрес разрядов со значениями "0" записывается в ячейку с адресом 10, а со значениями "1" — в ячейку с адресом 11, а считывание с одной из этих ячеек 5 осуществляется при анализе очередного числа А.

Так как при анализе последовательных кодов числа А с одинаковыми значениями разрядов fO в) А = 0.00000000 или г) А = l. 11111111 будет считан адрес предыдущего чис ла, то в конце анализа необходима 15 предварительная установка ячеек памяти записи в начальное состояние, что может потребовать еще несколько дополнительных тактов работы. В ряде случаев (в особенности, для спе- 20 циальных целей — последовательном устройстве для вычисления элементарных функций и т.п.) указанные дополнительные такты работы могут оказаться нежелательными. В этом случае 25 устройство дополняется схемой дешифрации равнозначных состояний последовательных входных данных. Эта схема выполнена на триггерах 5, 6, 7, элементе задержки 8, элементах И 9, щ

10, 11 и элементе НЕ 12.

Разряды числа А поступают на элемент И 10 непосредственно, а на элемент И 9 - через элемент НЕ 12. При поступлении сигнала по тактовому вхо- З ду 13 устройства выполняется логика . и на одном из элементов 9 или 10, устанавливая первый 5 или второй 6 триггер в единичное состояние. В конце предыдущего цикла импульсом р с последовательного выхода счетчика

f через элемент задержки 8 оба эти триггера устанавливаются в нулевое состояние, поэтому после анализа числа А для вариантов а и б оба

4$ триггера в конце цикла обязательно оказываются в единичном состоянии, которое через третий элемент И 11 в конце цикла анализа переписывается в триггер 7. Для вариантов в или r лишь один из триггеров 5 или 6 окажется в единичном состоянии,что приводит к установке в конце цикла анализа триггера 7 в нулевое состояние.

Выход этого триггера является сигнальным выходом устройства и служит для определения равнозначных состояний.

Применение изобретения позволяет расширить область применения устройства за счет возможности анализа последовательных кодов с произвольным представлением двоичных данных.

Формула изобретения

Устройство для анализа последовательных кодов, содержащее счетчик и первый триггер, о т л и ч а ю— щ е е с я тем, что, с целью расширения области применения, устройство содержит блок памяти, счетный триггер, второй, третий и четвертый триггеры, три элемента И, элемент НЕ и элемент задержки, причем кодовый вход устройства соединен с первым входом адреса записи блока памяти, с единичным входом первого триггера, с первым входом первого элемента И и через элемент НЕ с первым входом второго элемента И, тактовый вход устройства соединен с входом счетчика, с тактовым входом блока памяти и со вторыми входами первого и второго элементов И, информационный выход счетчика соединен с информационным входом блока памяти, выход пере-. полнения счетчика соединен с входом счетного триггера,с единичным входом второго триггера и через элемент задержки с единичными входами третьего и четвертого триггеров, нулевые входы которых соединены соответственно с выходами первого и второго элементов И, выходы третьего и четвертого триггеров соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен с нулевым входом второго триггера, выход которого является сигнальным выходом устройства, единичный выход счетного триггера соединен со вторым входом адреса записи блока памяти, нулевой выход счетного триггера соединен с первым входом адреса считывания блока памяти, выход первого триггера соединен со вторым входом адреса считывания блока памяти, выход которого является информационным выходом устройства.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

0 703812, кл. G 06 F 9/46, 1977 °

2. Авторское свидетельство СССР

У 697995, кл. G 06 .F 9/46, 1978 (прототип).

Тираж 731 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 5113/57

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4

Составитель И. Кудряшев

Редактор А, Долинич Техред 3. Палий Корректор Г. Огар