Устройство для синхронизации

Иллюстрации

Показать всеРеферат

О П И С А Н И Е < 943737

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскии

Социалистическии

Республик (6l) Дополнительное к авт. свид-ву (22) Заявлено 03.05.78(2l) 2610485/18 24 с присоединением заявки № (23) Приоритет (51)IVL. Кл.

С 06 Г 15/16

3Ьвударатвеииый комитет

СССР

Ilo lellaN изобретений и открытий

Опубликовано 15.07.82. Бюллетень ¹26 (53) УДК 681.Д27.. 6(088. 8) Дата опубликования описания 18.07.82 (72) Авторы изобретения

Ю. С. Хенкин и Я. М. Лихтер:

1 с

Киевский ордена Трудового Красного Зттаъжнп завод вычислительных и управляющих машин (71) Заявитель (54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАБИИ

Изобретение относится к вычислитель=ной технике и может быть использовано

У при проектировании многопроцессорных систем.

Известно устройство синхронизации

5 вычислительных систем, обеспечивающее синхронную работу процессоров с постоянным вз,аимным расположением синхросигналов 1

Однако это устройство отличается не- 10 достаточной гибкостью, так как в многопроцессорных системах желательно иметь возможность по программе менять взаим ное расположение синхросигналов.

Наиболее близким к данному изобретению является устройство, отличающееся наличием одного генератора тактирующих импульсов и блока программного задания сдвига синхроимпульсов различных процессоров, входящих в систему (21 . 20

Однако это устройство имеет большое время вхождения в синхронизм (несколько циклов), увеличивающееся с ростом числа тактов, на которые разбит рабочий

2 пикл. Кроме того, во время вхождения в синхронизм образуются переменные йнтервалы между соседними тактами в процессорах, что может привести к сбою при обмене информацией между ними в данный момент, так как таких переменных интервалов много

Белью изобретения является повышение быстродействия и надежности устройства, Бень достигается тем, что ввод в синхронизм производится путем останова устройства после формирования соответствующих тактовых импульсов, определяемых блоком управления, в каждом процессоре с последующим одновременным запуском, в устройство для синхронизации, содержащее блок управления, выходы которого подключены соответственно к первым вхо-. дам блоков местного управления, вторые входы которых подключены-к выходам соответствующих распределителей, входы которых соединены с выходами елементов И, одни входы которых подключены к выходу генератора тактовых импульсов, 94373 введены триггеры останова и триггер цикла, формирователи импульсов запуска и останова, причем другие входы элементов И подключены к выходам триггеров останова, первые входы которых подключены к первым выходам блоков местного управления, а вторые — к единичным входам триггера цикла и выходу формирователя импульсов запуска, вход которого подключен. к третьим входам блоков е местного управления, к выходу и первым входам формирователей останова, вторые входы триггеров останова соединены с выходами триггера цикла, тактовые входы триггеров останова подключены ко второму входу второго блока местного управления, а информационные — ко вторым выходам первого и третьего блоков месч ного управления.

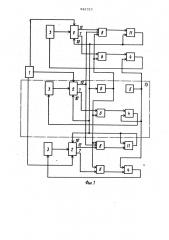

На фиг. 1 приведена блок-схема устройства; на фиг. 2 - блок-схема блока местного управления.

Работа устройства поясняется на примере системы, состоящей из 3-х процессоров с восьмитактной синхронизацией соответственно.

Устройство содержит блок управлении

1, выходы которого подключены к первым входам блоков местного управления 2, расположенных в каждом процессоре. Вторые входы блоков 2 соединены с выхода» ми распределителей 3, входы которых соединены с выходами схем 4 (элементы И}. Первые входы схем 4 объединены и подключены к генератору тактовых им-, пульсов 5, а другие входы подключены

35 к выходам триггеров останова 6. Первые входы триггеров останова 6 подключены к выходам 7 блоков местного управления 2, а вторые объединены между собой

40 и установочными входами триггеров цикла

8 и подключены к выходу формирователя запуска 9, вход которого подключен к объединенным между собой третьим входам 10 блоков 2, выходам и первым входам формирователей останова 11. Другие

45 входы формирователей останова 11 подключены к выходам триггеров 8, тактовые входы которых объединены и подключены к выходу 12 блока местного управления 2 центрального процессора 13, а информационные входы подключены к выходам 12 блоков 2 своих процессоров, На блок местного управления 2 (см. фиг. 2) поступаЬт тактовые импульсы

14 «21 от распределителя и управляющие сигналы 22 - 29. Блок местного управления состоит из восьми элементов 30 И - по числу тактовых импуль7 ф сов в одном рабочем цикле, элемента 31

ИЛИ и элемента 32 И, Рассмотрим работу системы без сдвига синхроимпульсов в разных процессорах.

Для этого необходимо подать управляющий сигнал на одноименные входы блоков местного управления 2 всех процессоров, например, на входы 29. В этом случае на выход 12 поступает каждый восьмой тактовый импульс.

При синхронной работе передний .фронт импульсов на тактовых входах триггеров

8 (Q-триггера с динамическим управлением, т. е. занесением по фронту синхросигнала) устанавливается внутри импульсов, поступаюших на информационные вхог ды, и на выходах триггеров 8 будет постоянный уровень (например, уровень логической единицы). Триггеры 6 установлены в состояние, при котором импульсы генератора 5 через схемы 4 И поступают на распределители 3.

При рассинхронизации любого процессора с центральным передний фронт сигнала на тактовом входе одного из триггеров 8 не совпадает с импульсом на информационном входе, триггер 8 переключается и запускает формирователь останова 11, который формирует импульс длительностью равной времени одного рабочего цикла.

При совпадении этого импульса с восьмым тактовым импульсом на входах элемента

32 И в каждом процессоре на выходе 7 формируется импульс, переключаюший саответствуюший триггер 6, запрешая прохождение импульсов генератора 5 на распределитель 3. Одновременно сигнал с выхода формирователя 11 блокирует по входам формирователи 11 от повторного запуска. Таким образом все распределители останавливаются после выдачи восьмого тактового импульса. Далее формирователь 11 задним фронтом запускает формирователь 9, устанавливаюший триггеры 6 и 8 в исходное состояние. Тем самым разрешается прохождение импульсов генератора 5 на распределители 3, которые начинают формирование импульсов с первого такта.

При задании сдвига работа устройства происходит аналогично. Например, если на блоки местного управления 2 разных процессоров подать управляюшие сигналы соответственно на 22, 23 и 24 входы, то при рассинхронизации первый процессор остановится после выдачи первого тактового импульса, второй - после второго, третий - .после третьего, и при запуске первый процессор начинает формиро9437 вание тактовых импульсов со второго, второй (центральный, в нашем примере) -с третьего, третий - с четвертого, что и обуславливает синхронную работу процесcopos с заданным сдВиГОм синхроимпульг 5 сов. При этом будет совпадение переднего фронта второго тактового импульса центрального процессора соответственно с первым и третьим тактовыми импульсами первого и третьего процессоров на входах 1Р триггеров 8.

Таким образом система входит в синхронизм в течение одного цикла, а неравномерный интервал между остановом распределителей и их пуском только один. 1S

Это обеспечивает минимальное время вхождения в синхронизм независимо от длительности никла числа тактов в цикле и количества процессоров, входящих в систему. При частых изменениях сдвигов щ синхроимпульсов между процессорами по программе устройство обеспечивает более высокое быстродействие. При этом за счет того, что число интервалов переменной длительности сведено к минимуму, повЫ- 2S шается надежность функционирования системы. формула изобретений Зр

Устройство для синхронизации, содержащее блок управления, выходы которого подключены соответственно к первым

37 6 входам блоков местного управления, вторые входы которых подключены к выходам соответствующих распределителей, входы которых соединены с выходами элементов И, одни входы которых подключены к генератору тактовых импульсов, о тличающееся тем, что, с целью повышения быстродействия и надежности устройства, оно содержит триггеры останова и цикла, формирователи импульсов запуска и останова, причем другие входы элементов И подключены к выходам триггеров останова, первые входы которых подключены к первым выходам блоков местного управления, а вторые - к установочным входам триггеров цикла и выходу формирователя импульсов запуска, вход которого подключен к третьим входам блоков местного управления, к выходам и первым входам формирователей останова, вторые входы которых соединены с выходами триггеров цикла, тактовые входы которых подключены к второму выходу одного из блоков местного управления, а информационные - к вторым выходам других соответствующих блоков местного управления.

Источники информации,, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

¹ 308430, кл. Cj 06 Р 15/16, 1972.

2. Авторское свидетельство СССР

¹ 458829, кл. G 06 Г 15/16 1975. . (прототип).

943737

Составитель Ю. Хенкин

Техред 3.Палий орр тoр r- Ог р редакто А. Долинич

Филиал ППП "Патент, г. Уигород, -ул. Проектная, 4

Заказ 5 ЖЗ/57 Тираж 73 1 . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж35, Рауновская наб., д. 4/5