Устройство для регенерации динамической памяти

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик (1)943845 (61) Дополнительное к авт. сеид-ву (22) Заявлено 21.11. 80 (21) 3оо8372/18-24 с присоединением заявки No — (23) Приоритет

Опубликовано 150782.Бюллетень Мо 26

Р М g> з

6 11 С 11/34.

Государственный комитет

СССР во делам изобретений и открытий (ЯЗ) УДК 681.327, ° 66 (088. 8) Дата опубликования описания 15.07.82 (72) Авторы изобретения

Х.Лайх (ГДР) и Ф.В.Левчановский (Объединенный институт ядерных иссйедеваний (71) Заявитель (54) УСТРОЙСТВО ДЛЯ РЕГЕНЕРАЦИИ

ДИНАМИЧЕСКОЙ ПАМЯТИ

Изобретение относится к автомати- ке и вычислительной технике и может быть использовано. в микропроцессорных вычислительных системах.

Известны устррйства регенерации динамической памяти, в которых используется асинхронный режим обработки запросов обращений к памяти со сто роны процессора. Эти устройства получили широкое распространение благодаря своей универсальности и независимости от типа вычислительной системы, в которой динамическая память применяется. Основными элементами таких устройств являются:двоичный 15 счетчик, адресный коммутатор и схемаарбитр. В схему — арбитр поступают сигналы запросов обращения к памяти и сигналы состояния памяти. На основании этих сигналов арбитр определяет последовательность обработки запросов и производит запуск циклов записи, чтения или регенерации памяти (1 ).

Недостатком устройства являются большие потери времени. 25

Наиболее близким техническим решением к изобретению является устройство, в котором в качестве арбитра применяется встроенный в микропроцессор (МП) типа К580ИК80 алго- . ритм обработки запросов обращений модуля прямого доступа к памяти (ПДП).

Устройство содержит триггер запроса и триггер коммутации, элемент ИЛИ-НЕ, первый и втОрой входы которого .подключены к первой и второй шинам запроса соответственно, а выход элемента ИЛИ-НЕ соединен с информационным входом сдвигового регистра, коммутатор, первый вход которого подключен к выходу счетчика адреса, и дешифратор, выходы:которого соединены с первыми входами элементов ИЛИ, причем входы элементов ИЛИ подключены к шинам выборки адреса памяти (2).

Недостатком асинхронного устройства регенерации динамической памяти является простой процессора во . время регенерации. Коэффициент потерь зависит от типа динамической памяти, длительности цикла обращения к памяти, периода регенерации и определяется выражением;

У = "†- -100а, И Тр где Ис — чисЛо строк (столбцов) матрицы памятит

1 - длительность цикла обращения, Т вЂ” период регенерации..

943845

Для динамической памяти типа

К565РУЗА эти потери составляют. 3,2% процессорного времени. В устройстве эти потери времени. увеличиваются еще примерно вдвое, поскольку необходима синхронизация микропроцессора в режиме Захват шин . Невозможно также использование в микропроцессорной вычислительной системе модуля ПДН типа К580ИК57, так как шины Захват и Подтвержде- 1О ние захвата МП заняты для целей регенерации памяти.

Цель изобретения — повышение быстродействия устройства регенерации динамической памяти путем выполнения регенерации памяти в те.моменты времени, когда МП находится в такте, не требующем обращения к ней. Таким тактом для МП типа

К580ИК80 является четвертый такт цикла выборки команды, в котором МП занят ее дешифрацией.

Поставленная цель достигается тем, что в устройство введены триггеры выборки команды останове, прямого до. ступа к памяти и триггер выборки столбца памяти, элемент И-ИЛИ-НЕ, первый и второй элементы И-НЕ, при этом входы синхронизации триггеров выборки команды и останова подключены к шине строба, первый вход элемента И-ИЛИ-НЕ соединен с второй шиной запроса, второй и третий входы — c прямыми выходами триггеров выборки команды и останова соответственно, четвертый вход элемента

И-ИЛИ-НЕ и входы сброса триггеров выборки команды и прямого доступа к памяти подключены к прямому выходу триггера запроса, а пятый и шестой 40 входы элемента И-ИЛИ-НЕ соединены соответственно с шиной установки и прямым выходом триггера прямого доступа к памяти, выход элемента ИИЛИ-НЕ подключен к информационному входу триггера коммутации, вход синхронизации которого соединен с первым входом первого элемента

И-НЕ и первой шиной синхронизации, а второй вход первого элемента И-НЕ с третьим входом элемента ИЛИ-НЕ, прямым выходом триггера коммутации, информационным входом триггера выборки столбца памяти, входом сброса триггера запроса и первым управляющим входом коммутатора, причем инверсный выход триггера прямого доступа к памяти подключен к третьему входу первого элемента И-НЕ, входы синхронизации триггера запроса и счетчика адреса соединены с шиной запроса регенерации, выход коммутатора подключен к адресной шине устройства, причем первый выход сдвигового регистра соединен с первым входом второго элемента И-HE и уп- 65 равляющим входом дешифратора, второй вход второго элемента И-НЕ подключен к инверсному выходу триггера коммутации, а выход второго элемента И-НЕ соединен с вторыми входами элементов

ИЛИ, при этом второй выход сдвигового регистра соединен со вторым управляющим входом коммутатора и входом сброса триггера выборки столбца па- мяти, вход синхронизации которого подключен к третьему выходу сдвигового регистра, причем информационные входы триггеров запроса и прямого доступа к памяти подключены к шине источника питания, а вход синхронизации сдвигового регистра — к второй шине синхронизации.

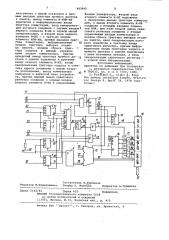

На чертеже приведена функциональная схема предлагаемого устройства.

Устройство содержит триггеры выборки команды 1, останова 2, запроса регенерации 3, прямого доступа и памяти 4, коммутации 8 и выборки столбца памяти 13, элемент И-ИЛИ-НЕ

5, счетчик адреса б, элемент ИЛИ-НЕ

7, первый и второй элементы И-НЕ 9 и 11, сдвиговый регистр 10, коммутатор адресных шин 12, дешифратор 14, элемент ИЛИ 15, динамическую память

16, первую и вторую шины синхронизации 24 и 17, первую и вторую ши ны запроса 18 и 19, шины данных микропроцессора 20 и 21, шины сброса, установки, и запроса регенерации 22, 23 и 25, шину Строб адреса модуля ПДП 2б, шины выходов триггеров выборки команды, останова, запроса регенерации и модуля ПДП 2731, шины выхода элементов И-ИЛИ-НЕ, ИЛИ-НЕ 32 и 33, прямую и инверсную шины выхода триггера коммутации 34 и 35, ацресные шины МП AO-A6 и А7-А13

36 и 37, выходные шины адресного счетчика 38, выходные шины сдвигового регистра 39-41, шины выхода первого и второго. элементов И-НЕ 42 и 43, старшие разряды адреса МП вЂ” 44 и 45, инверсный выход триггера выборки столбца 4б, адресные шины памяти

47, шины выборки строки матрицы памяти 48-51 и шины данных 52.

Рассмотрим работу устройства в то время, когда нет запроса регенерации памяти. В этом случае триггеры

1-4 сброшены и синхроимпульс первой шины синхронизации 24 (ф2-ТТЛ) установит триггер коммутации 8 в неактивное единичное состояние. Сигналы обращения к памяти Запись 18 и Чтение 19 проходят через элемент ИЛИ-НЕ 7 и устанавливают высокий

v уровень напряжения на послецовательном входе 33 сдвигового регистра 10.

Высокочастотные синхроимпульсы второй шины синхронизации 17 (длительность такта .- 54 нс) сдвигают этот уровень, который, появившись на ши943845 не 39, разрешает работу дешифратора блоков памяти 14, выходы которого в свою очередь, пройдя через элементы ИЛИ 15, стробируют и записывают младшие разряды адреса МП AO-Aá (36) на внутренний регистр строки матрицы выбранного блока (сигнал .RAS). Сигнал нулевого уровня напряжения на шине 48 выбирают блок памяти

0-16К, на шине 49-16К-32К, на шине

50 — 32K-48К и на шине 51- 48К-64К. 10

В .следующем такте сдвигового. регист-. ра 10 единичный уровень появляется на шине 40 и переключает коммутатор адресных шин 12 таким образом, что адресные разряды МП А7-А13 (37) проходят на адресную шину. памяти 47.

Положительный фронт на шине 41 установит триггер 13 в единичное состояние и на его выходе 46 появится сигнал, записывающий адресные разряды А7-А13 на внутренний регистр столбца матрицы памяти (сигнал CAS). После снятия

МП сигналов запроса 18 и 19 сдвиговой регистр 10, триггер 13 и коммутатор 12 возвращаются в первоначальное состояние.

Если на шине 25 появился сигнал запроса регенерации динамической памяти 16, то устанавливается в единичное состояние триггер запроса 3, 30 разрешив таким образом работу триггерам выборки команды 1 и прямого доступа к памяти 4, и увеличивается на единицу содержимое адресного счетчика б. В очередном цикле выборкиз5 команды в первом такте цикла на шине 20 (шина данных Д5 ) МП устанавливает единичный уровень, который ,сигналом строб 22 (Статус-строб,) переносится на шину 27. Во втором и третьем такте этого цикла МП выдает сигнал запроса 19 Чтение, который и .отрабатывается описанным способом. В четвертом такте цикла выборки команды сигнал "Чтение" сбрасывается и МП переходит к дешифрацйи выбранной команды. После сброса сигнала на шине 19 срабатывает элемент, И-ИЛИ-НЕ 5 и нулевой уровень напряжения на шине 32 переписывается положительным фронтом синхроимпульса ши- 50 ны 24 на шину 34, запуская таким образом снова цикл работы памяти и сбрасывая триггер запроса регенерации 3.

Так как на шине 35 теперь высокий уровень напряжения, то при появле- 55 нии высокого уровня и на выходе второго триггера сдвиговаго регистра 39 срабатывает второй элемент И-HE 11, и сигнал выборки строки матрицы памяти, пройдя через элементы ИЛИ 15, 60 появляется одновременно на входах всех блоков памяти (шины 48-51). В этот момент времени к адресным шинам

47 коммутатор 12 подключает выходы

38 адресного счетчика 6. Сигнал вы- 65 борки столбцов матрицы памяти 46 не включается, так как на информационном входе триггера 13 установлен нулевой уровень напряжения. Вследствие того, что триггеры запроса 3 и выборки команды 1 при срабатывании триггера коммутации 8 сбрасываются,, очередной положительный фройт импульса синхросерии на шине 24 возвращает в начальное состояние триггер коммутации 8, и цикл регенерации памяти на этом заканчивается.

Помимо цикла выборки команды регенерация памяти разрешена также прй подаче сигнала начальной .установки

23 (Системный сброс ) и переходе МП в режим Останов, который ,фиксируется триггером 2. Если в микропроцессорной системе работает мо-. дуль ПДП, то NII может находиться в режиме Захват . В таком случае цикл регенерации запускается сигналом Строб адреса (шина 26), выдаваемого модулем ПДП. Этот сигнал устанавливает в единичное состояние триггер 4, который задерживает на один такт (время регенерации памяти) импульсы первой синхросерии, поступающих к модулю ПДП по шине 42.

Формула изобретения

Устройства для регенерации динамической памяти, содержащее триггер запроса и триггер коммутации, элемент ИЛИ-НЕ, первый и второй входы которого подключены к первой и второй шинам запроса соответственно, а выход элемента ИЛИ-НЕ соединен с информационным входом сдвигового регистра, коммутатор, первый вход которого подключен к выходу счетчика адреса, и дешифратор выходы которого соединены с первыми входами элементов ИЛИ, причем выходы элементов ИЛИ подключены к шинам выборки адреса, о т л и ч а ю щ е ес я тем, что, с целью повышения быстродействия устройства, в него введены триггеры выборки команды, останова, прямого доступа к памяти и триггер выборки столбца памяти, элемент И-ИЛИ-НЕ, первый и второй элементы И-НЕ, при этом входы синхронизации триггеров выборки команды и останова подключены к шине строба, первый вход элемента И-ИЛИНЕ соединен с второй шиной запроса, второй и третий входы .- с прямыми выходами триггеров выборки команды и останова соответственна, четвертый вход элемента И-ИЛИ-НЕ и входы сброса триггеров выборки команды и прямого доступа к памяти подключены к прямому выходу триггера запроса, а пятый и шестой входы элемента И-ИЛИ-НЕ соединены соот7

943845

Составитель В.Тепенков

Редактор М.Недолуженко Техред Т. Маточка Корректор A.Ãðèéåíêo

Заказ 5142/62 Тираж 622 Подписное

HHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, r Ужгород, ул. Проектная, 4 ветственно с шиной установки и пря-. мым выходом триггера прямого доступа. к памяти, выход элемента И-ИЛИ-НЕ подключен к информационному входу триггера коммутации, вход синхрониза- ции которого соединен с первым входом5 первого элемента И-НЕ и первой. шиной синхронизации, а второй вход первого элемента И-НЕ - c третьим входом элемента ИЛИ-НЕ, прямым выходом хриггера коммутации, информационным 10 входом триггера выборки столбца памяти, входом .сброса триггера запроса и первым управляющим входом коммутатора, причем инверсный выход триггера прямого доступа к памяти подключен к третьему входу первого элемента И-НЕ, входы синхронизации триггера запроса и счетчика адреса соединены с шиной запро са регенерации„ выход коммутатора подключен к адресной шине устройства, причем первый выход сдвигового регистра соединен с,первым входом второго элемента И-НЕ и управляющим входом дешифратора, второй вход второго элемента И-НЕ подключен к инверсному .выходу триггера коммутации, а выход второго элемента И-НЕ соединен с вторыми входами элемен.тов ИЛИ, при этом второй выход сдвигового регистра соединен с вторым управляющим входом коммутатора и входом сброса триггера выборки столбца памяти, вход синхронизации которого подключен к третьему входу сдвигового регистра, причем информационные входы триггеров запроса и прямого доступа к памяти подключены к шине источника питания, а вход синхронизации сдвигового регистра к второй шине синхронизации.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

Р 78g035, кл. G 11 С 7/00, 1980.

Г1ейапй G., Dishi К. Кеер

the memory interface Simpt. e. Electronic Design 9, April 26, 1978 (прототип).