Постоянное запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз . Советских

Социалистических

Республнк в)943848 (И } М. Кл. (63) Дополнительное к авт. свид-ву(22) Заявлено 25. 10. 76 (21) 2414307/18-24 сприсоединениемзаявки № (23) Приоритет

Опубликовано 150782 Бюллетень ¹ 26

G 11 С 17/00

Государственный комитет

СССР но делам изобретений и открытий

{53}УДК 681.327 ° .66(088.8) Дата опубликования описания 15.07.-82 (72) Автор изобретения

ХК.Козлов (71) Заявитель (54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике,и может быть использовано прн изготовлении постоянных запоминающих устройств (ПЗУ) .

Известно ПЗУ, содержащее матрицы, состоящие из нелинейных элементов, связывающих адресные и разрядные шины, а также дешифраторы и шифраторы. Построение ПЗУ по такой схеме уменьшает количество элементов связи в матрицах, но выходы матриц соединены с шифраторами и де« шифраторами, которые сами будут иметь большое количество элементов 1).

Наиболее близким техническим решением к предлагаемому является ПЗУ„ содержащее входной дешифратор, выходьт которого через элементы связи накопителя соединены с разрядными шинами накопителя, выходной дешифратор, выходы которого соединены с первыми входами соответствующих элементов И-НЕ, выходы которых подключены к входам элемента ИЛИ-НЕ, выход элемента ИЛИ-НЕ является выходом устройства. Недостатком устройства является большое количество элементов (2).

Целью изобретения является повышение информационной емкости устройст ва.

Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее входной дешифратор, выходы которого соединены с входами накопителя, выходной дешифратор,выходы которого соединены с первыми входами соответствующих элементов И, выходы которых подключены к входам элемента ИЛИ, выход элемента ИЛИ является выходом устройства, введены инверторы и переключатели, причем вход каждого инвертора и первый вход каждого переключателя соединен с соответствующим выходом накопителя, вы» ход каждого инвертора соединен со вторым входом соответствующего пере-.

20 ключателя, выход которого соединен со-вторым входом соответствующего . элемента И.

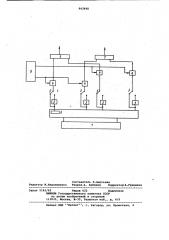

На чертеже представлена структурная схема ПЗУ.

25 Устройство состоит из блоков 1, количество которых равно числу ад ресов одной из групп (данном случае и), и многовходового элемента 2 ИЛИ.

Блок 1 содержит инвертор 3, элемент

30 4 И переключателя 5. Накопитель сос943848 тоит, например, из элемента 6 ИЛИ-НЕ (количество входов которой равно

m/2). Кроме того, устройство содержит дешифраторы 7 и 8.

Адреса разбиваются на две группы и и m, причем одна из групп адресов является общей (в данном случае

m) для другой группы. Наличие информации на выходе ПЗУ определяется не присоединением адресных шин одной из групп к входам элемента б

ИЛИ-НЕ. Для уменыттения количества

I элементов связи ПЗУ элемент б ИЛИ-НЕ имеет количество входов .равное 1/2 адресов группы m. При необходимости присоединения большего, чем m/2, 15 адресов к входам элемента ИЛИ-НЕ на его адресные шины присоединяются не при 1, а при 0, и в этом случае выход элемента 6 соединен со входом элемента 4 через инвертор 20

3. Контакты переключателя 5 замкнуты.

Емкость (объем) ПЗУ равна произведению и íà m. Выигрыш в количестве элементов получается при n

ПЗУ емкостью íà 1024 бита работает следующим образом. 30

Адреса разбиваются на группы

n=16 и m=64 (n m=16 64=1024), В этом случае количество блоков 1 равно 16, а элементы 6 имеют 32 входа (m/2).

Пусть на выходе запоминающего уст- 35 ройства требуется получить 1 при адресе lп и адресах: lm; 2m; 5m; 7m

8m; 15m; 16m; 20m; 23m; 26m; 30m;

32m; 35m; 40m; 45m; 47m; 48m; 64m; (m=18). . 40

Адрес — ln присоединяется к входу элемента 3, а адреса lm 2m; 5m, ..., 1

47m, 48m, 64m 6, „при этом замыкаются контакты переключателя.

При поступлении кода адреса ln u одного из кода адреса m указанного выше на выходе элемента 4 появляется отрицательный импульс, поступающий на вход элемента 2, на выходе которого образуется положительный тетпульс,50 соответствующий информационному знаку 1 . Пусть на выходе запоминающего устройства требуется Получить 1 при адресе Кд и при адРесах:

1m 3m; 6m; 12m; 13m; 15m; 17m; 20m; 55

21m; 25m; 27m; 30m; Зlm; 33m; 35m; 37m; 38m; 40тп; 41m; 44m; 4ám; 48m;

50m; 51m; 52m; 55m; 57m; 58m; 59m;

60m; 61m; 62m 63m; 64m (количество адресов равно 34). Так как элемент 6 имеет 32 входа, то к его входам присоединяются оставшиеся адреса, т.е. те, где должны быть 0, а именно:

2m; 4m; 5m; 7m; 8m; 9m; 10m; llm;

14m; 16m; ХВтпт 19m; 22m; 23m; 24m;

26m; 28m; 29m; 32m;. 34m; 36m; 39m;

42m; 43m; 45m; 47mI 49тпт 53m; 54m;

"56m, и замыкаются контакты переключателя. В этом случае, когда на нход элемента 6 не поступает сигнал, на выходе инвертора 3 высокий уровень и с выхода элемента 4 появляется отрицательный импульс.

При приходе сигнала на вход элемента б на ныходе инвертора 3 образуется отрицательный сигнал, который поступает на один иэ входов элемента 4.

В данном ПЗУ за счет наличия связей между элементами И, ИЛИ-HF. сокращается общее количество элементов запоминающего устройства. Так, для запоминающего устройства одного разряда на 1024 бита количество элементов сокращается йа 25%.

Формула изобретения

Постоянное запоминающее устройство, содержащее входной дешифратор, выходы которого соединены с нходами накопителя, выходной дешифратор, выходы которого соединены с первыми входами соответствующих элементов И, выходы которых йодключены к входам элемента ИЛИ, выход элемента ИЛИ являетcR выходом устройства, о т л и ч а—

1ю щ е е с я тем, что, с целью увеличения информационной емкости устройства, в него введены инверторы и переключатели, причем вход каждого инвертора и первый вход каждого переключателя соединены с соответству- . ющим выходом накопителя, выход каждого инвертора соединен с вторым входом соответствующего переключателя, выход которого соединен с вторым входом соответствующего элемента И.

Источники нттформации, принятые во внимание при экспертизе

1. Патент США У 3653004, кл. 340173, опублик. 1972.

2 ° Брик Е.A. Постоянные запоминающие устройства цифровых машин. Энергия, 1969, с.31, рис.18 (прототип).

943848

Составитель Л.Амусьева

Редактор М.Недолуженко Техред А. Бабинец . Корректор A.Ãðèöåíêî

Закаэ 5142/62 Тираж 622 Подписное

ВНИИПИ Государственного кОмитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент > г. Ужгород, ул. Проектная, 4