Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик пп 943849 (61) Дополнительное к авт. свид-ву (22) Заявлено 28. 01. 80 (21) 2873 721/18-24

fg)) Кп 3 с присоединением заявки ¹

G 11 С 27/00

Государственный комитет

СССР по делам изобретений и открытий (23) Приоритет

{53) УДК 681. 327 °.66(088.8) Опубликовано 150782. Бюллетень ¹ 26

Дата опубликования описания 15.07.82 (72) Авторы изобретения

А.П.Горшков и И.К.Крылов. (71) Заявитель (54) АНАЛОГОВОЕ ЗАПОМИНИОЩЕЕ УСТРОЙСТВО

Изобретение относится к автоматике и вычислительной технике и может быть использовано в аналого-цифровых преобразователях.

Известно аналоговое запоминающее устройство замкнутого типа, содержащее операционный усилитель, ключ, накопительный элемент, например конденсатор, и повторитель напряжения (1).

Обладая высокой статической точностью, устройство имеет невысокое быстродействие.

Известно также аналоговое Запоминающее устройство разомкнутого ти.па, содержащее входной буферный усилитель, ключ на полевом транзисторе, накопительный элемент, например конденсатор, и выходной буферный усилитель 2).

Известное устройство имеет более высокое. быстродействие, однако наличие существенных паразитных емкостей в ключевом элементе снижает точ:ность работы устройства.

Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство, содержащее первый и второй буферные усилители, накопительные элементы,. например конденсаторы, ключи, выполненные по мостовой диодной схеме, входной и выходной коммутаторы, каждый из которых выполнен на первом и втором транзисторах одного типа проводимости, третьем и четвертом транзисторах другого типа проводимости и двух стабилитронах 13 .

Недостатком известного аналогового запоминающего устройства является невысокая точность работы.

Целью изобретения является повышение точности работы аналогового запоминающего устройства.

15 Лля достижения указанной цели в аналоговое устройство, содержащее первый и второй буферные усилители, входы которых соединены соответственно с накопительными элементами, например с одними из обкладок конденсаторов, другие обкладки которых подключены к шине нулевого потенциала, ключи, выполненные по мостовой диодной схеме, причем к

25 первым диагоналям первого и второго ключей подключены соответственно вход первого буферного усилителя и первый вход устройства, вход второго буферного усилителя и второй

30 вход устройства, входной и выход943849 ной коммутаторы, каждый из которых выполнен на первом и втором транзисторах одного типа проводимости, третьем и четвертом транзисторах другого типа проводимости и двух стабилитронах, катоды которых подключены к коллекторам первого и второго транзисторов, а аноды— к коллекторам третьего и четвертого транзисторов, ко второй диаго.нали первого ключа подключены катод 1 первого и анод второго стабилитронов входного коммутатора, к первым диагоналям третьего и четвертого ключей подключены выходы буферных усилителей и выход устройства, к второй диагонали третьего ключа подключен катод первого и анод второго стабилитронов выходного коммутатора, а анод первого и катод второго стабилитронов подключены к второй диагонали четвертого ключа, эмиттеры транзисторов коммутаторов соединены с шинами питания, базы транзисторов подключены к шинам управления, введены дополнительный коммутатор

И элементы с йелинейной характерис-тикой, например диоды, анод первого из которых соединен с анодом первого стабилитрона входного коммутатора, катод первого диода подключен к выходу первого буферного усилителя и аноду второго диода, катод которого соединен с катодом второго стабилитрона входного коммутатора, анод третьего диода соединен с анодом второго стабилитрона дополнительного коммутатора, катод третьего диода подключен к выходу второго буферного усилителя и к аноду четвертого диода, катод которого соединен с катодом первого стабилитрона дополнительного коммутатора, аноды третьего и четвертого диодов второго ключа соединены с анодом первого стабилитрона дополнительного коммутатора, катбды первого и третьего диодов второго ключа соединены с катодом второго стабилитрона дополнительного коммутатора, базы транзисторов которого подключены к шинам управления, а эмиттеры - к шинам питания.

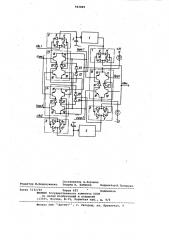

На чертеже представлена принципиальная схема аналогового запоминающего устройства.

Аналоговое запоминающее устройство содержит первый и второй буфер- ные усилители l и 2, накопительные элементы, например конденсаторы 3 и 4, ключи 5-8, выполненные по мостовой схеме на диодах 9-12, входные и выходной коммутаторы 13-15, каждый из которых выполнен на первом и втором транзисторах 16 и 17 од-. ного типа проводимости, третьем и четвертом транзисторах 18 и 19 другого типа проводимости и двух стабилитронах 20 и 21, элементы с нелинейной характеристикой, например диоды 22-25 °

Аналоговое запоминающее устройство работает следующим образом.

При подаче управляющих сигналов

U < П упр H Пупр à c апра откР ются первый и четвертый транзисторы 16 и 19, входных коммутаторов 13

0 и 14 и второй и третий транзисторы

17 и 18 выходного коммутатора 15.

В результате обеспечивается открытое состояние первого и второго диодов 22 и 23 и закрытое - третьего

5 и четвертого диодов 24 и 25, а также замкнутое состояние второго и третьего ключей б и 7 и разомкнутое— первого и четвертого ключей 5 и 8.

Следовательно, на конденсаторе 4 повторяется напряжение U>, поступающее на второй вход устройства, а на выход устройства через буферный усилитель 1 и ключ 7 поступает напряжение с конденсатора 3, уровень которого соответствует значению сигнала на первом входе устройства

U@ < в момент подачи указанных управляющих сигналов. Напряжение с выхода буферного усилителя 1 подается также через диоды 22 и 23 на

;входной коммутатор 13 для фиксации уровней напряжений запирания диодов

9 и 11 первого ключа 5. При подаче управляющих сигналов

ДРУ ой фазы, т.е. когДа Uyn<<> БупР4 и U> „

40 обеспечивается закрытое состояние диодов 22 и 23 и открытое — диодов

24.и 25, а также разомкнутое состояние второго и третьего ключей б и 7"и замкнутое — первого и четвер45 того ключей 5 и 8. В этом случае на конденсаторе 3 повторяется напряжение 0, поступающее на первый вход устройства, а на выход устройства через буферный усилитель

50 2 и ключ 8 поступает напряжение с конденсатора 4, уровень .которого соответствует значению сигнала на втором входе устройства в момент изменения фазы управляющих сигналов.

Напряжение с выхода буферного усилителя 2 подается также через диоды

24 и 25 на входной коммутатор 14 для фиксации уровней напряжений запира ния диодов 9 и 11 второго ключа б.

Иэ сказанного следует, что при. равенстве (c заданной точностью) напряжений на стабилитронах 20 и 21 и диодах 22 и 23, 24 и 25 запирающие напряжения на первом и третьем диодах

65 9 и 11 ключей 5 и б равны по величине

943849 и не зависят от текущих значений сигналов U8< и Uy, поступающих на входы аналогового запоминающего устройства. Следовательно, напряжения на конденсаторах 3 и 4 на этапе хранения не изменяются при изменении 5 напряжений на входах устройства, т.е. точность работй устройства оказывает:ся выше по сравнению с известным устройством.

Таким образом, введение дополнительного коммутатора и элементов с нелинейной характеристикой, например диодов, позволяет по сравнению с базовым устройством уменьшить на этапе хранения пролезание на выход устройства входных сигналов с десятков милливольт до долей милливольт. Это позволяет повысить точность аналогового запоминающего устройства и использовать его в аналого-20 цифровых преебразователях при кодировании быстро флюктуирующих сигналов. первого ключа подключены катод пер=. вого и анод второго стабилитронов входного коммутатора, к первым диагоналям третьего и четвертого ключей подключены выходы буферных усилителей и выход устройства, к второй диагонали третьего ключа подключены катод первого и анод второго стабилитронов выходного коммутатора, а анод первого и катод второго стабилитронов подключены к второй диагонали четвертого ключа, эмиттеры транзисторов коммутаторов соединены с шинами питания, базы транзисторов подключены к шинам управления, о тл и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введены дополнительный коммутатор и элементы с нелинейной характеристикой, например диоды, анод пЕрвого из которых соединен с анодом первого стабилитрона входного коммутатора, катод первого диода подключен к выходу первого буферного усилителя и к аноду второго диода, катод которого соединен с катодом второго стабилитрона входного коммутатора, анод третьего диода соединен с анодом второго стабилитрона дополнительного коммутатора, катод третьего диода подключен к выходу второго буферного усилителя и к аноду четвертого диода, катод которого соединен с катодом первого стабилитрона дополнительного коммутатора, аноды третьего и четвертого дио.дов второго ключа соединены с анодом первого стабилитрона дополнительного коммутатора, катоды первого и третьего диодов второго ключа соединены с катодом второго стабилитрона дополнительного коммутатора, базы транзисторов которого подключены к шинам управления, а эмиттеры к шинам питания.

Источники информации, принятые во внимание при экспертизе

1. Заявка ФРГ 9 2646161; кл. G 11 С 27/00, опублик. 1977.

2. Зарубежная радиоэлектрони;ка, 1978, 9 10, с.. 71 °

3. Автометрия, 1975, 9 1, с. 115 (прототип) 25

Формула изобретения

Аналоговое запоминающее устройство, содержащее первый и второй буферные усилители, входы которых сое« 30 динены соответственно с накопитель.ными элементами, например с одними иэ обкладок конденсаторов, другие обкладки которых подключены к шине . нулевого потенциала, ключи, вынол- З5 ненные по мостовой диодиой схеме, причем к первым диагоналям первого и второго ключей подключены соответственно вход первого буферного усилителя и первый вход устройства, вход второго буферного. усилителя и второй вход устройства, входной и выходной коммутаторы, каждый из которых выполнен на первом и втором транзисторах одного типа проводимости, третьем и четвертом транзисто- 45 рах другого типа проводимости и двух стабилитронах, катоды которых подключены к коллекторам первого и второго транзисторов, а аноды - к ,коллекторам третьего и четвертого Ю транзисторов, к второй диагонали

943849

Составитель A.Âîðîíèí

Редактор М.Недолуженко Техред A. Бабинец КорректорA.Гриценко

Заказ 5142/б2 Тираж 622 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 филиал ППП Патент > г. Ужгород, ул. Проектная, 4