Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскнк

Сецкалкстнческкк

Республик

oi>943853 (6!) Дополнительное к авт. свид-ву 22) Заявлено 25. 12. 80 (21) 3224446/18-24 с присоединением заявки ¹(23) Приоритет Опубликовано 1507.82. Бюллетень ¹ 26

Дата опубликования описания 15.07.82

f51) M Кп з

G 1l С 27/00

Государственный комитет

СССР по делам изобретений и открытий

{53) УДК 681. 327. .66 (088 ° 8) 1 3 „ЫФРВЗув49

" 74 " (Ф и Я (72) Автор изобретения

В К Чепалов (71 ) Заявитель (54) АНАЛОГОВОЕ ЗА ОМИНАКМЦЕЕ УСТРОИСТВО

1

Изобретение относится к измерительной технике и может быть использовано как входное устройство в аналого-. цифровых преобразователях.

Известно аналоговое запоминающее устройство, содержащее ключ на полевом транзисторе, управление которым осуществляется .по цепи затвора, и конденсатор. Управляющая шина через иивертор соединена также с затвором. дополнительного полевого транзистора (ключа), сток которого соединен со стоком ключевого полевого транзистора.

Дополнительный полевой транзистор используется для компенсации паразитных выбросов, обусловленных прохождением фронтов управляющих импульсов через параэитные емкости ключа.

На конденсатор выбросы приходят в противофазе (благодаря включению инвертора) и компенсируют друг друга (1).

Однако полная компенсация выбросов возможна только при полной идентичности параметров полевых транзисто- 25 ров и строгом равенстве длительности фронтон импульсов в шине управления и на выходе инвертора, что практически трудновыполнимо в условиях серийного производства. 30

Известна также ячейка аналоговой памяти, содержащая два последовательно включенных ключа на полевых тран-. зисторах, эатво1ы кото1ых через конденсаторы соединены с нулевой шиной, а управляющее напряжение подается на. подвижный контакт переменного резистора, включенного между затворами обоих ключей. Включение двух последовательных ключей, один иэ которых епережает или отстает в работе от дру гого благодаря включению регулируемых RC-цепей в затворы обоих транзисторов, позволяет устранить поме" ховый сигнал на накопительном конденсаторе с большой степенью точности, исключить из схемы инвертирующее устройство и применять любые пары транзисторов одного типа беэ предварительного подбора по параметрам (2).

Однако данная ячейка памяти имеет большую апертурную погрешность, вызванную увеличением времени переключения ключей за счет введения емкостей в цепи затворов транзисторов.

Наиболее близким по технической сущности к предлагаемому является аналоговое запоминающее устройство; сОдержащее ключ на полевом транэис943853 торе, запоминающую емкость, компенсирующую емкость, два ключа на биполярных транзисторах, на которые по„цаются разнополярные управляющие сигналы. Коллектор одного иэ ключей подключен к затвору ключевого полевого транзистора, коллектор второго биполярного ключа — к одной обкладке компенсирующей емкости, вторая обкладка которой подключена к выходу ключа на полевом транзисторе. 10

Благодаря наличию регулировки в коллекторе второго биполярного ключа возможно и зменение компенсирующего сигнала, поступающего через компенсирующую емкость. В данном устройстве также обеспечивается малая апертурная погрешность, так как отсутствуют реактивные элементы в цепи з а i во ра ключе в ого полевого тра н зи стора (3) .

Недостатком известного устройства является сравнительно малая точность запоминания, обусловленная компенсацией прохождения выбросов от коммутирующего напряжения на запоминающую емкость. Это обусловлено тем, что схема управления полевым транзистором выполнена íà основе насыщенных ключей, причем при переходе от режима выборки к режиму заполнения один ключевой биполярный транзистор переходит от режима запирания к режиму насыщения, в то время как другой ключевой транзистор переходит от режима насыщения к режиму запирания. Если переход от запирания 35 к насыщению в транзисторах осуществля. ется за сравнительно короткое время (т.е. с крутым фронтом), то время обратного переключения обычно на порядок больше, т.е. переключение осу- 4() ществляется с большой длительностью фронта, что обусловлено процессом рассасывания носителей в базе биполяр ного транзистора. Причем длительность фронта выхода из насыщения зависит 45 от множества факторов — от температуры окружающей среды, коэффициента перадачи тока транзистора, величины базового тока и т.д. Поскольку величина помехового сигнала на запоминающей емкости зависит от длительности фронта управляющего и компенсирую. щего сигналов, это обуславливает его зависимость от перечисленных факторов, а следовательно, вызывает ухудшу шение точности и стабильности всего запоминающего устройства.

Цель изобретения — повьааение точ.ности устройства.

Поставленная цель достигается тем, что в устройство, содержащее первый усилитель, выход которого соединен с первым накопительным элементом, например с одной из обкладок первого конденсатора, второй накопительный элемент, например второй конденса- 65 тор, одна из обкладок которого соединена с шиной нулевого потенциала, другие обкладки конденсаторов соединены с выходом ключа и являются выходом устройства, первый вход ключа соединен с входной шиной, второй усилитель, выход которого соединен с вторым входом ключа, первые входы усилителей соединены с второй шиной питания, введены переключатель тока, первый и второй нелинейные элементы, первые выводы которых соединены соответственно. с выходами переключателя тока, первый и второй входы переключателя тока являются управляющими входами устройства, третий вход переключателя тока подключен к первой шине питания, вторые выводы нелинейных элементов подключены к второй шине питания, третьи выводы нелинейных элементов соединены с соотвест вующими вторыми входами усилителей ! и с соответствующими первыми выводами нелинейных элементов, выходы усилителей через резисторы соединены с первой шиной питания.

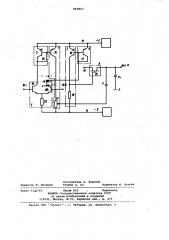

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит усилители 1 и 2, нелинейные элементы 3 и 4, переключатель 5 тока, шину 6 нулевоimp потенциала, накопительные элементы, например конденсаторы 7 н 8, ключ 9, входную шину 10, шины 11 и 12 питания, выход устройства 13.

Переключатель 5 тока выполнен на транзисторах 14 и 15; усилитель 1 на транзисторе 16 и резисторе 17; усилитель 2 - на транзисторе 18 и резисторе 19; нелинейные элементы— на транзисторах 20 и 21; ключ 9 на полевом транзисторе 22. Эмиттеры транзисторов 14 и 15 соединены с шиной 11 питания через резистор 23.

Транзисторы 16 и 20, 18 и 21 образуют отражатели тока, нагрузками которых являются соответственно резисторы 17 и 19.

Предложенное устройство функционирует следующим образом.

В исходном состоянии на управляющие входы Эх и Вх < подаются. уровни обеспечивающие запирание транзистора 14 и открывание транзистора 15 переключателя 5 тока. Коллекторный ток транзистора 15 обеспечивает прямое смещение транзистора 21 нелинейного элемента 4, что обуславливает протекание тока через транзистор 18, причем коллекторный ток транзистора

18 равен по величине коллекторному току транзистора 15 при идентичных параметрах транзисторов 18 и 21 (в этом заключается принцип работы отражателя тока); Коллекторный ток транзистора 18 создает падение напряжения на резисторе 19, поступающее

943853 на затвор полевого транзистора 22 и поддерживающее ключ 9 в открытом состоянии. Входной сигнал при этом воспроизводится на выходе устройства с задержкой, характерной для интегрирующей йс-цепи, где a - паразитное сопротивление открытого транзистора

22; С - величина конденсатора 8.

При переходе в режим запоминания переключаются логические уровни на входах Sxq и Вхд и ток, задаваемый -10 резистором 23, переключается транзисторами 14 и 15 в отражатель тока, образованный транзисторами 20 и 16.

При этом ток отражателя тока на транзисторах„ 18 и 21 выключается.

Это обеспечивает формирование отри- цательного перепада напряжения на затворе полевого транзистора 22, в результате чего транзистор 22 закрывается и устройство переходит в режим хранения напряжения, присутствующего в этот моьМнт на конденсаторе

8. На резисторе 17 при этом формируется положительный перепад напряжения, поступающий с подвижного контак- 5 та резистора 17 через конденсатор 7 на конденсатор 8, тем самым компенсируя прохождение помехового сигнала через паразистные емкости транзистора 22. Путем изменения положения подвижного контакта резистора 17 изменяется амплитуда компенсирующего сигнала и возможна полная компенсация помехи не конденсаторе 8.

Характерной особенностью предложенного устройства является использо- З5 ванне в нем ненасыщенных ключей (переключателей тока) в качестве формирователей управляющего и компенсирующего сигналов. Это обеспечивает большое быстродействие устройства 40 малую величину апертурной погрешности, практически равные по длительности фронты управляющего и компенсирующего сигналов. В устройстве не требуется дополнительный инвертор для получения компенсирующего сигнала, поскольку в симметричной переключательной схеме инверсный управляющий сигнал образуется автоматически.

Применение отражателей тока позволяет,, получить управляющий перепад на затворе ключевого транзистора 22, меняющийся от величины -Е до величины +Е, т.е. в данном устройстве напряжения источников питания полностью используются для формирования управляющего сигнала, чего нельзя достичь в обычной схеме переключателя тока, где формируемый сигнал обычно значи тельно меньше величин питающих напряжений. Увеличение же управляющих напряжений на затворе транзистора 22 обуславливает расширение диапазона входных коммутирующих сигналов. Использование симметричной пЕреключательной схемы обеспечивает малые по величине броски в цепях питания и корпуса, снижает уровень наводок и дополнительно повышает точность запоминания малых сигналов. формула изобретения

Аналоговое запоминающее устройство, содержащее первый усилитель, выход которого соединен с первым накопительным элементом, например с одной из обкладок первого конденсатора, второй накопительный элемент, !

::например второй конденсатор, одна из обкладок которого соединена с 1шиной нулевого потенциала, другие обкладки конденсаторов соединены с выходом ключа и являются выходом устройства, первый вход ключа соединен с входной шиной, второй усилитель, выход которого соединен с вторым входом ключа, первые входы усилителей соединены с второй шиной питания, о т л и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введены переключатель тока, первый и второй нелинейные элементы, первые выводы которых соединены соответственно с выходами переключателя тока, первый и второй входы пепереключателя тока являются управляющими входами устройства, третий вход переключателя тока подключен к первой шине питания, вторые выводы нелинейных элементов .подключены к второй шине питания, третьи .выводы нелинейных элементов соединены с соответствующими вторыми входами усилителей и с соответствующими первыми выводами нелинейных элементов, выходы усилителей через резисторы соединены с первой шиной питания.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

9 462216, кл. G 11 С 27/00, 1974.

2. Авторское свидетельство СССР

М 733031, кл. G 11 С 27/00, 1979.

3. Приборы и элементы автоматики и вычислительной техники. Экспрессинформация, 36, 1979, с. 23 (прототип).

943853

Редактор М. Петрова

Филиал ППП Патент, г. Ухгород, ул. Проектная, 4

Составитель A. Воронин

Техред A. Ач Корректор М. Шароши

Заказ 51+/63 Тирам 622 . . Подписное

ВНИИПИ Государственного комитета СССР по делам изобретениИ и отк1жтий

113035, Москва, Ж-35, Раушская наб., д. 4/5