Управляемый фильтр

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистичесиик

Респубблик (ii >9440&0 (6I ) Дополнительное к авт. свил-ву (5l)М. Кл.

Н 03 Н 21/00 (22) -Заявлено 17. 12. 80 (2I ) 3221841/18-09 с присоелиненнем заявки № 3221842/09 (23) П ио итет "

3ЪорАерстеккоый кометет СССР во Амам взобретенкй н открытий р р

Опубликовано 15.07.82. Бюллетень № 26 (53) УДК 621 396. .96(088.8) Дата опубликования описания 1 .07.82

В.П.Авдеев, H.À.Ôîìèí, И.П.Строков, Е.fl.Ãèëüáo, Т.M.Äàíèåëÿí, А.А.Ершов, В.А.Столяр, Я.Г.Парпаров и А.А.Берлин (72) Aexopb> изобретения

Сибирский металлургический институт им. Серго Орджоникидзе „. и Кузнецкий металлургический комбинат им.В.И.Ленйнэ (7I) Заявители

1 54) УПРАВЛЯЕМЫЙ ФИЛЬТР

Изобретение относится к радиотехнике и может быть использовано для выделения полезной низкочастотной составляющей измеренных сигналов.

Известен управляемый фильтр, содержащий блок сравнения, ограничитель и интегратор, выход которого соединен с другим входом блока сравнения (1).

Недостатком известного устройства является низкая точность выделения полезного сигнала в случае длительных по времени и значительных по амплитуде искажений сигнала на входе устройства. Это обусловлено тем, что на выходе интегратора имеется ошибка, определяемая соотношением (3

8= — т„„ где Ттт - постоянная времени интегрирующего звена;

Тгр - длительность грубой помехи;

1э — зона ограничения в ограни2 чителе. Если задана максимально допустимая погрешность оценки полезного сигнала о вследствие влияния грубой ои помехи, то эта точность может быть обеспечена при условии н грВ противном случае устройство не отвечает предъявляемым к нему требованиям по точности.

Цель изобретения - повышение точности выделения полезного сигнала при наличии длительных по времени и по . амплитуде искажений входного сигнала.

Для этого в управляемом фильтре, содержащем блок сравнения и последовательно включенные ограничитель и интегратор, выход которого соединен с другим входом блока сравнения, между выходом блока сравнения и входом ограничителя включен мажоритарный элемент, другой вход которого

:подключен к выходу блока сравнения

3 94408 через первый элемент задержки, а третий вход через второй элемент задержки - к выходу первого элемента задержки.

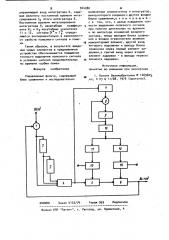

На чертеже представлена структурная электрическая схема управляемого фильтра.

Управляемый фильтр содержит блок 0

1 сравнения, первый вход которого подключен к входу устройства, а выход через последовательно соединенные элементы задержки 2 и 3 - к третьему входу мажоритарного элемента 4, первый и второй входы которого соединены соответственно с выходом блока

1 сравнения и выходом элемента 2 задержки, выход же мажоритарного элемента 4 подключен через ограничитель

5 к входу интегратора 6, выходом со20 единенного с вторым входом блока 1 сравнения и с выходом устройства.Блоки 7-14 предназначены для настроек величины ограничивающего напряжения ограничителя 5 и постоянной времени интегрирования Ти интегратора 6. Вход детектора знака 7 подключен к выходу мажоритарного элемента 4, а выход - к первому входу блока 8 сравнения, выход которого соединен с входом интегратора 9,выход которого подключен к второму входу блока 8 сравнения и к входу квадрата 10. Выход квадратора 10 подключен к входам двух масштабных уси- 35 лителей 11 и 12. Выход масштабного усилителя 11 соединен с первым входом сумматора 13, второй вход которого связан с источником сигнала постоянной величины, а выход - с управ- 40 ляющим входом ограничителя 5. Выход второго масштабного усилителя 12 соединен с первым входом сумматора 14, второй вход которого подключен к источнику сигнала постоянной Величи- 45 ны, а выход - к управляющему входу интегратора 6.

Устройство работает следующим образом. 50

Входной сигнал поступает на вход блока 1 сравнения, в котором из него вычитается выходной сигнал устройства, и получаемая разность E, (t) 55 непосредственно и через элементы 2 и 3 задержки поступает на входы мажоритарного элемента 4. Длитель0 4 ность задержки 7 в элементах задержки 2 и 3 определяется по выражению где Тщс у, - максимальная длительность грубой помехи; вю»

Тя - и пах - соответственно минимальное и максимальное значение параметров управляемого фильтра. Если

E (t) содержит грубые помехи, то они отфильтровывается в мажоритарном эле.менте 4 благодаря совместной обработке трех отсчетов сигнала E соответственно в моменты t, (t-ь) и (t-2 c) и частично в ограничителе 5.

В мажоритарном элементе 4 осуществляется выбор центрального члена вариационного ряда, построенный из мгновенных значений поступающих на него сигналов, Сигнал спд> (t) с выхода мажоритарного элемента 4 поступает на вход ограничителя 5 и на вход детектора знака 7. Если E щд (й) превышает величину ограничивающего напряжения Р ограничителя 5, то в ограничителе 5 он ограничивается до этой величины. Сигнал с выхода . ограничителя 5 поступает на вход интегратора 6. На выходе интегратора

6 получается сглаженный сигнал, который и поступает на выход устройства. Сигнал с выхода детектора знака 7, равный +1 или -1 в зависимости от знака сигнала Я,дд (й), поступающего на вход детектора знака 7 с выхода мажоритарного элемента 4, поступает на первый вход блока 8 сравнения, в котором от него вычитается выходной сигнал интегратора 9, и разность поступает на вход этого же интегратора 9, а на выходе его получается сглаженный сигнал от детектора знака 7. С выхода интегратора 9 сигнал через квадратор 10, в котором он возводится в квадрат, поступает на входы двух масштабных усилителей 11 и 12, где производится умножение сигнала на коэффициенты К и К . Выходной сигнал масштабного усилителя

ll суммируется в сумматоре 13 с постоянным сигналом и поступает на управляющий вход ограничителя 5, задавая величину ограничивающего напряжения (Ь . Выходной сигнал второго масштабного усилителя 12 суммируется во втором сумматоре 14 с постоянным сигналом Ти и поступает на

Источники информации, принятые во внимание при экспертизе

Формула изобретения

Управляемый фильтр, содержащий 1. Патент Великобритании Р 1469605 блок сравнения и последовательно кл, Н 03 G 11/08, 1975 (прототип).

ВНИИПИ Заказ 5153/74: Тираж 959 Подписное филиал ППП "Патент", r. Ужгород, ул. Проектная, 4

5 9440 управляющий вход интегратора 6, задавая величину постоянной времени инте- грирования Т этого интегратора б.

Постоянная времени интегрирования интегратора 9, масштабные коэффициенты К и К масштабных усилителей

11 .и 12, сигналы,Р и Т> опреде% % ляются экспериментально в зависимости от свойств полезного сигнала и помехи. 1О

Таким образом, в результате введения новых элементов в предложенном устройстве обеспечивается повышение точности выделения полезного сигнала в условиях наличия продолжительных 1S по времени грубых помех.

80 6 включенные ограничитель и интегратор, выход которого соединен с другим входом блока сравнения,о т л и ч а ю щ и йс я тем, что, с целью повышения точ-. ности выделения полезного сигнала при наличии длительных по времени и по амплитуде искажений входного сигнала, между выходом блока сравнения и входом ограничителя включен мажоритарный элемент, другой вход которого подключен к выходу блока сравнения через первый элемент задержки,а третий вход через второй элемент задержки - к выходу первого элемента задержки.