Устройство для исправления ошибок в кодовой комбинации

Иллюстрации

Показать всеРеферат

Союз Советскик

Соцмапмсткческмк

Республик

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Н 04 L 1(10

3Ьоудоротееииый комитет

СССР ае делам изобретений и открытий (23) Приоритет(53) УДК 621. .394. 14 (088. 8) Опубликовано 15.07.82. Бюллетень № 26 . Дата опубликования описания 18.07.82

В. Н, Червяцов и В, В. Евстафьев

I (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК

В КОДОВОЙ КОМБИНАБИИ

Изобретение относится к электросвязи и может быть использовано в аппа, ратуре нередачи - приема дискретной информации, Известно:устройство для исправления ошибок в кодовой комбинации, содесокащее последовательно соединенные первый пороговый блок, первый ключ, первый сумматор по модулю два, элемент И, второй сумматор по модулю два, первый io элемент ИЛИ и блок обнаружения ошибок, а также второй пороговый блок и последсвательно соединенные второй элемент ИЛИ и накопитель, при этом входы первого и второго пороговых блоков обье-л динены, а выход второго блока подключен к второму вхоау эжмента И, первый и второй выходь| первого ключа подсоединены соответственно к вторым входам второго сумматора по модулю два и первого о эжмента ИЛИ (1).

Однако известное устройство характеризуется низкой помехоустойчивостью.

Цель изобретения - повышение помех -. устойчивости.

Поставленная цель достигается тем, что в устройство для исправления ошибок в кодовой последовательности, содержащее последовательно соединенные первый лоро» говый блок, первый ключ, первый сумма» тор но модулю два, элемент И, второй сумматор по модулю два, первыи элемент

ИЛИ и блок обнаружения ошибок, а также второй пороговый блок и последовательно соединенные второй эжмент ИЛИ и накопитель, при этом входы первого и второго пороговых блоков обьединены, а выход второго порогового блока подключен к второму вхо у элемента И, первый и второй выходы первого ключа подсоединены соответственно к вторым входам второго сумматора по модулю два и первого эжмента ИЛИ, введены второй ключ и послв доватетеьно соединенные третий суммато j по мосС лю два и элемент ЗАПРЕТ, выход которого подключен к первому входу вто3 944 рого элемента ИЛИ, к второму вхоцу которого подключен первый выход блока обнаружения ошибок, второй выход которого подключен к второму входу первого ключа, второму входу элемента ЗАПРЕТ, тре- g тьему входу второго элемента ИЛИ и управляющему входу второго ключа, к информационному входу которого подключен выход накопителя, а выходы второго ключа подключены соответственно к третьему 1О входу первого элемента ИЛИ и второму входу первого сумматора по модулю два, при этом к входам третьего сумматора по модулю два подключены выходы первого и второго пороговых блоков. 35

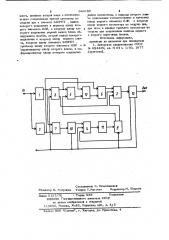

На чертеже приведена структурная ° электрическая схема предложенного устройства.

Устройство содержит первый пороговый блок 1, второй пороговый блок 2, щ элементы ИЛИ 3 и 4, сумматоры 5-7 по модулю два, ключи 8 и 9, элемент 10 . ЗАПРЕТА, накопитель 11, элемент И 12, блок 13 обнаружения ошибок.

Устройство работает следующим обра- 2$ зом.

Принятая. кодовая комбинация поступает на входы первого и второго пороговых блоков 1 и 2, С выхода первого порогового блока 1 первая модификация кодовой щ комбинации через первый ключ 8, первый элемент ИЛИ 3 поступает в блок 13 обнаружения ошибок.

Кроме того, эта же последовательность поступает на первый вход третьего сумма-З тора 7, на второй вход которого поступают сигналы стирания с выхода второго порогового блока 2, преобразованные предварительно в единичные сигналы. С выхода третьего сумматора 7 по модулю. два кодовая комбинация, позиции которой инвертированы сигналами стирания (вторая модификация) поступает через элемент 10

ЗАПРЕТ, второй элемент ИДИ 4 в накопитель 11. Блок 13 обнаружения ошибок осу1цествляет кодовую проверку комбинации первой модификации. Если ошибки не обнаруживаются, первая модификация выдается получателю на выход устройства.

В случае обнаружения ошибок блок 13 обнаружения ошибок выдает первую моди» фикацию по первому выхоцу через второй элемент ИЛИ 4 в накопитель 11. При этом из накопителя 11 выводится вторая модификация, которая через второй ключ

9, первый элемент ИЛИ 3 поступает в блок 13 обнаружения ошибок . сли ошибка не обнаруживается, то вторая модифика130 4 ция выдается на выход ус:тройства. В случае обнаружения ошибки блок 13 обнаружения ошибок выдает вто)зую модификацию кодовой комбинации второй элемент ИЛИ

4 в накопитель 11. Одновременно из блока 13 обнаружения ошибок подают сигналы на управляющие входы ключей 8 и 9, на второй вход эжмента 10 ЗАПРЕТ

Из накопителя 11 первая модификация кодовой комбинации первого повторения поступает через второй ключ 9 на второй вход первого сумматора 5 по модулю два.

На первый вход первого сумматора 5 по модулю два через первый ключ 8 поступает с выхода первого порогового блока

1 комбинация первой модификации. Для исправления ошибок в первом сумматоре 5 по модулю два происходит поразрядное сравнение обоих комбинаций. Результат сравнения поступает на один из входов элемента И 12, на другой вход которого подаются сигналы стирания с выхода второго порогового блока 2. Инвертирование элементов комбинации второго повторения во втором сумматоре 6 по модулю два происходит в том случае, если на входах элемента И 12 одновременно появляется сигнал несовпадения с первого с умматора 5 по модулю два и сигнал стирания от второго порогового блока 2. Исправжвжнная комбинация поступает в блок 13 обнаружение ошибок выдается получателю.

Использование предлагаемого устройства обеспечивает повышение помехоустойчивости и скорости передачи за счет уменьшения числа повторных передач сообщения.

Ф ормула изобретения

Устройство для исправдения ошибок в кодовой комбинации, содержащее последовательно соединенные первый пороговый блок, первый ключ, первый сумматор по модулю два, элемент И, второй сумматор по модулю два, первый элемент ИЛИ и блок обнаружения ошибок, а также второй пороговый блок и последовательно соединенные второй элемент ИДИ и накопитель, при этом входы первого и второго пороговых блоков обьединены, а выход второго порогового блока подключены к второму входу элемента И, первый и второй выходы первого ключа подсоединены соответственно к вторым входам второго сумматора по модулю два и первого элемента ИЛИ, о.т л и ч а ю щ е е с я тем, что, с целью повышения помехоустайчи5 944 вести, введены второй ключ и последовательно соединенные третий сумматор по модулю два и элемент ЗАПРЕТ, выход которого подключен к первому входу второго элемента ИЛИ, к второму входу кс торого подключен первый выход блока обнаружения ошибок, второй выход которого подключен к второму входу первого ключа, второму входу, элемента ЗАПРЕТ третьему входу второго элемента ИЛИ и IO управляющему входу второго ключа, к информационному входу которого подключен

130 6 выход накопителя, à выходы второго клв» ча подключены соответственно к третьему входу первого элемента ИЛИ и второму входу первого сумматора по модулю два, при этом к входам третьего сумматора по модулю два подключены выходы первого и второго пороговых блокса.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 634469, кл. Н 04 Là 1(101 1977 ,(прототи ).

Составитель.С. Осмоловский

Редактор И. Митровка Техред Т.Мат очка Корректор М. Шароши

Заказ 5157(76 i Тираж 688 П одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-Э5, Раушская наб., д, 4/ 5

Филиал ППП "Патент, г. Ужгород, ул. Проектная, 4