Устройство для фазовой синхронизации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

«»944133 (6! ) Дополнительное к авт. саид-ву (22)Заявлено 31.12.80(2I) 3227307/18-09 с присоединением заявки ле— (St)N. Кл.

Я 04 Ь 7/06

3ЪеудврстеаввИ комитет

CCCP ае двам кзобретевкй к етхрытвк

{2З) Приоритет (53) УДК 621.394, .662 (088.8}

Опубликовано 15.07.82. Бюллетень М 26

Дата опубликования описания 17.07.82

В. В. Иеркуль и И. И Русак (72) Авторы изобретения (7l) Заявитель (54} УСТРОЙСТВО ДЛЯ ФАЗОВОЙ СИНХРОНИЗАЦИИ

Изобретение относится к технике передачи дискретной информации H& расстояние и может быть использовано в аппаратуре приема дискретной информации по линиям связи.

Известно устройство для фаэовой синхронизации, содержащее последовательно соединенные интегратор, управляемый генератор, делитель частоты и счетчик синхроимпульсов, а также элемент И tl3.

Однако известное устройство имеет сравнительно низкую точность синхрони зации, обусловленную сравнительно большим периодом измерения величины фазового рассогласования. 15

Цель изобретения — повышение точности синхронизации путем уменьшения периода измерения величины фазового рассогласования. .Цель достигается тем, что в устрой- 2о ство для фаэовой синхронизации, содержащее последовательно соединенные интегратор, управляемый генератор, делитель частоты и счетчик синхроимпульсов, а также элемент И, введены блок задержки и последовательно - соединенные блок выделения фронтов сигнала, преобразователь и регистр рассогласования, выходы которого подключены ко входу интегратора и первому входу элемента И, к второму входу которого подключен выход управляемого генератора, а выход элемента И подключен к счетному входу регистра рассогласования, при этом выход блока выделения фронтов сигнала через блок задержки подключен ко входу сброса счетчика синхроимпульсов и корректирующему входу делителя. частоты, выход которого подключен к второму входу преобразователя, к третьему входу которого подключен выход счетчика синхроимпульсов.

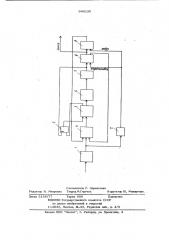

На чертеже представлена структурная электрическая схема устройства.

Устройство содержит блок 1 выделения фронтов сигнала, блок 2 задержки, элемент И 3, преобразователь 4, регистр 5 рассогласования, интегратор 6, 944133

3 управляемый генератор 7, делитель 8 частоты, счетчик 9 синхроимпульсов.

Устройство работает следующим образом.

Передние фронты сигналов информации с блока 1 вьщеления фронтов сигнала возбуждают преобразователь 4, на второй вход которого поступают сигналы со второго выхода делителя частоты, код на котором указывает величину рассо- !0 гласования фаз синхроимпульсов и сигналов информации, а на третий вход преобразователя поступают сигналы с выхода счетчика синхроимпульсов, код последнего фиксирует время отсутствия 15 сигналов информации из линии связи.

Преобразователь 4 путем деления кода делителя 8 частоты на код счетчика 9 . синхроимпульсов.определяет знак и код рассогласования и устанавливает в соответствующее положение триггеры на регистре 5.рассогласования.

Сигнал c,âûõoäà регистра 5 рассогласования возбуждает интегратор 6.

Время возбуждения интегратора 6 опре- деляется количеством синхроимпульсов, . поступающих на счетный вход регистра

5 рассогласования с элемента И 3, вы-. зывающих переполнение регистра 5 рассогласования. В случае переполнения Зо регистра 5 рассогласования прекращается появление сигналов с выхода элемента И 3 и производятся блокировка возбуждения интегратора 6. Задержанным сигналом с блока 1 выделения фронтов сигнала на блоке 2 задержки производится корректировка кода на делителе 8 частоты и сбрасывается код на счетчике

9 синхроимпульсов. Изменение потенциала на выходе интегратора 6 вызывает изменение частоты на выходе управляемого генератора 7.

Таким образом, устройство для фазо- вой синхронизации обеспечивает повышение точности синхронизации путем умень щения периода измерения величины фазового рассогласования.

Формула изобретения

Устройство для фазовой синхронизации, содержащее последовательно соединенные интегратор, управляемый генератор, делитель частоты и счетчик синхроимпульсов, а также элемент И, о т л и— ч а ю щ е е с я тем, что, с целью повышения точности синхронизации путем уменьшения периода измерения величины фазового рассогласования, введены блок задержки и последовательно соединенные блок выделения фронтов сигнала, преобразователь и регистр рассогласования, выходы которого подключены к входу интегратора и первому входу элемента И, к второму входу которого подключен выход управляемого. генератора, а выход элемента И подключен к счетному входу регистра рассогласования, при этом выход блока выделения фронтов сигнала через блок задержки подключен к входу сброса счетчика синхроимпульсов и корректирующему входу делителя частоты, выход которого подключен к второму входу преобразователя, к третьему входу которого подключен выход счетчика синхроимпульсов.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

И 605328., кл. Н. 044 7/06, 1972 (прототип).

944 133

Составитель Г. Лерантович

Редактор И. Митровка ТехредМ.Гергель Корректор Ю. Макаренко, Заказ 5158/77 Тираж 688 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3O35, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", r. Ужгород, ул. Проектная, 4