Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советскик

Социалистические

Республик (ii)944137 (61) Дополнительное к авт. санд-ву (22) Заявлено 11 02.81 (21) 3245831/18-09 с присоединением заявки М (233 П риоритет

Опубликовано 15.07.82. Бюллетень .йэ 2i6

{5! )м. Кл.

H,04 L 7/08

1Ъоударетееииый комитет

СССР ио делам изобретеиий и открытий (53) УДК 621.394. .662 { 088.8) Дата опубликования описания 15.07.82

В.С. Князькин, В.А. Трошанов и H. Ф. Юрков (72) Авторы изобретения (71) Заявитель (54} Устройство цикловой синхронизлции т

Изобретение относится к технике передачи информации и может использоваться для помехоустойчивой синхронизации сис» тем связи при передаче рекуррентных последовательностей.

Известно устройство цикловой синхронизации, содержащее первый сумматор по модулю два, выход .которого подключен к входу регистра сдвига с обратной связью и первому входу второго сумматора по модулю два, к второму входу которого, а также к первому входу третьего сумматора по модулю два подключен первый выход регистра сдвига с обратной связью, остальные выходы которого подключены к входам дешифратора, к соответствуюшему входу которого подключен выход счетчика временных интервалов, первый вход которого объединен с тактовым zo входом делителя частоты, а к остальным входам счетчика временных интервалов подключен выход второго сумматора по модулю два, при этом второй вход третьеro сумматора по модулю два обьединен с первым входом первого сумматора по модулю два, к второму входу которого подключен выход первого элемента И, а выход третьего сумматора по модулю два подключен к первым входам первого и второго элементов И, причем к второму входу первого элемента И подключен вы» ход триггера фазирования, первый вход которого объединен с первым входом триг гера интервалов и входом делителя частоты, выход которого подклточен к втс.ому входу триггера интервалов, прямой и инверсный выходы которого подключены соот;ветственно к блокируюшему входу делителя частоты и второму входу второго элемента И, выход которого подключен к третьему входу триггера интервалов и второму входу триггера фазирования Pl) .

Однако известное устройство обладает недостаточной помехозашишенностью иэза необходимости выделения без ошибок участка рекуррентной последовательности значительной ..длины.

При этоы на блокирующем входе делителя 11 частоты появляется низкий уровень напряжения, закрывающий вход делителя 11 частоты, а на входе элемента И 8 высокий уровень. Закон образования регистром 2. сдвига с обратной связью последовательности знаков аналогичен закону образования входной рекуррент— ной последовательности, поэтому после заполнения регистра 2 сдвига с обратной связью входной последовательностью, с выхода 14 формирования обратной связи и входа устройства на выходы третьего сумматора 6 по модулю два поступают одинаковые сигналы. При этом ошибки во входной последовательности или послед вательности первоначального заполнения регистра 2 сдвига с обратной связью приводят к появлению ошибочных знаков на одном из входов третьего сумматора 6 по модулю два. В результате этого первый сигнал ошибки, который появляется на выходе третьего сумматора 6 по мо

3 3441 . 3

Цель изобретения - повышение помехозашищенности.

Поставленная цель достигается тем, что в устройство цикловой синхрониза п и, содержащее первый сумматор по модулю два, выход которого подключен к входу .регистра сдвига с обратной связью и первому входу второго сумматора по модулю два, к второму входу которого, а также к первому входу тртье- 1о го сумматора по модулю два подключен первый выход регистра сдвига с обратной связью, остальные выходы которого подключены к входам дешифратора„к соответствующему входу которого подключен выход счетчика временных интервалов, первый вход которого объединен с тактовым входом делителя частоты, а к остальным входам счетчика временных интервалов подключен выход второго сумматора по модулю два, при этом второй вход третьего сумматора по модулю два объединен с первым входом первого сумма ора по модулю два, к второму входу которого подключен выход первого элемента И, а выход третьего сумматора по .модулю два подключен к первым. входам первого и второго элементов И, причем. к второму входу первого элемента И подключен выход триггера фазирования, первый вход которого объединен с первым входом триггера интервалов и входом делителя частоты, выход которого подключен к второму входу триггера интервалов, прямой и инверсный выходы которого подключены

35 соответственно к блокирующему входу делителя частоты и второму входу второго элементе И, выход которого. подключен к третьему входу триггера интервалов и второму входу триггера фазирования, введены последовательно соединенные линии задеркки, третий элемент И, и дополнительный сумматор по модулю два, к второму входу которого подключен выход р го разряда регистра сдвига с обрат45 ной связью, к входу (И+1) разряда которого подключен выход дополнительного сумматора по модулю два, а выход третьего сумматора по модулю два подключен к входу линии задержки и второму входу третьего элемента И, к третьему входу

50 которого подключен выход триггера фазирования, к третьему входу которого подключен выход дешифратора.

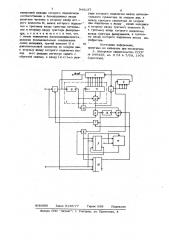

На чертеже представлена структурная схема устройства.

Устройство для цикловой синхронизации содержит первый сумматор 1 по модулю два, регистр 2 с обратной связью, вто7 4 рой сумматор 3 по модулю два, счетчик 4 временных интервалов, дешифратор 5, третий сумматор 6 ло модулю два, элементы И 7 и 8, триггер 9 интервалов, триггер 10. фазирования, делитель 11 частоты, регистр 2 сдвига с обратной связью содержит регистр 12 сдвига, регистр 13 сдвига, блок 14 формирования обратной связи, дополнительный сумматор 15 по модулю два, линия задержки 16, третий элемент И 1 7.

Устройство работает следующим образом.

При поступлении сигнала на первые входы триггеров 9 и 10 триггер 9 интервала устанавливается в единичное состояние, а триггер 10 фазирования и делитель

11 частоты — в нулевое состояние . При этом элементы И 7, И 8, И 17, закрыты и входная информация через первый сумматор 1 по модулю два поступает в регистр 2 сдвига с обратной связью без исправления в ней ошибок. Блокирующий вход делителя 11 частоты открыт высоким уровнем напряжения, поступающим с выхода триггера 9 интервалов и в делитель 1 1 частоты поступает тактовая частота. Через интервал времени, определяемый коэффициентом деления делителя 11 частоты и равный времени первоначального заполнения регистра 2 сдвига с обратной связью входной последовательностью, на выходе делителя 11 частоты появляет» ся сигнал, переводящий триггер 9 интервалов в нулевое состояние.

5 9441 дулю два проходит через DTKFbITbN второй элемент И 8 и устанавливает триггеры 9 и 10 в единичное состояние. Высокий уровень напряжения с выхода триггера 10 фазирования поступает на элемен-5 ты И 7 и И 17 и сигнал ошибки с выхода третьего сумматора 6 по модулю два поступает через первый элемент И 7 на вход первого сумматора 1 по модулю два, изменяя входной знак на противоположный . При этом происходит исправление ошибки, если она имела место на входе устройства, или внесение дополжтельной ошибки во входную рекуррентную последовательность, если она имела место 15 на выходе блока 14 формирования обратной связи регистра 2 сдвига с обратной связью

Одновременно сигнал ошибки с выхода третьего сумматора 6 по модулю два 20 поступает на вход линии задержки 16, время задержки которого равно времени задержки входного сигнала регистром 12 сдвига до первого выхода с регистра ? сдвига с обратной связью на вход б ка 25

14 формирования обратной связи.

Следовательно внесенная в регистр 2 сдвига с обратной связью дополнительная .ошибка через время задержки ее регистром 1 2 сдвига является причиной появле- 30 ния на выходе третьего сумматора 6 по модулю два нового сигнала ошибки, который поступает на вход третьего элемента И 17 одновременно с задержанным линией задержки 16 сигналом внесения в регистр 2 сдвига с обратной связью дополнительной ошибки. В результате этого на выходе третьего элемента И 1 7 появляется сигнал, который поступает на вход дополнительного сумматора 1 5 по модулю два и исправляет внесенную в рекуррентную последовательность ошибки.

Таким оробразом, ошибки во входной рекуррентной последовательности исправляются на первом сумматоре 1 по модулю 4 два, а ошибки в последовательности первоначального заполнения регистра 2 сдвига с обратной связью приводят к внесению дополнительных ошибок во входную рекуррентную последовательность с по—

50 следующим их исправлением на дополHHTGBbHoM сумматоре 15 по модулю два.

Исправлению не подаются двойные ошибки одновременно появляющиеся на входе регистра 2 сдвига с обратной связью и на выходе блока 14 формирования обратной

55 связи. В процессе заполнения регистра 2 сдвига с обратной связью входной рекуррентной последовательностью второй сумматор 3 по модулю два совместно со счетчиком 4 временного интервала обеспечивает отсчет безошибочного отрезка рекуррентной последовательности длительностью равной величине регистра 2 сдвига с обратной связью. После заполнения регистра 2 сдвига с обратной связью информацией без ошибок на выходе счетчика 4 временного интервала появляется сигнал, который открывает дешифратор 5.

При появлении в регистре сдвига 2 с обратной связью комбинат, на которую настроен дешифратор 5, íà его выходе появляется импульс фазового пуска и одновременно триггер 10 фазирования устанавливается в нулевое состояние и элементы И 7, И 17 закрываются.

Технико-экономический эффект от применения предлагаемого устройства заключается в повышении помехозапппценности выделения синхросигнала, чем увеличивается вероятность вхождения в синхро низм и сокращается время синхронизации систем связи.

Формула изобретения

Устройство цикловой синхронизации, содержащее первый сумматор по модулю два, выход которого подключен к входу регистра сдвига с обратной связью и первому входу второго сумматора по модулю два, к второму входу которого, а также к первому входу третьего сумматора по модулю два подключен первый выход регистра сдвига с обратной связью, остальные выходы которого подключены к входам дешифратора, к соответствующему входу которого подключен выход счетчи— ка временных интервалов, первый вход которого объединен с тактовым входом делителя частоты, а к остальным входам счетчика временных интервалов подклкьчен выход второго сумматора по модулю два, при этом второй вход третьего сумматора по модулю два объединен с первым входом первого сумматора по модулю два, к второму входу которого под— ключен выход первого элемента И, а выход третьего сумматора по модулю два подключен к первым входам первого и второго элемента И, причем к второму входу первого элемента И подключен выход триггера фазирования, первый вход которого объединен с первым входом триггера интервалов и входом делителя частоты, выход которого подключен к вторсму входу триггера интервалов, прямой и

7 9441 инверсный выходы которого подключены . соответственно к блокирующему входу делителя частоты и второму входу вто— рого элемента И, выход которого подклк чен к третьему входу триггера интервалов и второму входу триггера фазирования, отличающеесятем, что, с целью повышения помехозащищенности,введены последовательно соединенные линия задержки, третий элемент И и:, 10 дополнительный сумматор по модулю два, к второму входу которого подключен выход уъro разряда регистра сдвига с обратной связью, к входу (И+1)-го разI

37 8

Ряда которого подключен выход дополнительного сумматора по модулю два, а выход третьего сумматора по модулю два подключен к входу линии задержки и второму входу третьего элемента И, к третьему входу которого подключен выход триггера фазирования, к TÐe» му входу которого подключен выход дешифратора.

И сточники информации, принтяые во внимание при экспертизе

1. Авторское свидетельство СССР

% 640439, кл. Н 04 Ь 7/08, 1976 (прототип).

ВНИИПИ Заказ 5158/77 Тираж 688 Подписное филиал ППП "Патент"; г. Ужгород, ул. Проектная, 4