Многоканальный анализатор рекуррентного сигнала фазового пуска

Иллюстрации

Показать всеРеферат

ОП ИСАЙИ Е

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВМДЕТЕЛЬСТВУ

Союз Советски и

Социаиистическкк

Вес убп пц944138 (61) Дополкительное н авт. свид-ву (22}Заявлено 21.02,80(2! ) 2886094/18-09 с присоединением заявки М (23) Приоритет(5! )М. Кл.

Н 04 4 7/10 авщдэротекииый комитет

COCP ио делам изобретений и открытий

Опублиноваио 15.07.82. Бюллетень М 26 (53) УДК 621-394. .662(088.8}

Дата ояубликоваиия описания 15.07.82

Г.N. Вагина (72} Автор .. изобретения (7) ) Заявитель (54) МНОГОКАНАЛЬНЫЙ АНАЛИЗАТОР РЕКУРРЕНТНОГО

СИГНАЛА ФАЗОВОГО ПУСКА

Изобретение относится к связи и может быть использовано в аппаратуре системы передачи данных для синхронизация рекуррентными последовательностями прн приеме информации по Й каналам с временным разделением каналов на различных

5 скоростях (например, 1,2; 2,4, 4,8. 9, 6 кГц).

Известен анализатор рекуррентного . сигнала фазового пуска содержащий после. о довательно соединенные анализатор ошибок, блок памяти и коммутатор, к второ».му входу которого подключен выход первого блока сравнения и первый вход второго блока сравнения, второй вход которого объединен с третьим входом коммутатора и является информационным входом устройства (1).

Недостатком данного анализатора является его применение только в однока- 20 нальных системах с фиксированной скоростью. В устройстве присутствует шина тактовых импульсов с одной фиксированной скоростью, равной скорости приттима.

2 мой информации, в результате чего шраничивается применяемость известного анализатора. Дпя применения в многоканальных системах потребовалось бы количество известных анализаторов, рваное количеству каналов.

Бель изобретения - сокращение вре- i меня анализа рекуррентного сигнала.

Поставленная цель достигается тем, что в многоканальный анализатор рекуррентного сигнала фазового пуска, содержащий последовательно соединенные анализатор орщбок блок памяти и комму твтор, к второму входу которого подклк ; чен выход первого блока сравнения и

Первый вход второго блока сравнения, второй вход которого обьединен с третьим входом коммутатора, и является информа ционным входом устройства, введены последовательно соединенные первый формирователь рекуррентной последователь- . ности (РП), первый элемент И и второй элемент И и последовательно соединенные второй формирователь РП и третий алв3 94413 мент И, а также дополнительный блок сравнения, к входам которого подключены соответствующие выходы второго фор мирователя РП, а выход дополнительного блока сравнения подключен к первому s входу второго формирователя РП, к второму входу которого подключен выход второго блока сравнения и первый вход анализатора ошибок, к второму входу которого подключен третий вход второго,10 формирователя РП, второй вход блока памяти и первый вход первого формировате— ля РП, являющийся входом считывания устройства, к второму входу которого, явля. ющемуся входом запись устройства, под- is ключены четвертый вход второго формирователя РП и третьи входы блока памяти и анализатора ошибок, к четвертым входам которых подключен выход третьего элемента И, при этом к входам первого ?o блока сравнения подключены соответствующие выходы первого формирователя РП, а второй выход анализатора ошибок подключен к второму входу третьего . .элемента И, при этом выход коммутатора под- 2s ключен к третьему входу первого формирователя РП.

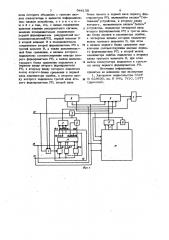

На фиг. 1 представлена с руктурноэлектрическая схема аначизатора, на фиг. 2 — поясняющие его работу эпюры.

Анализатор содержит коммутатор 1, второй блок 2 сравнения, первый блок 3 сравнения, дополнительный блок 4 сравнения, первый элемент И 5, третий эле. мент И 6, второй элемент И 7, блок 8 памяти, анализатор 9 ошибок, первый формирователь 10 рекуррентной последовательности (РП), второй формирователь РП 11, информационный вход 12, вхоц "Считывание" 13, выход 14.1-14К 40 формирователя (РП) 10, вход "Запись" 15 формирователь (РП) состоит из блоков 16.1-16 М памяти и регистра 17. !

Устройство работает следующим обра45 зом.

Входная информация (фиг. 2 f) с R каналов, поступающая через коммутатор 1 с входа 12 записывается сигналом запись (фиг. 2е) в блок 16.1 памяти фор50 мирователя 10 по соответствующим адресам (фиг. 2 а, в - с R ). В следующем цикле (работа с теми же канала» ми) информация из блока 16,1 памяти

-записывается последовательно в регистр

17 сигналом "Считывание" (фиг. 2 ), а сигналом" Зались" (фиг. 2 С), осуществляется перезапись информации из регистра

17 в последующий блок 16.2 памяти, 8 4 причем в блок 16.1 памяти тем же сигналом будет записан следующий бит входной информации, по адресам а, в — с R ) и т. д. (фиг. 2) до блока 16 4 памяти включительно. То есть предыдущая информация из блока памяти 16.1, 16,2, 16Н с каждым циклом по адресам а, в, с я (фиг. 2) записывается последовательно в регистр 17 сигналом "Считывание" (фиг. 28) по входу 13, а сигналом "Запись (фиг. 28) по входу 12 с выходов

14.1, 14,2, 14.И -l регистра 17 производится перезапись в блоки памяти 16.2—

l6 К соответственно. Таким образом, происходит заполнение формирователя 10 входной информацией по Й каналам.

Одновременно на блоке 2 сравнения по каждому из адресов а, в — с Р (фиг. 2) происходит сравнение побитно входной информации (фиг. 2 Х ) с входа 12 с информацией, находящейся в формирователе

РП 10, и преобразованной в рекуррентную последовательность через блок 3 сравнения, которая не совпадает с вход— ной информацией. Следовательно, на выходе блока 2 сравнения присутствуют сигналы несовпадения.

После заполнения входной информации (фиг. 2 4) формирователя РП 10, с выхода блока 3 сравнения выдается рекуррентная последовательность, аналогичная входной.

При совпадении входной информации с информацией блока 3 сравнения на заданном участке, на выходе блока сравнэ. ия 2 отсутствуют сигналы несовпадения.

Через определеннь1й промежуток времени выход блока 3 сравнения подключается через коммутатор 1 на вход формирователя РП 10, а блок 2 сравнения в этом случае осуществляет побитное сравнение входной информации .(фиг. 2 f) с рекуррентной последовательностью, с блока 3 сравнения.

Формирователь РП 1 1 начинает перебор своей рекуррентной последовательности при отсутствии сигналов несовпадения через блок 4 сравнения индивидуально по каждому из адресов а, в— с К (фиг. 2).

Если входная информация по определенным каналам имеет опережение или запаздывание относительно других каналов, то вхождение в синхронизм и начало работы формирователя РП 11 идет с опережением и запаздыванием по соответствующим каналам.

Конец рекуррентных последовательностей формирователя РП 11 по каждому

5 9441 из R каналов дешифруется элементом

И б„исходя из заданной длительности г неискаженного участка входной рекуррентной последовательности. С выхода

I элемента И 6 сигналы конца рекурренты устанавливают в исходное состояние анализатор 9 ошибок М по соответствующим адресам переключают ячейки в блоке 8 памяти.

По сигналам с выхода блока 8 памяти 10 через коммутатор 1 рекуррентная последовательность с блока 3 сравнения записывается в блок 16.1 памяти и работа происходит аналогично записи входной информации. !

Следовательно, формирователь РП 10 совместно с блоком 3 сравнения через коммутатор 1 формирует R рекуррентных последовательностей по R каналам, автономно по каждому каналу с одним из адресов, а, в — с (Т), а, в — с (II) и т. д. (фиг. 2).

Блок 2 сравнения при подключении выхода блока 3 сравнения через коммутатор 1 на вход формирователя РП 10 осуществляет побитное сравнение входной информации (фиг. 2 f.) с рекуррентными последовательностями из формирователя

РП 10 и.блока 3 сравнения.

Конец фазового пуска формирователя

РП 10 по каждому из R каналов дешифри,руется элементом И 5 и выдается через элемент И 7 на выход соответственно адресам а, в — с R (фиг. 2).

В случае вхождения в синхронизм с M аналогичной рекуррентной последоваельностью ненужной радиостанции на выходе блока 2 сравнения присутствуют сигналы несовпадения по данному каналу, которые фиксируются анализатором 9 ошибок. 40

При определе.-.юй последовательности сигналов несовпадения анализатор 9 ошибок по данному каналу выдает сигнал на вход блока 8 памяти. Вход формирователя РП 10 через коммутатор 1 подклю- 4s чается к информационному входу 12. С выхода анализатора 9 ошибок по данному каналу выдается сигнал на второй вход элсмента И 7 для блокировки выхода фазового пуска. 50

В исходное положение устройство устанавливается по сигBBJIBM несовпадения с блока 2 сравнения. Поэтому если на выходе 12 рекуррентная последовательность отличается от рекуррентной последователь-55 ности, формируемой на выходе блока 3 сравнения, то на выходе блока 2 сравнения присутствуют сигналы несовпадения, 38 6 причем в анализаторе 9 ошибок происходит анализ количества несовпадения и их последовательности и, если входная рекуррента отлична от формируемой, проис>. ходит переключение входа 12 устройства на вход формирователя РП 10 через коммутатор 1.

Когда на информационный вход 12 поступает информация по одному или Я каналов, блок 2 сравнения выдает. сигналы несовпадения по соответствующим каналам, так как формирователь РП 10 находится в нулевом состоянии (предыдущая информация состояла из нулей). ,Сигналы несовпадения устанавливают формирователь РП 11 в исходное состояние, и одновременно они подсчитываются в анализаторе 9 ошибок. Последний фиксирует смену входной рекуррентной после довательности и выдает в блок 8 памяти, который подключает информационный вход

12 через коммутатор 1 к входу формирователя РП 10.

На вход 1 3 устройства подаются сигналы считывания (фиг. 2 d ), a к входу

15 подводятся разряды адреса а, в — с и сигналы записи (фиг. 2 В ), которые формируются с частотной, равной принимаемой информации. Возможное количество обрабатываемых каналов зависит от выбранной длительности на один канал.

В предлагаемом устройстве полностью реализуется функции известных анализаторов, кроме того, с введением многоканальных формирователей появилась возможность увеличить количество рабочих каналов от одного до 64-128, причем рекуррентная последовательность формируется индивидуально по каждоМу каналу и зависит только от входной информации.

Каждый канал имеет фиксированное время работы, которое определяется адресом на данный канал. Также имеется возможность работы на разных скоростях (1,2 кГц-9,6 кЫ), это достигается при . определенно сформированном сигнале запись, соответствующем частоте принимаемой информации.

Формула изобретения

М ногоканальжтй анализатор рекуррент ного сигщцщ фазового пуска, содержащий последовательно соединенные анализатор ошибок, блсж памяти и коммутатор, к второму входу которого подключен выход первого блока сравнения и первый вход второго блока сравнения, второй.

7 0441 вход которого объедииен с третьим входом коммутатора и является информационным входом устройства, о т л и ч а юш и и с,.я тем, что, с целью сокращения

speMeRK анализа рекуррентного сигнала, 3 введены последовательно соединенные первый формирователь рекуррентной по. следовательности(РП), первый элемент И и второй элемент И и последовательно . соединенные второй формирователь РП и 10 третий элемент И, а также дополнитель-. ный блок сравнения, к входам которого подключены соответствующие выходы второго формирователя РП, а выход дополнительного блока сравнения подключен к 1 первому в1соду второго формирователя

РП, к второму входу которого подключен выход второго блока сравнения и первый вход, анализатора ошибок, к второму входу которого подключен третий вход вто- zо рого формирователя РП, второй вход

Й8 8 блока памяти и первый вход первого формирователя РП, являющийся входом Считывание устройства, к второму входу

g/ которого, являющемуся входом Запись устройства, подключен четвертый вход второго формирователя РП и третьи входы блока памяти и анализатора ошибок, к четвертым входам которых подключен выход третьего элемента И, при этом к входам первого блока сравнения подключены соответствующе выходы первого формирователя РП, а второй выход анализатора ошибок подключен к второму входу третьего элемента И, при этом выход коммутатора подключен к третьему входу первого формирователя РП.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР

М 628630, кл. Н 04 7/10, 1977 (прототип) .

М4138

Составитель Т. Поддубняк

Редактор H. Воловик Техред М.Гергель <орректор У., Пономаренко

Заказ 51 8/77 Тираж 688 Подписное

БНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4