Устройство для контроля искажений типа "преобладание телеграфных сигналов

Иллюстрации

Показать всеРеферат

Союз Советскин

Социалистически»

Республик

ОПИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ()944139 (61) Дополнительное к авт. свид-ву (22) Заявлено 24.12,80 (21) 3222781/1 8-09 (51) М. Кл. с присоединением заявки МН 04 1 11/08 тнеуйарстеенный квинтет

СССР (23) Приоритет

No делан иаебретеннй н открыт»»

Опубликовано 1 5.07.82. Бюллетень J@ 26

Дата опубликования описания 15.07.82 (53) УЯK 621.394..664(088.8) Г. М. Лукашев, E. Н. Nopoaos и В. Я. Пешков (72) Авторы изобретения (71) Заявитель (54) УСТРОЙСТВО ДЛЯ -КОНТРОЛЯ ИСКАЖЕНИЙ

ТИПА ПРЕОБЛАДАНИЕ ТЕЛЕГРАФНЫХ

СИГНАЛОВ

Изобретение относится к радиотехнике и может использоваться в устройствах приема сигналов частотной телеграфии и поиском по частоте для анализа пра— вильности захвата сигнала по допустимой

5 величине преобладаний демодулированного сигнала.

Известно устройство для контроля искажений типа преобладание телеграфных сигналов, содержашее первый и второй блоки сравнения, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ (11.

Однако данное устройство для анализа симметриии информационного сигнала в аналоговом виде содержит датчик опорного сигнала, задаюший пороги срабатывания измерительных устройств, кроме того, уровень входного сигнала должен быть постоянным. ю

Бель изобретения - повышение точнос ти контроля при переменном уровне телег рафных сигналов.

Поставленная пель достигается тем, что в устройство для контроля искажений типа преобладания телеграфных сигналов, содержашее первый и второй блоки срав нення, выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, введены амплитудный детектор, первый и второй интеграторы и первый и второй ключи, при этом первый выход амплитудного детектора, вход хоторого является сигнальным входом устройства, соединен с первым входом первого интегратора, второй вход которого и первый вход второго интегратора соединены с вторым выходом амплитудного де- тектора, первый выход которого соединен с вторым входом второго интегратора, третий и четвертый входы первого интегратора соединены соответственно с первым и вторым выводами первого ключа, управляющий вход которого, объединенный с управляюшмм входом второго ключа, является управляюшим входом устройства, третий и четвертый входы второго интег3 9441 ратора соединена соответственно с первым и вторым выводами второго ключа, выход первого интегратора соединен с инвертирующим входом первого блока сравнения, выход второго Интегратора сое- 5 динен с инвертирующим входом второго блока сравнения,,а неинвертирующий вход первого блока сравнения и инвертирующий вход второго блока сравнения соединены с общей шиной устройства.

1О

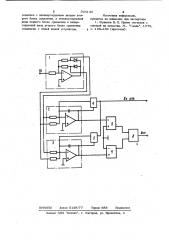

На чертеже приведена структурная, схема устройства, Устройство содержит амплитудный детектор 1, два интегратора 2 и 3, два ключа.4, 5, два блока 6 и 7 сравнения и элемент 8 ИЛИ.

Устройство рабо"ает следующим образом.

Информационный сигнал в аналоговом виде поступает на вход амплитудного детектора 1, с первого выхода которогс отрицательные посылки поступают на перabfA вход интегратора 2 и на второй вход интегратора 3, а положительные посылки со второго выхода поступают на второй вход интегратора 2 и на первый вход интегратора 3, причем отношение сопротивления резистора по цепи прохождения положительных посылок к сопротивлению резистора по цепи прохождения отрицательных посылок равно Н для интегратора 2 и отношение сопротивления резистора по цепи прохождения отрицательных посылок к сопротивлению резистора по цели прохождения положительных посылок равно тоже Я для интегратора 3.

Y, — больше или равно единице.

Число М указывает, во сколько раз плошадь отрицательных посылок может превышать площадь положительных посылок.

40 или наоборот и выбирается, исходя из допустимой величины преоблада ний.

Первый ключ 4 и второй ключ 5 размыкаются при поступлении на их входы управляющего сигнала.

Если за время анализа сумма площа45 ,дей положительных посылок не превышает больше чем в Й раз сумму площадей отрицательных посылок и если сумма плошадей отрицательных посылок не превышает более, чем в Й раз сумму площадей положительных посылок, то на выходе интегратора 2 будет положительное напряжение, а на выходе интегратора 3— отрицательное, которое поступают на входы блока 6 и блока 7, на выходах ко- 55 торых будут логические нули, которые ! поступают на входы элемента ИЛИ 8, с выхода которого выдается сигнал, указы39 4 вающий на то, что величина преобладания в допуске

При отношении суммъ площадей отрицательных и положительных посылок, превышающем значение М, на выходе одного из измерительных устройств появится логическая единица и на выходе элемента ИЛИ 8 появляется сигнал, указываю щий на то, что величина преобладания не в допуске.

При окончании входного управляющего сигнала ключи 4 и 5 замыкаются. Qmгельность управляющего сигнала выбирается исходя из необходимого времени усреднения, которое определяется скоростью телеграфирования.

Благодаря измерению соотношения площадей отрицательных и положительных посылок сигнала, исчезает необходимость использования датчика опорного сигнала, задающего пороги на измерительные устройства, и устройство может стабильно работать при изменении уровня входного сигнала.

Формула изобретения

Устройство для контроля искажений типа преобладание телеграфных сигналов, содержащее первый и второй блоки сравнения, выходы которых соединены соответственно с первым и вторым входами .элемента ИЛИ, отличающееся тем, что, с целью повышения точности контроля при переменном уровне телеграфных си налов, введены амплитудный детектор, первый и второй интеграторы и первый и второй ключи, при этом первый выход амплитудного детектора, вход которого является сигнальным входом устройства, соединен с первым входом первого интегратора, второй вход которого и первый вход второго интегратора соединены с вторым выходом амплитудного детектора, первый выход которого соединен с вторым входом второго интегратора, третий и четвертый входы первого интегратора соединены соответственно с первым и вторым выводами первого ключа, управляющий вход которого, объединенный с управляющим входом второго ключа, является управляющим входом устройства, третий и четвертый входы второго интегратора соединены соответственно с первым и вторым выводами второго ключа, выход первого интегратора соединен с инвентирующим входом первого блока сравнения, выход второго интегратора

5 944 соединен с неинвертирующим входом вто рого блока сравнения, а неинвертирующий вход первого блока сравнения, и инвертирующий вход второго блока сравнения соединены с общей шиной. устройства.

139 6

Источники информации, принятые во внимание при акспертиэе

1. Шувалов В. П. Прием сигналов с оценкой их качества. М., Связь", 1979, с. 188-189 (прототип).

ВКИИПИ 3аказ 5158/77 Тираж 688 ..Подписное филиал ППП Патент", r. Ужгород, ул. Проектная, 4